# ION-INDUCED SINGLE-EVENT BURNOUT MECHANISMS IN SIC POWER MOSFETS AND DIODES

By

Dennis R. Ball, II

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

### DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

June 30, 2020

Nashville, Tennessee

Approved:

Kenneth F. Galloway, Ph.D.Ronald D. Schrimpf, Ph.D.Arthur F. Witulski, Ph.D.

Michael L. Alles, Ph.D.

Joshua D. Caldwell, Ph.D.

© Copyright by Dennis R. Ball, II 2020

All Rights Reserved

# DEDICATION

This dissertation is dedicated to my wife, Andrea, and sons, Easton, Rowan, and Landon.

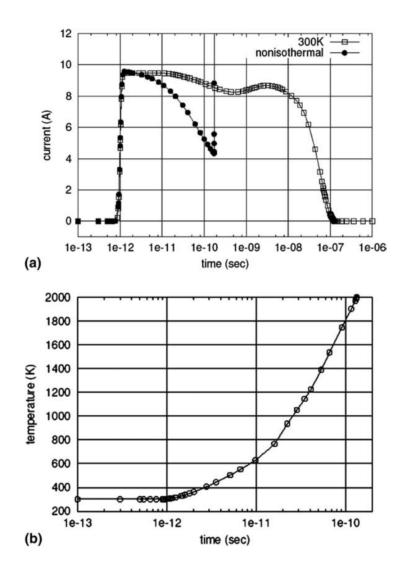

#### ACKNOWLEDGEMENTS

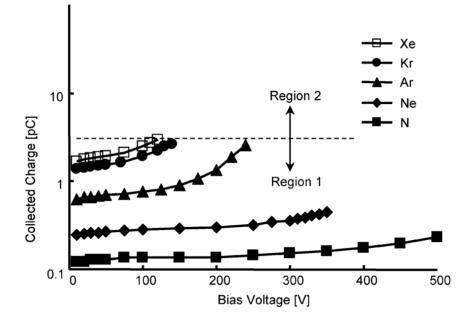

The body of research detailed in this dissertation would not have been possible without the support of NASA, through the Early Stage Innovations (ESI) program and managed by Goddard Space Flight Center. Additional acknowledgment goes to the University Programs of Synopsys, Inc. for providing access to Technology Computer-Aided Design (TCAD) tools used in this research.

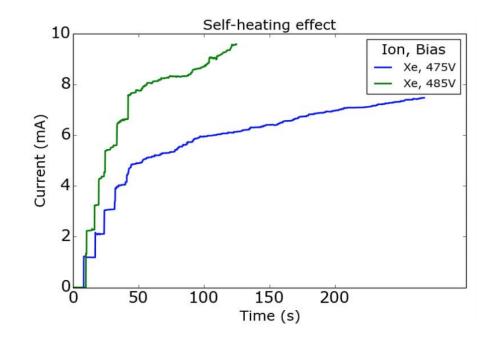

I would like to express my thanks and appreciation to my committee members for their support and enthusiasm for the research detailed in this dissertation. Dr. Ken Galloway and I were discussing my career several years ago and the possibility of pursuing a doctorate came up, and after a few minutes he looked at me and said "Well, Scooter...why not." For those that know him, you will understand why there is a period and not a question mark at the end of that quote! Dr. Galloway's encouragement and guidance have been invaluable during this research. Even more importantly, I am thankful that he has such a positive attitude and spirit. A special thank you goes to Dr. Ron Schrimpf, who is primarily responsible for my being at Vanderbilt/ISDE in the first place, and has been a mentor for the entirety of my career. Dr. Mike Alles has also been a great advisor, not only for his participation in this program, but also for the guidance that he has given me through the years. I have been extremely fortunate to have benefited directly from his interests in just about anything related to radiation in a semiconductor device, and so very much of my career has been working with him on so many different projects. Dr. Art Witulski's patience and ability to step away from his desk and pick up a pen and walk through a calculation or brainstorm an idea has been extremely helpful. I am very grateful to Dr. Josh Caldwell and his support of my research, and his willingness to be a part of this team and my committee.

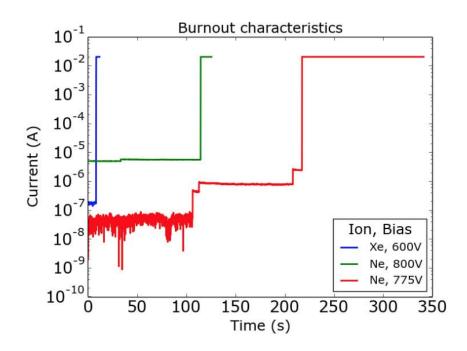

I am also very appreciative of the support and effort of the team that worked together as part of this research program. Dr. Robert Reed, Dr. Andrew Sternberg, Dr. John Hutson, Dr. Jean-Marie Lauenstein, Dr. Arto Javanainen, and Robert Johnson have been instrumental in discussions about pretty much every facet of this research. There is no "I" in "team", and while this work is my own, there is a tremendously collaborative effort among my entire committee and the other members of this research team, and I would not have gotten to this point without them.

I would also like to express my gratitude to VU RER faculty, Dr. Lloyd Massengill, Dr. Bharat Bhuva, Dr. Tim Holman, Dr. Dan Fleetwood, Dr. Jeff Kauppila, and Dr. Brian Sierawski. I have been extremely fortunate to have worked with each of them on a wide range of programs over my career as an engineer at ISDE. While this disseration is focused on one specific research area, I feel that my entire basis of knowledge is much more broad, and stems from having worked with these faculty members over the years.

I am thankful for my colleagues and co-workers at the Institute for Space and Defense Electronics. Dr. Kevin Warren, Tim Haeffner, and Mike McCurdy have all contributed to my research in some manner. I have always thought it important to understand my limitations, and being part of a team that can pretty much do anything is highly rewarding.

I am also deeply grateful to my wife, Andrea, and my sons, Easton, Rowan, and Landon. Let's face it, they are the best part of my life, and every day with my family is such an adventure.

# TABLE OF CONTENTS

| DEDI                | CATION                                                                                | iii                                                |  |  |

|---------------------|---------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| ACKNOWLEDGEMENTS in |                                                                                       |                                                    |  |  |

| LIST                | OF TABLES                                                                             | viii                                               |  |  |

| LIST                | OF FIGURES                                                                            | ix                                                 |  |  |

| Chap                | ter                                                                                   |                                                    |  |  |

| I.                  | INTRODUCTION                                                                          | 1                                                  |  |  |

| II.                 | POWER DEVICE STRUCTURE AND OPERATION                                                  | 6                                                  |  |  |

|                     | Power Device Structure                                                                | 6<br>10                                            |  |  |

| III.                | 3D TCAD MODEL DEVELOPMENT                                                             | 12                                                 |  |  |

|                     | Physical Device Design                                                                | 13<br>16                                           |  |  |

| IV.                 | RADIATION-INDUCED SINGLE-EVENT EFFECTS BACKGROUND                                     | 25                                                 |  |  |

|                     | Space Radiation Environment                                                           | 28<br>30<br>34<br>38<br>39<br>39<br>43<br>45<br>48 |  |  |

| V.                  | IDENTIFYING COMMON TRENDS FOR SINGLE-EVENT BURNOUT<br>IN SIC POWER MOSFETS AND DIODES | 50                                                 |  |  |

|                     | 1200 V SiC                                                                            | 51<br>57                                           |  |  |

| VI.                 | ION-INDUCED ENERGY PULSE MECHANISM                                                    | 61                                                 |  |  |

|       | Resistive Shunt Effects                                                          | 61<br>72<br>75<br>78 |

|-------|----------------------------------------------------------------------------------|----------------------|

| VII.  | EVALUATION OF DEVICE VARIANTS                                                    | 83                   |

|       | MOSFET Device Variants - Epitaxial Design                                        | 84<br>86             |

| VIII. | MITIGATING SINGLE-EVENT BURNOUT THROUGH DEVICE SE-<br>LECTION AND CIRCUIT DESIGN | 93                   |

|       | Silicon vs. SiC                                                                  | 94<br>97<br>97<br>99 |

| IX.   | IMPACT AND CONCLUSIONS                                                           | 102                  |

| REFE  | ERENCES                                                                          | 106                  |

| Apper | ndix                                                                             |                      |

| А.    | POSITIVE FEEDBACK LOOP: PARASITIC BJT AND IMPACT IONIZATION                      | 113                  |

|       | Parasitic BJT                                                                    | 114<br>118           |

| В.    | NEUTRON-INDUCED SECONDARY PARTICLE GENERATION                                    | 127                  |

# LIST OF TABLES

| Table |                                                                                                                                                                                                                                                                                   | Page |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.    | Comparison of on-state resistance and rated current for two commercially available power MOSFETs, one silicon and one SiC [12], [13]                                                                                                                                              | 8    |

| 2.    | Electrical property comparison of Silicon and SiC after Choi <i>et al.</i> [14]                                                                                                                                                                                                   | 9    |

| 3.    | Parameters Used in TCAD Simulations for MOSFETs and Diodes                                                                                                                                                                                                                        | 14   |

| 4.    | Measured degradation and catastrophic failure regions for SiC power<br>MOSFETs after Lauenstein <i>et al.</i> [6]                                                                                                                                                                 | 43   |

| 5.    | Ion Beam Characteristics with $SEB_{TH}$ shown $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                               | 53   |

| 6.    | TCAD-simulated maximum lattice temperature as a function of device bias and particle LET                                                                                                                                                                                          | 78   |

| 7.    | 3D TCAD-simulated maximum lattice temperature as a function of ion strike location for ion LET (in MeV-cm <sup>2</sup> /mg) and bias consistent with the single-event burnout threshold for 1200 V SiC JBS diode and SiC MOSFET. DNC indicates a simulation that Did Not Converge | 81   |

| 8.    | 3D TCAD Simulation Results Indicating Positive Feedback as a function of Ion Strike Location, LET, and Bias                                                                                                                                                                       | 126  |

# LIST OF FIGURES

| Page | 'e                                                                                                                                                                                                                                                                           | Figure |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

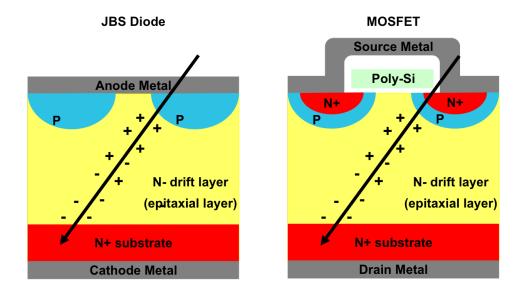

| 7    | Typical cross-sections for planar, vertical power junction-barrier Schot-<br>tky diode and power MOSFET                                                                                                                                                                      | 1.     |

| 8    | Typical cross-section of a power MOSFET defining resistive paths through the device after Havanur <i>et al.</i> [11]                                                                                                                                                         | 2.     |

|      | Electric field concept comparison of silicon and SiC as a function of distance, $W_n$ . The area under each field curve is the junction voltage, which is equal in this example $\ldots \ldots \ldots$ | 3.     |

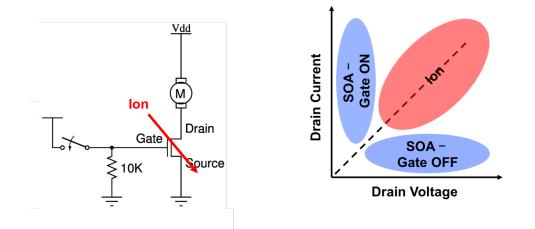

|      | Conceptual example of a power MOSFET being used as a switch to drive<br>a load (left) and the safe-operating area (SOA) (right). An actual circuit<br>will also have a diode from drain to ground for inductive current flow<br>when the transistor is OFF                   | 4.     |

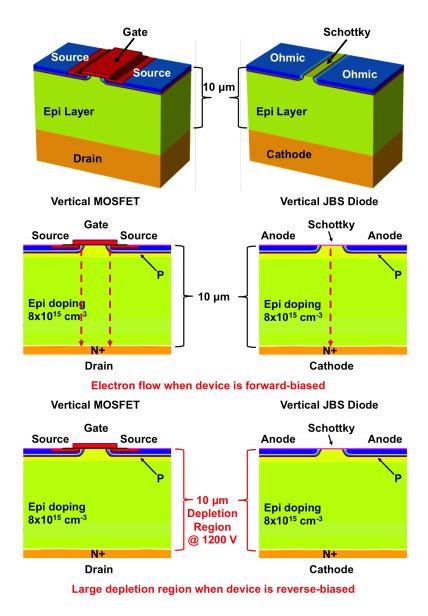

| 15   | 3D TCAD model of a 1200 V SiC power MOSFET (top left) and JBS diode (top right) showing device structure (epi doping/depth). 2D-cutplanes indicating current flow in forward operation (middle) and fully-depleted epitaxial region at 1200 V (bottom)                       | 5.     |

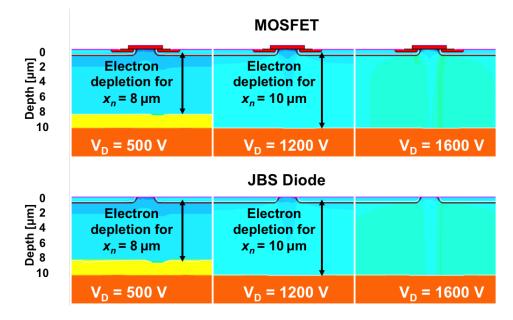

| 18   | 2D-cutplanes of the electron density for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V $\ldots$                                                                                                                                                    | 6.     |

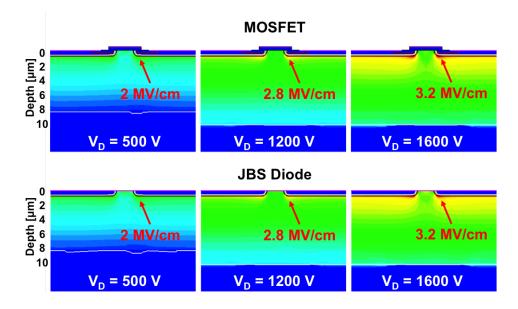

|      | 2D-cutplanes of the internal electric field for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V $\ldots$                                                                                                                                             | 7.     |

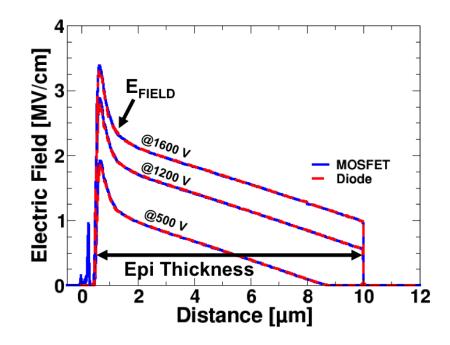

| 20   | 1D-cutlines of the internal electric field for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V $\ldots$                                                                                                                                              | 8.     |

| 21   | 2D-cutplanes of the internal electrostatic potential for both the MOS-FET and the diode, when biased at 500 V, 1200 V, and 1600 V $\ldots$                                                                                                                                   | 9.     |

| 21   | 1D-cutlines of the internal electrostatic potential for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V $\ldots$                                                                                                                                     | 10.    |

|      | 3D TCAD-simulated electrical avalanche breakdown as a function of reverse bias for 1200 V SiC power MOSFET and diode                                                                                                                                                         | 11.    |

|      | 3D TCAD-simulated electrical avalanche breakdown as a function of reverse bias for 1200 V SiC power MOSFET and diode                                                                                                                                                         | 12.    |

| 13. | Example of a power MOSFET in the OFF-state hit by an ion (left), forcing a high-current, high-voltage state that may be non-stable and outside of the SOA                                                                                                                                  | 27 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 14. | Schematic cross-sections for vertical power junction-barrier Schottky diode and power MOSFET indicating electron-hole pairs generated by the passage of a heavy ion                                                                                                                        | 29 |

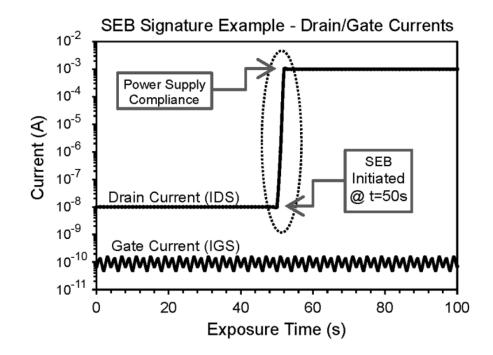

| 15. | Example of SEB during heavy ion irradiation of a power MOSFET.<br>Sudden drain current increase indicates drain-to-source short circuit after<br>Titus <i>et al.</i> [30]                                                                                                                  | 31 |

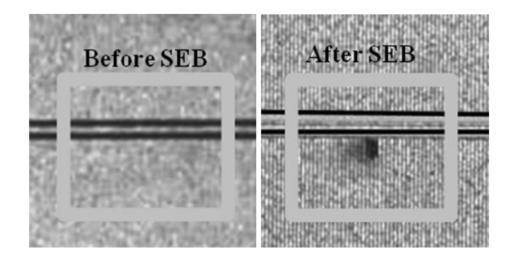

| 16. | Before and after photos of SEB. Visible physical damage is a likely indicator of SEB after Titus <i>et al.</i> [30]                                                                                                                                                                        | 31 |

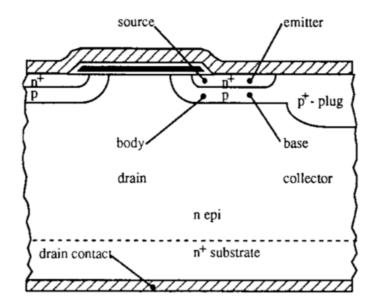

| 17. | Inherent N-P-N parasitic BJT transistor in a vertical DMOS device after Johnson <i>et al.</i> [32]                                                                                                                                                                                         | 32 |

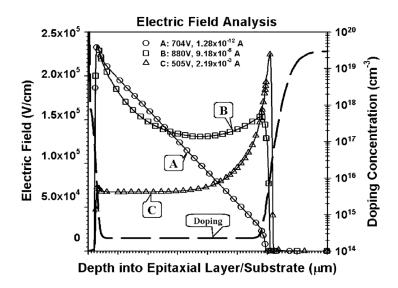

| 18. | Electric field distribution pre-strike (A) and post-strike (B and C) for<br>simulated ion strike in a power MOSFET. A to B to C represents an<br>evolution of the electric field as a function of time after Liu <i>et al.</i> [31]                                                        | 33 |

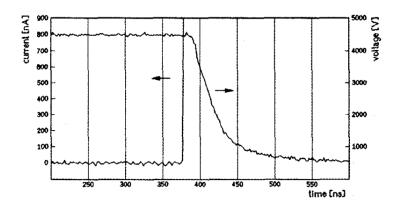

| 19. | Oscilloscope recording of reverse blocking current and voltage during failure. The destructive current develops in less than 10 ns after Kabza <i>et al.</i> [33]                                                                                                                          | 35 |

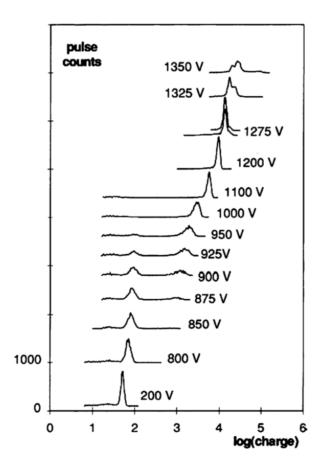

| 20. | Charge spectrum from the bombardment of a 4kV diode with 90 MeV Kr ions showing the number of events as a function of the total generated charge with increasing the applied voltage after Maier <i>et al.</i> [34]                                                                        | 36 |

| 21. | Output currents of isothermal and non-isothermal simulations with LET = $30 \text{ MeV-cm}^2/\text{mg}$ and V = $3500 \text{ V}$ (top), along with maximum temperature due to self-heating (bottom) after Walker <i>et al.</i> [36]                                                        | 37 |

| 22. | Collected charge as a function of reverse bias voltage observed in SiC Schottky diodes after Kuboyama <i>et al.</i> [42]                                                                                                                                                                   | 40 |

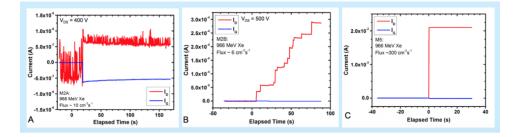

| 23. | Measured diode current versus time during heavy-ion irradiation for two diodes, showing discrete increases in leakage current with individual heavy ions, with self-heating effect. Xenon flux was 68, and Neon was $5.7-6.1 \text{ ions/cm}^2/\text{s}$ after Witulski <i>et al.</i> [18] | 41 |

| 24. | SEB events for three different 1200 V JBS diodes. Xenon flux was 68, and Neon was $5.7-6.1$ ions/cm <sup>2</sup> /s. All diodes are irradiated at room temperature after Witulski <i>et al.</i> [18]                                                                                       | 41 |

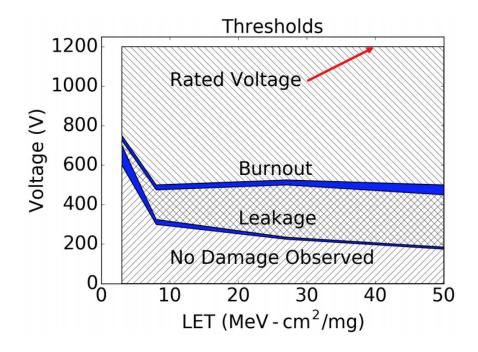

| 25. | Measured degradation mode thresholds as functions of applied bias and LET. The width of the line indicates minimum voltage at which burnout was observed and maximum voltage with no burnout observed after Witulski <i>et al.</i> [18]                  | 42 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 26. | MOSFET drain current as a function of time during irradiation A) No damage, B) Leakage current degradation, and C) Catastrophic failure after Lauenstein <i>et al.</i> [6]                                                                               | 44 |

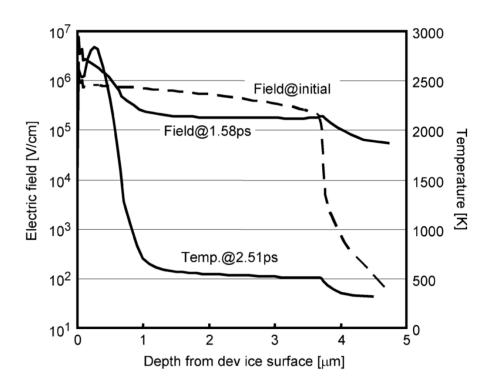

| 27. | Electric field and temperature distribution along ion track after Kr ion strike under 220 V of reverse bias after Kuboyama <i>et al.</i> [42] $\ldots$ .                                                                                                 | 47 |

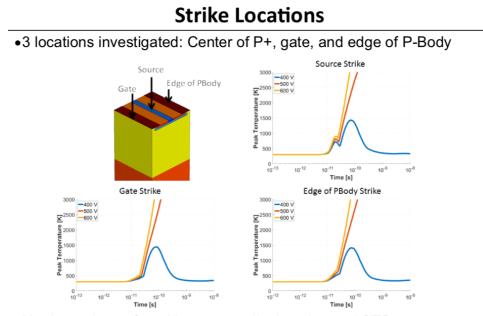

| 28. | 3D TCAD simulations of ion-induced temperature increase in SiC power<br>MOSFET for LET = 46 MeV-cm <sup>2</sup> /mg varying bias and hit location after<br>McPherson <i>et al.</i> [48]                                                                  | 47 |

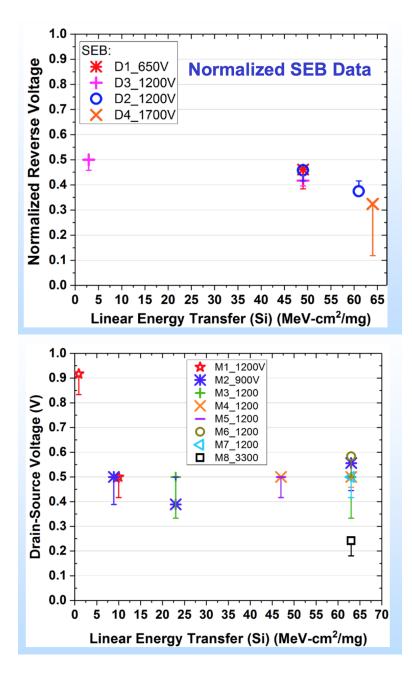

| 29. | Single-event burnout voltage normalized to rated breakdown voltage as a function of ion LET for SiC Schottky diodes (top) and MOSFETs (bottom) showing that 50% device de-rating is not sufficient for survivability after Lauenstein <i>et al.</i> [45] | 49 |

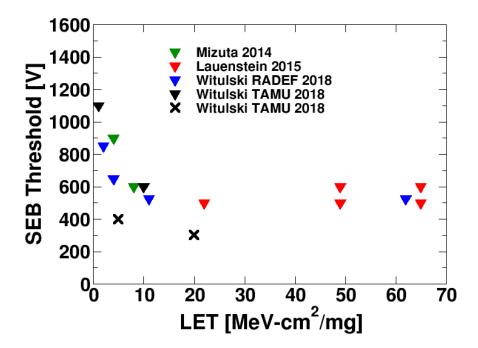

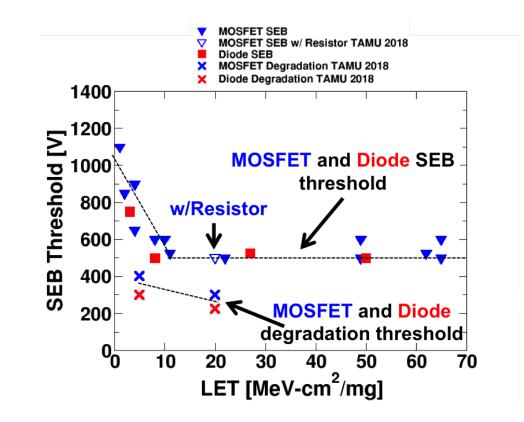

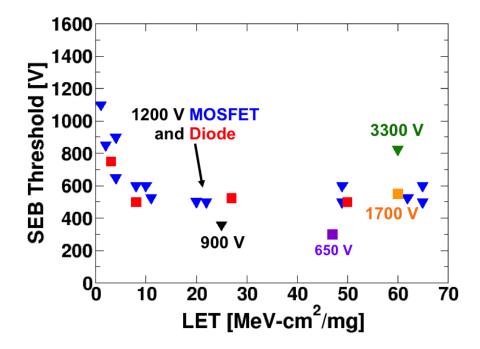

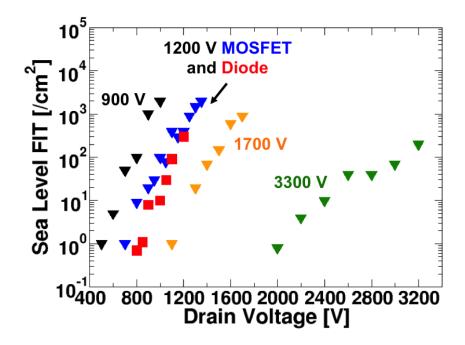

| 30. | Single-event burnout and degradation threshold bias voltages vs. LET for 1200 V SiC power MOSFETs taken during this work and compared to published literature [19], [45], [46], [50]                                                                     | 52 |

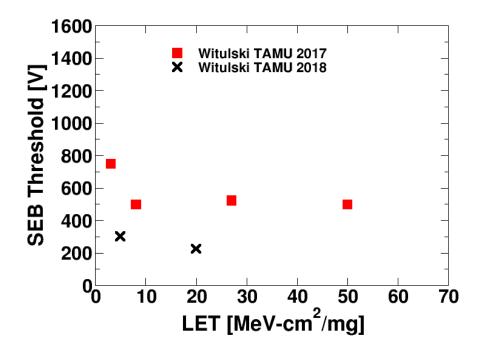

| 31. | Single-event burnout and degradation threshold bias voltages vs. LET for 1200 V SiC power diodes taken during this work and compared to published literature after Witulski <i>et al.</i> [18]                                                           | 53 |

| 32. | Single-event burnout threshold bias voltages vs. LET for 1200 V SiC power MOSFETs and diodes for data taken during this work and compared to published literature [18], [19], [45], [46], [50]                                                           | 56 |

| 33. | Circuit schematic for a non-destructive test technique for silicon power<br>devices with a resistor inline between the power supply and the drain node                                                                                                   | 57 |

| 34. | Single-event burnout threshold bias voltages vs. LET for 1200 V SiC power MOSFETs and diodes [18], [19], [45], [46], [49], [50]                                                                                                                          | 59 |

| 35. | Single-event burnout threshold bias voltages vs. LET for 1200 V SiC power MOSFETs and diodes after Lichtenwalner <i>et al.</i> and Akturk <i>et al.</i> [56], [57]                                                                                       | 60 |

| 36. | 3D TCAD model of a 1200 V SiC power MOSFET (top left) and JBS diode (top right) showing device structure (epi doping/depth). 2D-cutplanes indicating current flow in forward operation (middle) and fully-depleted epitaxial region at 1200 V (bottom)   | 62 |

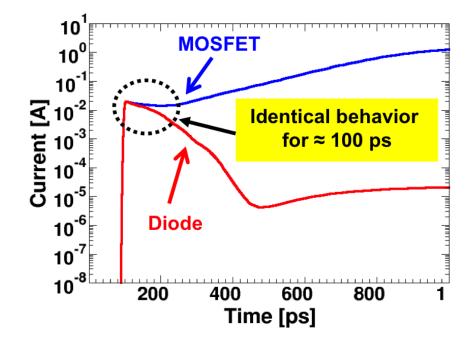

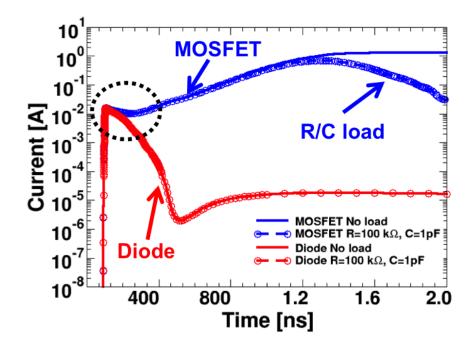

| 37. | Ion-induced current transient for a 1200 V SiC power MOSFET and diode for particle with LET=10 MeV-cm <sup>2</sup> /mg and 500 V drain bias                                                                                                                                                       | 64 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

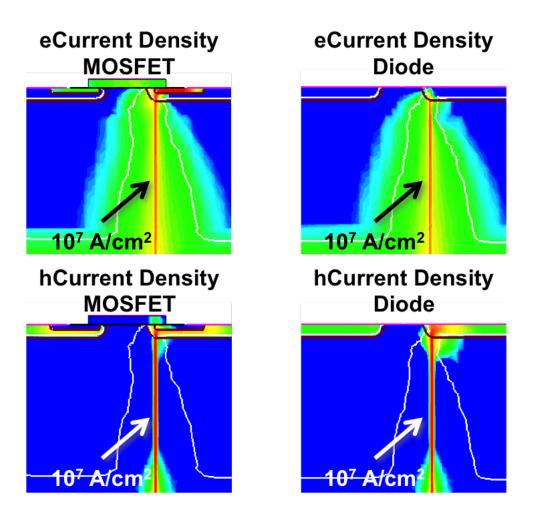

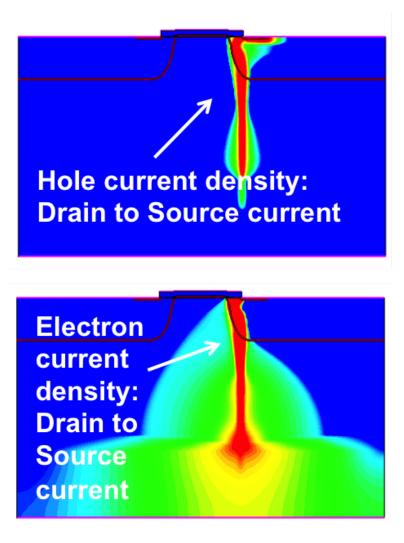

| 38. | 2D-cutplanes in TCAD showing electron and hole current densities exceeding $1 \times 10^7 \text{ A/cm}^2$ for a particle with LET = 10 MeV-cm2/mg with 500 V drain bias. 2D-cutlplanes taken at 5 ps following the ion strike.                                                                    | 65 |

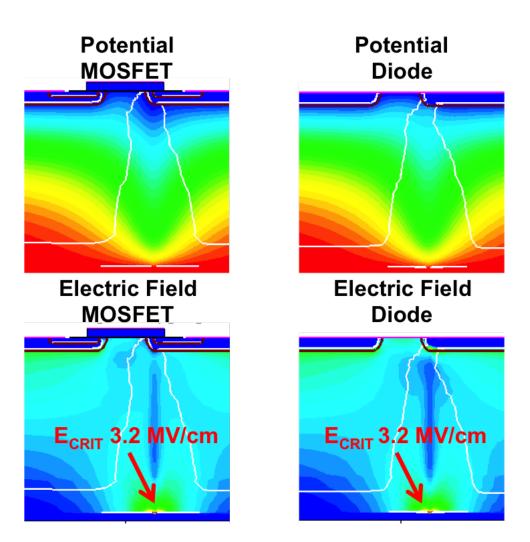

| 39. | 2D-cutplanes in TCAD showing internal electrostatic potential and electric field ino-induced re-distribution, with electric fields exceeding $3.2 \text{ MV/cm}$ for a particle with LET = 10 MeV-cm <sup>2</sup> /mg with 500 V drain bias. 2D-cutlplanes taken at 5 ps following the ion strike | 66 |

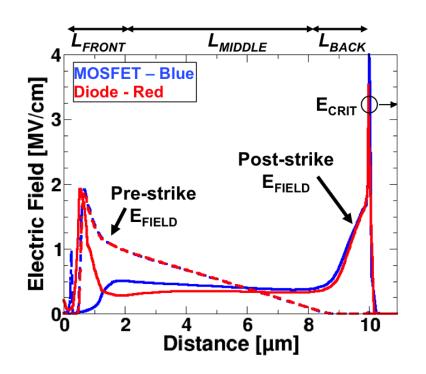

| 40. | 1D-cutline in TCAD showing pre- and post-strike electric fields exceeding $3.2 \text{ MV/cm}$ for a particle with LET = 10 MeV-cm <sup>2</sup> /mg with 500 V drain bias. 1D-cutlines taken at 5 ps following the ion strike                                                                      | 67 |

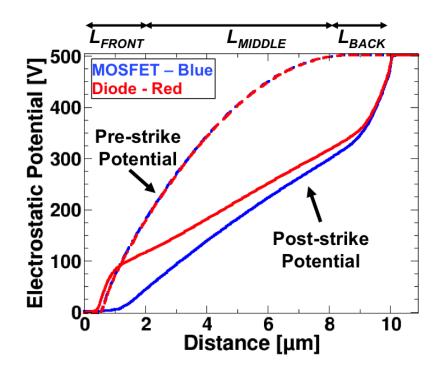

| 41. | 1D-cutline in TCAD showing pre- and post-strike internal electrostatic potential (bottom) for a particle with LET = 10 MeV-cm <sup>2</sup> /mg with 500 V drain bias. 1D-cutlines taken at 5 ps following the ion strike                                                                          | 68 |

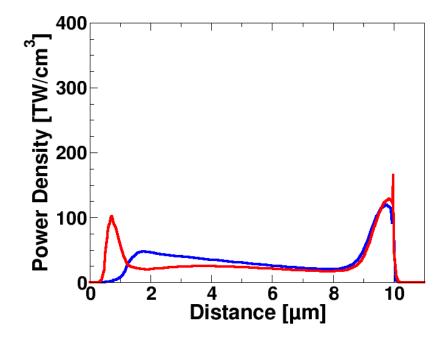

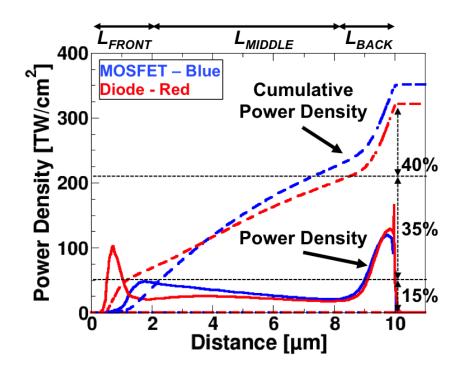

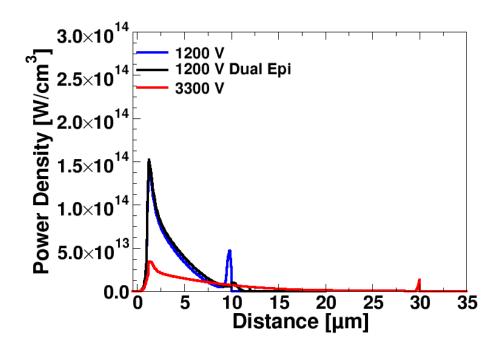

| 42. | 1D-cutline in TCAD showing post-strike power density for a particle with $LET = 10 \text{ MeV-cm}^2/\text{mg}$ with 500 V drain bias. 1D-cutlines taken at 5 ps following the ion strike.                                                                                                         | 70 |

| 43. | 1D-cutline in TCAD showing post-strike cumulative power density for a particle with $LET = 10 \text{ MeV-cm}^2/\text{mg}$ with 500 V drain bias. 1D-cutlines taken at 5 ps following the ion strike.                                                                                              | 71 |

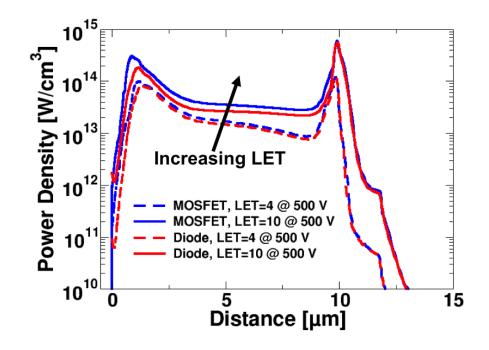

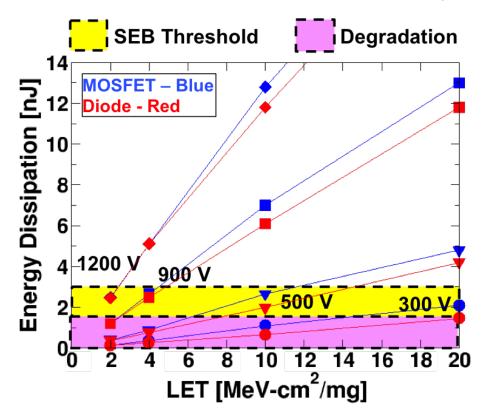

| 44. | 1D-cutline in TCAD showing post-strike power density and cumulative power density for a particle with LET = 4 and 10 MeV-cm <sup>2</sup> /mg with 500 V drain bias. 1D-cutlines taken at 5 ps following the ion strike                                                                            | 73 |

| 45. | TCAD calculated energy dissipation for 10 ps following the strike with the $SEB_{TH}$ conditions highlighted                                                                                                                                                                                      | 74 |

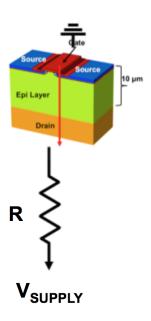

| 46. | Circuit schematic for a 3D-TCAD mixed mode ion-strike simulation with a resistor inline between the power supply and the drain node                                                                                                                                                               | 75 |

| 47. | 3D TCAD mixed-mode ion-strike simulations for both the MOSFET and JBS diode using non-destructive technique for adding a resistor inline with the power supply. Ion LET=10 MeV-cm <sup>2</sup> /mg and devices biased at 500 V                                                                    | 77 |

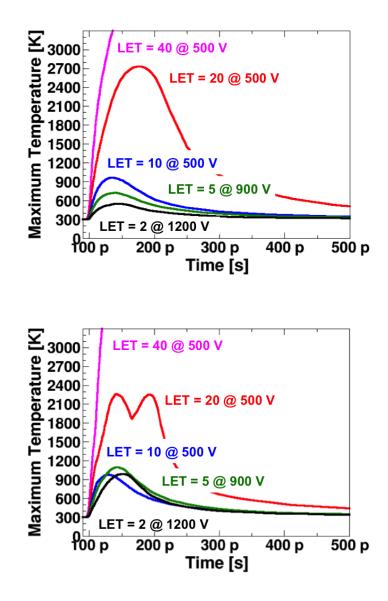

| 48. | 3D TCAD simulated maximum lattice temperature for ion LET (in MeV- $cm^2/mg$ ) and bias consistent with the single-event burnout threshold for 1200 V SiC JBS diode (top) and SiC MOSFET (bottom) $\ldots \ldots \ldots$                                                                          | 80 |

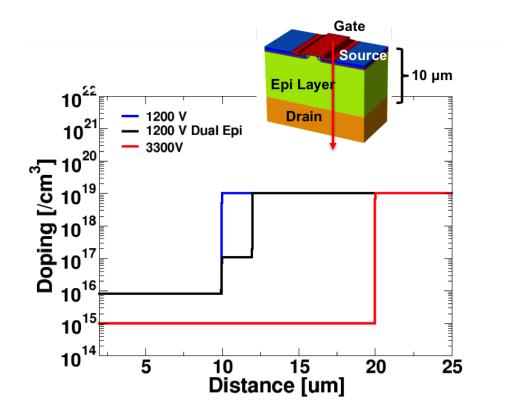

| 49. | 3D TCAD model of a 1200 V SiC power JBS diode showing device<br>structure, also shown is a representative long-range ion track (top). 1D-<br>cutlines of net doping through the epi and drain regions for each variant<br>(bottom)                                                                                                                                                                                                                     | 85  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

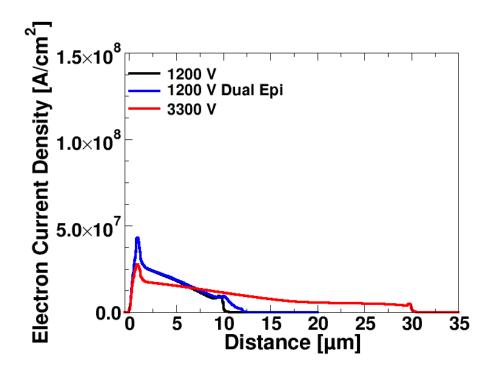

| 50. | Ion-induced electron current density at 20 ps following the strike for SiC power MOSFETs for particle with LET=10 MeV-cm2/mg and 500 V drain bias.                                                                                                                                                                                                                                                                                                     | 86  |

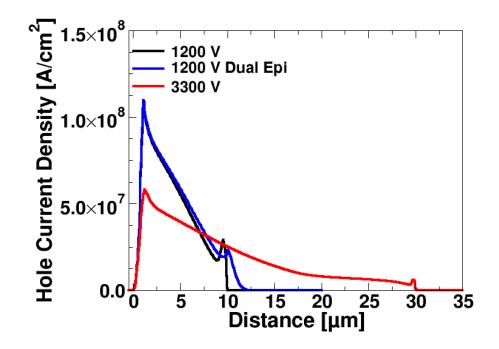

| 51. | Ion-induced hole current density at 20 ps following the strike for SiC power MOSFETs for particle with LET=10 MeV-cm2/mg and 500 V drain bias.                                                                                                                                                                                                                                                                                                         | 87  |

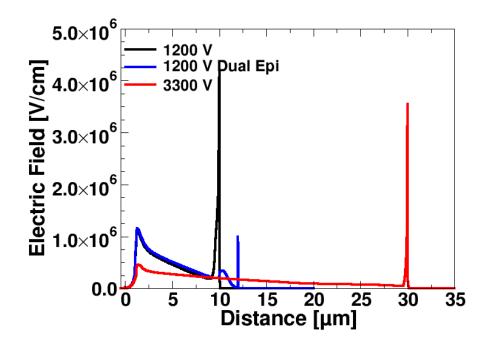

| 52. | Ion-induced hole electric field re-distribution at 20 ps following the strike for SiC power MOSFETs for particle with LET=10 MeV-cm2/mg and 500 V drain bias.                                                                                                                                                                                                                                                                                          | 88  |

| 53. | Ion-induced total power density at 20 ps following the strike for SiC power MOSFETs for particle with LET=10 MeV-cm2/mg and 500 V drain bias.                                                                                                                                                                                                                                                                                                          | 89  |

| 54. | Ion-induced current transient for a 1200 V SiC power MOSFET and diode for particle with LET=10 MeV-cm <sup>2</sup> /mg and 500 V drain bias                                                                                                                                                                                                                                                                                                            | 90  |

| 55. | Ion-induced current transient for a 1200 V SiC power MOSFET and diode for particle with LET=10 MeV-cm <sup>2</sup> /mg and 500 V drain bias                                                                                                                                                                                                                                                                                                            | 91  |

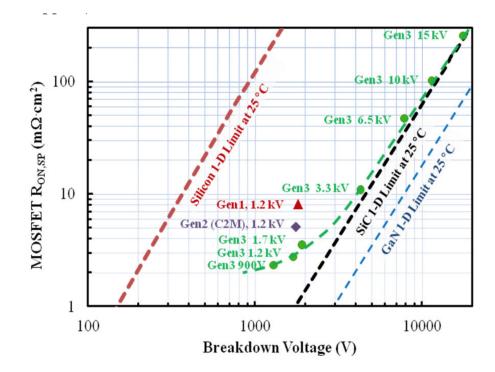

| 56. | One-dimensional specific on-resistance versus breakdown voltage com-<br>paring silicon, silicon carbide, and gallium nitride after Gajewski <i>et al.</i><br>[16]                                                                                                                                                                                                                                                                                      | 96  |

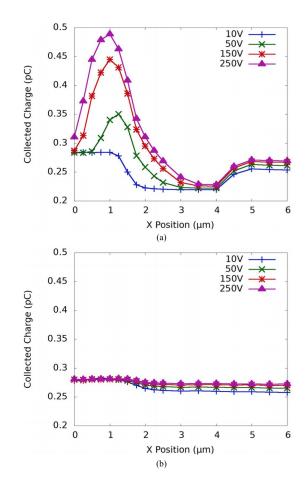

| 57. | TCAD simulations of collected charge in a MOSFET for a constant<br>amount of deposited charge but varying location and bias are shown<br>in (a). TCAD simulations of collected charge in a diode for a constant<br>amount of deposited charge but varying location and bias (b). For (a)<br>and (b), a strike location of 0 is at the center of the epitaxial region near<br>the surface between two p-doped regions. after Johnson <i>et al.</i> [75] | 116 |

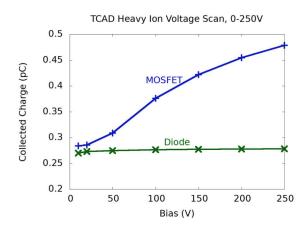

| 58. | TCAD simulations of collected charge in a MOSFET and diode for a constant amount of deposited charge in the most sensitive location but varying bias after Johnson <i>et al.</i> [75]                                                                                                                                                                                                                                                                  | 117 |

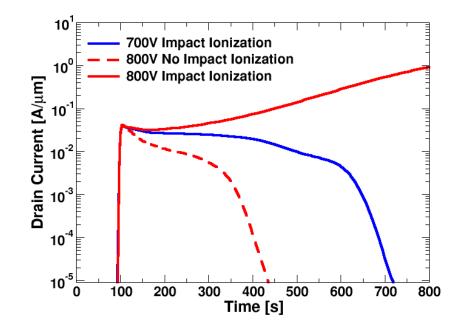

| 59. | TCAD heavy ion simulations of SiC power MOSFET, showing single-<br>event burnout at 800 V at LET=5 MeV-cm <sup>2</sup> /mg with impact ionization<br>turned on, and device recovery at other conditions.                                                                                                                                                                                                                                               | 119 |

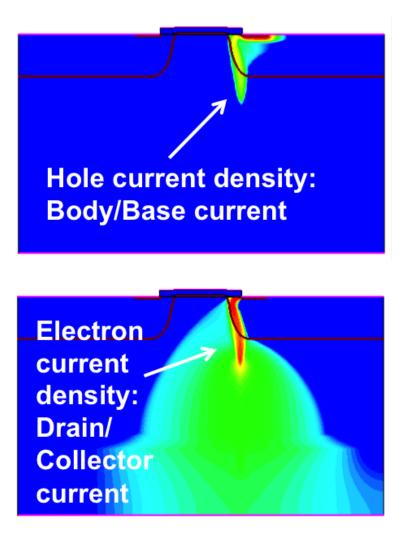

| 60. | 2D cross-section TCAD time slice 250ps after the strike occurs, showing<br>hole current density $(A/cm^2)$ (top), electron current density (bottom)<br>with impact ionization turned off, for LET=5 MeV-cm <sup>2</sup> /mg at VD=800<br>V. Blue indicates a current density of 1 A/cm <sup>2</sup> while red indicates a<br>current density of 106 A/cm <sup>2</sup> . | 121 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 61. | 2D cross-section TCAD time slice 250ps after the strike occurs, showing<br>hole current density $(A/cm^2)$ (top), electron current density (bottom)<br>with impact ionization turned on, for LET=5 MeV-cm <sup>2</sup> /mg at VD=800<br>V. Blue indicates a current density of 1 A/cm <sup>2</sup> while red indicates a<br>current density of 106 A/cm <sup>2</sup> .  | 122 |

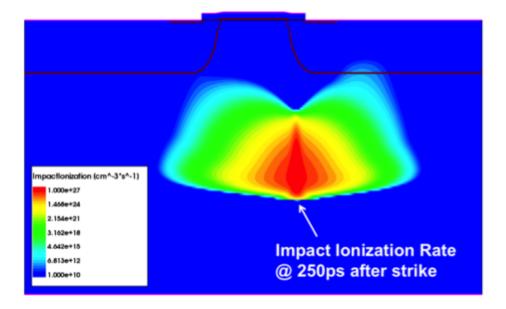

| 62. | Impact ionization (per cm <sup>2</sup> -s) at the epi/drain junction at 250 ps after the strike occurs for LET=10 MeV-cm <sup>2</sup> /mg at VD=800 V. Impact ionization rate ranges from 1e10 cm-3•s-1 (blue color) to 1e27 cm-3•s-1 (red color)                                                                                                                       | 123 |

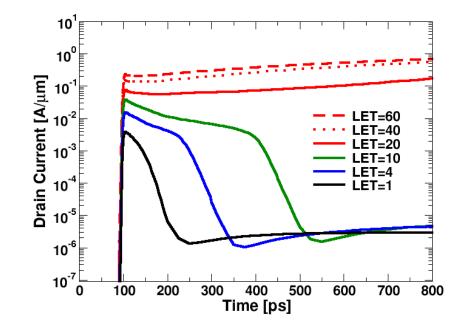

| 63. | TCAD heavy ion simulations of a SiC power MOSFET, showing drain current transient as a function of LET with the drain biased at 500 V. At LETs of 20 MeV-cm <sup>2</sup> /mg and greater, the drain current runs away, indicating a positive feedback loop between a parasitic BJT and impact ionization.                                                               | 124 |

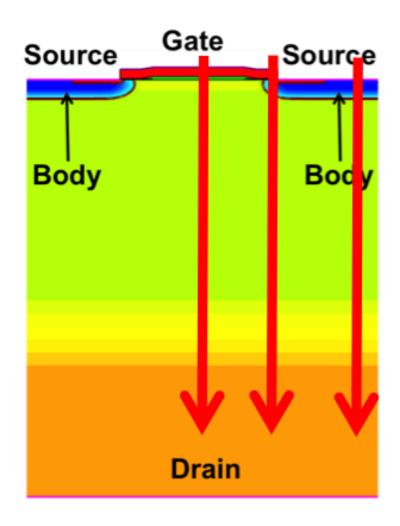

| 64. | 2D cross-section of TCAD model, with arrows indicating varied ion strike locations. In all cases, ion is at normal incidence.                                                                                                                                                                                                                                           | 125 |

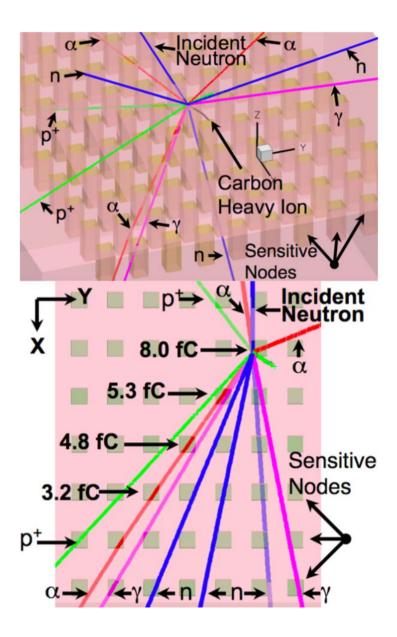

| 65. | TCAD representation of an MRED-generated nuclear event. The shaded volumes represent the sensitive nodes of the memory device. The incident neutron enters and induces a nuclear event. The shower of secondary products includes alpha particles, protons, neutrons, gamma rays, and a carbon heavy ion after Tipton <i>et al.</i> [81] $\ldots$                       | 129 |

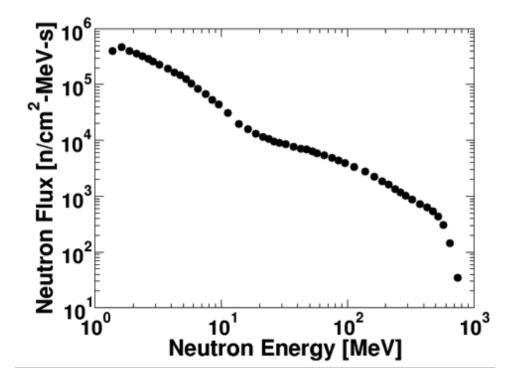

| 66. | Neutron spectrum from LANL [67] that closely matches the terrestrial neutron spectrum, and is used for MRED simulations.                                                                                                                                                                                                                                                | 130 |

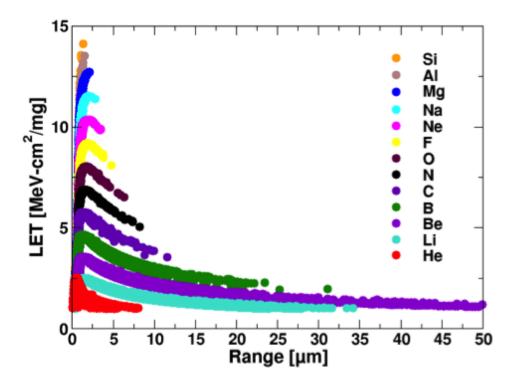

| 67. | Secondary particles (showing range and LET) generated from neutron<br>environment and entering the primary sensitive volume as calculated by<br>MRED.                                                                                                                                                                                                                   | 131 |

#### CHAPTER I

#### INTRODUCTION

Growth of the global power semiconductor industry hinges upon developing new technologies and products that can meet a wide range of voltage specifications, while providing higher power efficiency in a smaller package when compared to previous technologies. Applications range from low-voltage healthcare devices to high-power space, aerospace, automotive, and defense systems. Historically, power devices were all silicon-based, however, the past two decades have shown tremendous achievements in the use of wide-bandgap materials, such as silicon carbide (SiC), with the first commercially available 1200 V SiC power junction barrier Schottky diode offered in 2006 and the first 1200 V SiC power MOSFET offered in 2011 [1].

Silicon carbide is superior to silicon due to higher breakdown electric fields, increased thermal conductivity and significantly lower on-state resistance, all of which result in size, weight, and power (SWaP), and overall cost savings [2]. Over twenty automotive companies are using SiC power MOSFETs and diodes for onboard charging systems in their electric and hybrid-electric vehicles [3] in addition to many other applications. The global SiC power semiconductor market size was valued at \$302M in 2017, and projected to reach \$1.1B by 2025 [4], with 90% of the market focused on terrestrial applications, and 10% devoted to aerospace and defense applications [5], which would include space systems. The SWaP benefits of SiC over silicon make these power devices ideal candidates for space-based applications. These features are of interest to both National Aeronautics and Space Administration (NASA) and European Space Agency (ESA) for use in space vehicles, such as the Orion Spacecraft and the Venus Mobile Explorer [6], in addition to space solar arrays and a variety of other applications and interplanetary missions. However, microelectronic devices and circuits used in space may be susceptible to naturally occurring radiation, such as heavy ions.

Obtaining radiation data for semiconductor devices is an expensive, time-consuming task with single-event burnout (SEB) testing particularly challenging because of the destructive nature of the test. The safe operating area (SOA) for 1200 V SiC power MOSFETs and diodes has been characterized to a limited extent through test campaigns, however, little insight has been gained into the physical mechanism(s) that may be responsible for ion-induced single-event burnout. Understanding these mechanisms is imperative for organizations, such as NASA and ESA, for making space-flight hardware design decisions to mitigate risk of operational failure during a mission. Ion-induced radiation data for power devices reflects the response of a device from the perspective of an electrical terminal, or better defined as "on the outside looking in". Modeling and simulation tools, such as 3D Technology Aided Design (TCAD), provide the capability to explore the physical response of a device to radiation, leveraging available data to validate modeling and simulation efforts.

Historically, it has been thought that there are separate mechanisms responsible for the catastrophic failures observed in silicon power diodes (localized avalanche breakdown due to ion-induced electric field spikes) and silicon power MOSFETs (parasitic bipolar junction transistor), resulting in differing single-event burnout responses between the two types of devices. A natural assumption is that separate mechanisms are also responsible for single-event burnout in SiC power diodes and MOSFETs. However, that is not the case. In this work, industry-generated heavy ion data is compiled and combined with new data, identifying matching single-event burnout thresholds for the 1200 V power MOSFETs and diodes. Analysis of these heavy-ion data indicates that the devices have a common mechanism responsible for the catastrophic failures.

Insight into failure mechanisms is developed through the use of 3D TCAD simulations, which are used to identify similarities in both structures during an ion event. The simulation results show a resistive shunt effect capable of generating very high localized current transients during an ion strike, and consequently, significant energy dissipation. For LET and bias conditions matching the single-event burnout threshold data, a constant amount of energy dissipation is calculated through analysis of TCAD simulation results. Ion-induced, highly-localized energy pulses are proposed as a common mechanism responsible for catastrophic single-event burnout in 1200 V SiC power MOSFETs and JBS diodes.

The 3D TCAD framework developed in this work also provides an opportunity to efficiently evaluate the effects of an ion-strike on a variety of device variants (doping and dimension). Understanding how these variants perform following an incident heavy-ion strike will provide design teams an opportunity to consider alternate device designs that may meet the mission specification or otherwise mitigate the risk associated with single-event burnout during flight. This analysis may also prove to be useful for manufacturers that are interested in exploring radiation-hardened device development, further driving innovation for device reliability.

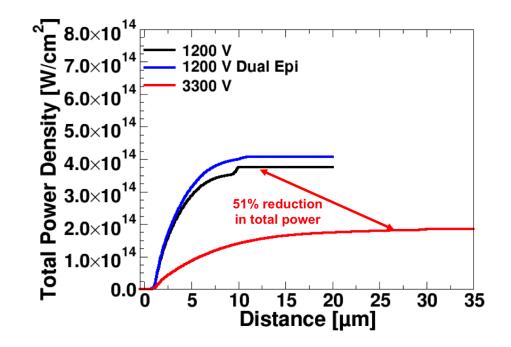

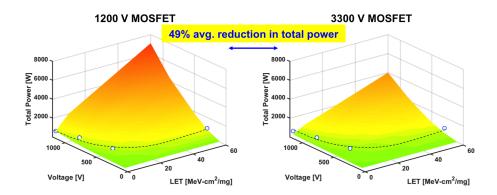

Typically, using a commercial off-the-shelf part is less expensive than using a special radiation-hardened device. Successfully designing a power electronic circuit to

operate while minimizing the risk of single-event burnout causing catastrophic failure of the circuit is important for both space and terrestrial applications. Circuit designers must understand the environment and the mechanisms contributing to single-event burnout in order to appropriately select parts. In this work, 1200 V and 3300 V SiC power MOSFETs are compared for operation in a circuit, with insight provided into the concept of voltage derating and a trade-off analysis focused primarily on power losses during operation. Implications for part selection and circuit design show that using a 3300 V power MOSFET provides ample single-event burnout threshold margin for space applications up to 650 V for most space environments, while the 1200 V device is susceptible to single-event burnout.

In this dissertation, Chapter II provides a brief overview of vertical power device structure and electrical operation, along with introducing the electrical benefits of SiC compared to silicon power devices. The development of 3D Technology Computer-Aided Design (TCAD) models for both the 1200 V power MOSFET and JBS diode are discussed in Chapter III. This discussion provides detailed information about the physical structure (doping and dimensions) along with the electrical characteristics (current and voltage) for each device, establishing the similarity between the MOSFET and the diode. Historical concepts of single-event burnout and the effects of ion-induced charge deposition in power devices are explored in Chapter IV. This work identifies a unique similarity in the single-event burnout response of SiC power MOSFETs and JBS diodes in Chapter V, leveraging ioninduced single-event burnout data from available literature, in addition to describing data taken during this work. A novel method for analyzing ion-induced energy pulses for both diodes and MOSFETs is presented in Chapter VI. In Chapter VII, evaluation of ion-induced effects on device variants is explored and potential tradeoffs in performance are discussed. Finally, Chapter VIII provides considerations for circuit designers and risk mitigation in heavy ion environments. Chapter IX discusses the impact of this work for the radiation effects community.

There is an Appendix A for discussion about the role of the parasitic bipolar junction transistor turn-on following an ion strike in the SiC power MOSFET, and a final Appendix B providing discussion about neutron-induced secondary particle generation in SiC in a terrestrial environment.

### CHAPTER II

### POWER DEVICE STRUCTURE AND OPERATION

An estimated 50% of the electricity used in the world is controlled by power devices [7], with applications ranging from consumer, industrial, medical, and transportation. Efficiency and cost of systems drives innovation, with silicon power devices dominating the market for the past few decades. However, silicon power devices have proven to have significant conduction power losses for high-voltage applications due to the design of the device. Silicon carbide provides vast improvements in size, weight, and power, when compared to silicon because of the superior electrical properties of SiC over silicon [7]. This chapter discusses the general power device structure and compares silicon to SiC, while also introducing the safe operating area for power devices.

#### <u>Power Device Structure</u>

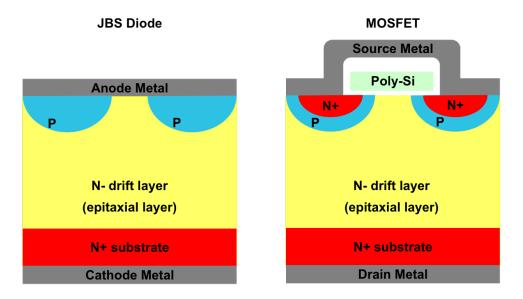

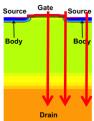

Power MOSFETs are the most commonly used power devices for a wide range of applications, such as power supplies, DC-to-DC converters, and motor controllers [8], while power diodes are commonly used in rectifying circuits [9]. Commercially available power MOSFETs and JBS diodes typically have a vertical structure which provides higher breakdown voltages, lower on-state resistance, and higher current than a lateral structure. The MOSFETs are commonly called Vertical Double-Diffused MOSFETs, or VDMOS [10] due to the double-diffusion process for creating the source and body regions. A Junction-Barrier Schottky (JBS) diode can be designed in the same process as the MOSFET, with the exceptions of no source implant and replacing the gate stack with a Schottky contact. Typical cross-sections of each device are shown in Figure 1. Most MOSFETs are NMOSFETs with the starting wafer a

Figure 1: Typical cross-sections for planar, vertical power junction-barrier Schottky diode and power MOSFET

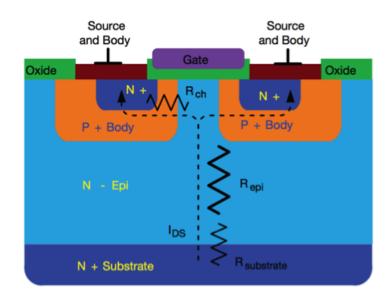

heavily doped n-type substrate. The n-type drift layer, the epitaxial layer or epi region, is then grown onto the substrate, and will be lightly doped. The doping of the epi region sets the breakdown voltage, with the thickness of the epi region designed to allow for full depletion of the epi region under reverse bias. Subsequent processing steps involve implanting the p-type body region and the heavily doped n-type source, followed by growing a gate oxide and depositing the back end of line metal layers. In both the JBS diode and the MOSFET, current flow is vertical when the device is ON, and when the device is OFF, the applied bias is supported across the entire epi region. In a power device, the doping and thickness of the epitaxial layer set the primary characteristics of the device with respect to breakdown voltage and current capacity. Resistance through the epi region increases as the epi thickness increases and the doping density decreases. The resistive paths through the device are shown in Figure 2 [11], with the resistance through the epi region dominating the total resistance along the path of current flow. For silicon power devices, designing a high-voltage, low-resistance device has proven to be challenging, with an example of a silicon power MOSFET rated at 1000 V [12] and 8 A, with 1450 m $\Omega$ s of on-state resistance ( $R_{ON}$ ), shown in Table 1. This particular device was chosen because the rated breakdown voltage is similar to the rated breakdown voltage of the SiC power MOSFETs that are discussed in this work.

Figure 2: Typical cross-section of a power MOSFET defining resistive paths through the device after Havanur *et al.* [11]

Table 1: Comparison of on-state resistance and rated current for two commercially available power MOSFETs, one silicon and one SiC [12], [13]

| Device      | Material | $V_{BREAKDOWN}$ [V] | $R_{DS,ON} [m\Omega s]$ | $I_{RATED}$ [A] |

|-------------|----------|---------------------|-------------------------|-----------------|

| FQA8N100C   | Si       | 1000                | 1450                    | 8               |

| C2M0080120D | SiC      | 1200                | 80                      | 36              |

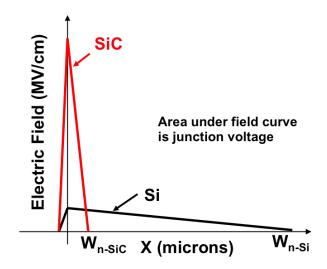

Silicon carbide (SiC) is superior to silicon for use in many power device applications due to significantly higher breakdown electric fields and significantly lower onstate resistance [2]. These benefits can be attributed to the electrical properties of SiC compared to silicon, a few of which are summarized [14] and shown in Table 2. A semiconductor with a wide bandgap requires more energy to produce carriers through impact ionization which leads to electrical breakdown than a semiconductor with a narrow bandgap. SiC has a bandgap of 3.3 eV, compared to 1.1 eV for silicon, which results in a critical electric field in SiC of 2-3 MV/cm compared to 0.2-0.3 MV/cmin silicon. This concept can be visualized by considering the peak electric field as a function of distance  $(W_n)$  for both SiC and silicon, as shown in Figure 3. For a given applied potential (the area under the electric field curve), the electric field in SiC reaches a much higher peak over a shorter distance when compared to silicon. This effect directly results in lower on-state resistance and higher drive currents for SiC compared to silicon. The electrical characteristics of SiC have resulted in commercially available high-voltage and low-resistance devices, with a 1200 V SiC MOSFET providing 36 A at 80 m $\Omega$  of on-state resistance [13], also shown in Table 1.

| Electrical Property              | Si   | SiC (4H) |

|----------------------------------|------|----------|

| Band Gap Energy (eV)             | 1.12 | 3.28     |

| Critical Electric Field (MV/cm)  | 0.29 | 2.5      |

| Electron Mobility $(cm^2)/VS$    | 1200 | 800      |

| Hole Mobility $(cm^2)/VS$        | 490  | 115      |

| Thermal Conductivity (W/cmK)     | 1.5  | 3.8      |

| Maximum Junction Temperature (C) | 150  | 600      |

Table 2: Electrical property comparison of Silicon and SiC after Choi *et al.* [14]

Figure 3: Electric field concept comparison of silicon and SiC as a function of distance,  $W_n$ . The area under each field curve is the junction voltage, which is equal in this example

#### Power Device Safe Operating Area

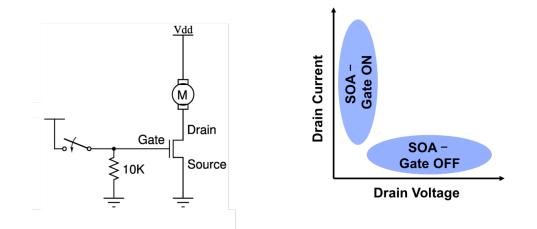

Power devices are intended to operate in either a high-voltage, low-current state, or a low-voltage, high-current state to prevent significant power dissipation that may impact device and/or circuit reliability. An example of a power MOSFET being used as a switch to drive a load and the current/voltage safe operating area (SOA) is shown in Figure 4. Note that this figure is conceptual, and an actual circuit will have a diode connected from the drain to ground to allow a path for inductive current to flow when the MOSFET is OFF. When the MOSFET driving the load is turned OFF, the drain is biased at the supply voltage, and the drain current through the circuit is minimized, referred to as OFF-state leakage current. As the MOSFET is slowly turned ON by increasing the gate voltage, the drain current increases significantly while the drain-to-source voltage drops. The device is stable in both OFF and ON states. During the transition from OFF to ON, the gate voltage is controlled in such a way as not to exceed the switching speed of the device, typically in the tens to hundreds of nanoseconds for a power MOSFET [13], maintaining stability through the transition. In addition to the device and circuit being stable, power dissipation, or the product of current times voltage, is maintained in such a way that the device can continue to operate without physical damage. Significant power dissipation can result in catastrophic device failure, such as the separation of metal lines from the semiconductor surface, electromigration of metal through a metal/semiconductor interface, or thermal heating leading to metal and/or semiconductor damage.

Figure 4: Conceptual example of a power MOSFET being used as a switch to drive a load (left) and the safe-operating area (SOA) (right). An actual circuit will also have a diode from drain to ground for inductive current flow when the transistor is OFF

### CHAPTER III

#### 3D TCAD MODEL DEVELOPMENT

Chapter II provided a brief overview of vertical power device structure and electrical operation, along with introducing the electrical benefits of SiC compared to silicon. In this chapter, a detailed discussion of a 1200 V SiC power MOSFET and a 1200 V JBS diode is provided, to include both physical (doping and dimension) and electrical (current and voltage) characteristics. Both the MOSFET and the JBS diode can have the same breakdown voltage, indicating that the devices share the same or very similar doping, epitaxial dimensions, and other physical geometries. Of particular importance to this work is that the rated breakdown voltage, 1200 V, is consistent between both devices, and is typically determined experimentally by device manufacturers. The data that will be shown in Chapter V is for 1200 V commercial devices. For specifying the device breakdown rating, most manufacturers use an unclamped inductive switching (UIS) test methodology (established as a JEDEC standard [15]) to determine an avalanche safe operating area (SOA) for the SiC devices. In these devices, there are zero failures in 1000 hours at low avalanche conditions, 1200 V at 150 C, hence, the 1200 V rated breakdown voltage [16].

Electrical data, both before and after radiation exposure, provide insight into the behavior of a semiconductor device from an external point of view, where measurement equipment can characterize current and voltage. 3D Technology Computer-Aided Design (TCAD) tools provide an opportunity to investigate internal device physics, such as current density, electric field, and impact ionization. TCAD tools are finite-element based solvers for carrier diffusion and transport, solving Poisson's and the electron and hole continuity partial differential sets of coupled equations. The remainder of this chapter will discuss the physical 3D model, followed by the electrical breakdown operation.

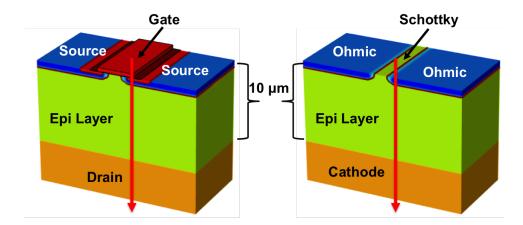

#### Physical Device Design

Typically, power devices are designed to take advantage of a large die area, for example, 2 mm x 3 mm. Either a honeycomb or a striped cell design is commonly used and a device is composed of many cells in parallel. 3D TCAD models of a single cell, 1200 V SiC power MOSFET and JBS diode, Figure 5 (top), were developed in the Synopsys Sentaurus suite of TCAD tools, version K-2015.06, [17], based on information from published literature [18], [19]. The devices have an epitaxial thickness of 10  $\mu$ m, with doping of 8x10<sup>15</sup> cm<sup>-3</sup> N-type, with an additional 15  $\mu$ m of highly-doped N+ drain (the highly-doped drain is truncated in Figure 5 for visualization purposes). Otherwise, the models shown in Figure 5 are to-scale, with the thickness of the epitaxial region indicated for guidance. Additional parameters are listed in Table 3.

Both devices have the same P-type body doping at the surface of the device, seen more clearly in the 2D-cutplanes, also shown in Figure 5. In the JBS diode, after implanting the P-type body doping, the surface metallization is deposited. The JBS diode has been designed in such a way that the device can operate as a P-i-N diode when reverse-biased, and as a Schottky diode when forward-biased [20], with representative electron current flow indicated in Figure 5 (middle). The MOSFET has a highly doped (N+), source region implanted, and the source metal contacts both the N+ source and the P-type body. This is an effective option for grounding the body to the source. A gate oxide of 50-100 nm is deposited over the center of the structure, with polysilicon covering the gate oxide to control the channel regions, with representative electron current flow indicated in Figure 5 (middle). In both the diode and the MOSFET, applying positive voltage to the drain results in a depletion region forming in the epitaxial region, and at 1200 V, the entire epitaxial region is depleted, see Figure 5 (bottom). Consequently, vertical structure, doping, and dimensions, of both the diode and the MOSFET are nearly identical.

Table 3: Parameters Used in TCAD Simulations for MOSFETs and Diodes

| Parameter            | Value                                                            |

|----------------------|------------------------------------------------------------------|

| 4H-SiC               | Bandgap = 3.26  eV                                               |

| P-Body Doping/Depth  | $1 \mathrm{x} 10^{19} \mathrm{cm}^{-3}, 1 \ \mu \mathrm{m}$      |

| N-Epi Doping/Depth   | $8 \mathrm{x} 10^{15} \mathrm{cm}^{-3}, 10 \ \mathrm{\mu m}$     |

| N+Drain Doping/Depth | $1 \mathrm{x} 10^{19} \mathrm{\ cm}^{-3},  15 \; \mu \mathrm{m}$ |

Figure 5: 3D TCAD model of a 1200 V SiC power MOSFET (top left) and JBS diode (top right) showing device structure (epi doping/depth). 2D-cutplanes indicating current flow in forward operation (middle) and fully-depleted epitaxial region at 1200 V (bottom)

#### Electrical Breakdown Simulation

As discussed previously, a power device is susceptible to single-event burnout when the device is OFF. Although device forward characteristics are very interesting, the reverse characteristics are more important to single-event burnout. Under this bias condition, there exists a very large depletion region in which charge can be deposited. In addition, the presence of a strong electric field is responsible for impact ionization and carrier generation in normal electrical operation, along with providing a mechanism for rapidly moving radiation-induced charge out of the depletion region. For the remainder of this dissertation, the N+ heavily doped substrate will be referred to as the drain, which is consistent with MOSFET terminology. In a diode, this region is called a cathode, but for sake of comparison to the MOSFET in both text and plots, the cathode will also be referred to as a drain.

For electrical breakdown, positive voltage is applied to the drain of the device, and the current flowing through the drain is monitored. For lab measurements, compliance is set for the current in order to protect both the measurement equipment and the device under test (DUT). In simulation, there are no such restrictions. As the depletion region is formed at any P-N junction in a semiconductor, and as the voltage across the junction increases, the depletion region grows, described by

$$X_D = \sqrt{\left[\frac{2\epsilon_s}{q}\left(\frac{1}{N_a} + \frac{1}{N_d}\right)(\phi_i - V_a)\right]} \tag{1}$$

where  $\epsilon_s$  is the permittivity of SiC, q is the electronic charge,  $N_a$  is the acceptor doping concentration in the p-type body,  $N_d$  is the donor doping concentration is the n-type epitaxial region,  $\phi_i$  is the built-in potential at the P-N junction, and  $V_a$ is the externally applied bias across the P-N junction [21]. The built-in potential is described by

$$\phi_i = \frac{kT}{q} ln \frac{N_a N_d}{n_i^2} \tag{2}$$

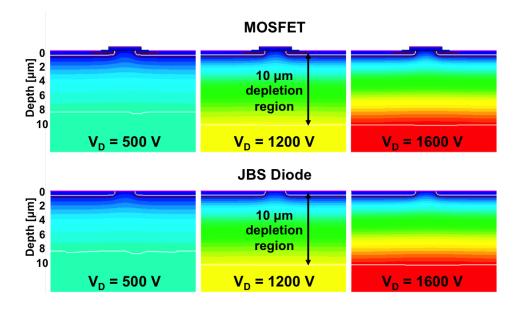

where k is Boltzmann's constant, T is the temperature in Kelvin and  $n_i$  is the intrinsic carrier concentration of SiC, which is  $5 \times 10^{-9} cm^{-3}$  [22]. In a step (one-sided or abrupt) P-N junction, there exists a large change in dopant level magnitude. For power device, the P-type body is typically doped 3-5 orders of magnitude higher than the N-type epitaxial region, essentially forming a step junction from P-type to N-type. As shown in Table 3, the P-type body is doped slightly more than 3 orders of magnitude higher than the N-type epitaxial region. This results in the depletion region extending significantly into the N-type epitaxial region, effectively setting the maximum depletion region thickness as the thickness of the epitaxial region. This can be seen in a series of 2D-cutplanes of electron density as a function of drain bias, shown in Figure 6. With the drain at 500 V, the depletion region (light blue) is 8  $\mu$ m wide, and at 1200 V, the epitaxial region is fully depleted at 10  $\mu$ m wide. Due to the N+ drain region, the depletion region can extend no further, evidenced by the 1600 V condition which shows no increase in depletion region thickness.

The charge density in a depletion region is described by Poisson's equation

$$\frac{d\mathcal{E}}{dx} = \frac{\rho}{\varepsilon_s} = \frac{q}{\varepsilon_s} N_d \tag{3}$$

which can be integrated to find the electric field,  $\mathcal{E}$

$$\mathcal{E}(x) = -\frac{q}{\varepsilon_s} N_d(x - x_n) \tag{4}$$

and as shown Equation 4, the electric field varies linearly within the depletion region. Both of these relationships are shown in Figure 7, which is a series of 2D-cutplanes

Figure 6: 2D-cutplanes of the electron density for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V

showing the internal electric field for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V. At 500 V, the electric field is linearly graded over the epitaxial region, with an  $\varepsilon_{max}$  of 1.6 MV/cm at the corner of the P-type body. As the drain voltage increases to 1200 V and then to 1600 V,  $\varepsilon_{max}$  increases to 2.8 MV/cm and 3.2 MV/cm, respectively. Once the N-type epitaxial region becomes fully depleted, with no additional area in which the depletion layer can grow, the electric fields at the corners of the P-type body increase rapidly, shown in Figure 7. This mechanism is even more evident when plotted as a series of 1D-cutlines, shown in Figure 8. The electric field is linear throughout the entire epitaxial region, and at 500 V, extends slightly over 8  $\mu$ m. At 1200 V, there is a clear truncation of the electric field at the epitaxial region and N+ drain interface, where the electric field drops to 0 V/cm. However, at the P-type body and epitaxial region interface, the electric field has reached a maximum value. This is further established as the drain voltage

is increased to 1600 V, and as noted above, has reached an  $\mathcal{E}_{max}$  of 3.2 MV/cm.

Figure 7: 2D-cutplanes of the internal electric field for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V

The electrostatic potential in the epitaxial region is obtained from the electric field using

$$\frac{d(\phi_i - V_a)}{dx} = -\mathcal{E} \tag{5}$$

which is integrated to give the total potential across the P-N junction by

$$\phi_i - V_a = \frac{q N_d x_n^2}{2\varepsilon_s} \tag{6}$$

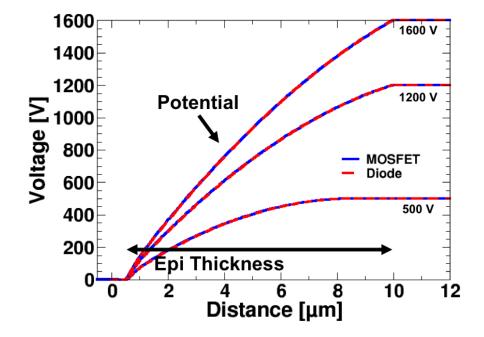

This concept is highlighed in Figure 9, which is a series of 2D-cutplanes showing the internal electrostatic potential for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V. At 500 V, the depletion region width (shown as a white line on the contour plot) extends slightly over 8  $\mu$ m. When the drain voltage is increased to 1200 V, the 10  $\mu$ m wide epitaxial region is fully depleted. Once the epitaxial region is fully depleted, it can extend no farther because of the N+ drain region. 1D-cutlines of the electrostatic potential for both the MOSFET and diode

Figure 8: 1D-cutlines of the internal electric field for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V

are shown in Figure 10. In all bias conditions, the entire externally applied voltage is dropped over the epitaxial region, with the slope changing significantly as the drain voltage increases.

This discussion provides the basis for designing a vertical power device. In particular, the epitaxial doping determines the slope of the electric field under a given externally applied voltage. For the 1200 V SiC power device structure, the epitaxial doping was set so that the epitaxial region can be fully depleted at 1200 V, while limiting the maximum electric field, given by

$$\mathcal{E}_{max} = \frac{2(\phi_i - V_a)}{x_n} \tag{7}$$

which results in creating mobile carriers in a process known as impact ionization. Impact ionization occurs when a mobile carrier is accelerated by an electric field in a

Figure 9: 2D-cutplanes of the internal electrostatic potential for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V

Figure 10: 1D-cutlines of the internal electrostatic potential for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V

depletion region, and a collision occurs between mobile carriers and electrons in the semiconductor lattice with enough energy to free additional electron-hole pairs. This is an avalanching effect can result in very high conduction (current flow). Impact ionization rates are exponentially related to electric field, and while impact ionization can occur with any electric field, as the electric field increases, impact ionization does as well, and with the carrier generation rate described by

$$G^{ii} = \alpha_n n v_n + \alpha_p n v_p \tag{8}$$

where n/p are the available free carriers,  $v_n/v_p$  is the carrier velocity, and  $\alpha_n/\alpha_p$  are the avalanche coefficients [17]. For the simulations in this work, the Okuto-Crowell Model was selected for avalanche coefficients, where  $\alpha$  is described by

$$\alpha = a\mathcal{E}^{\gamma} exp(-\frac{b^{\delta}}{\mathcal{E}}) \tag{9}$$

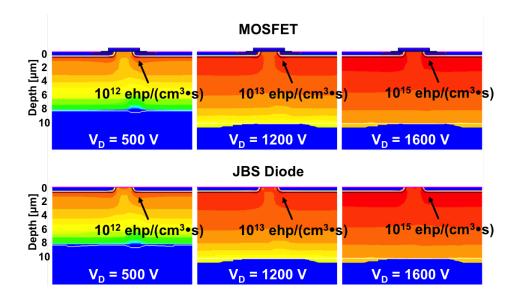

where  $a, b, \gamma$ , and  $\delta$  are fitting parameters [17]. This concept is highlighted in Figure 11, a series of 2D-cutplanes showing the impact ionization rates for both the MOSFET and the diode, when biased at 500 V, 1200 V, and 1600 V. The impact ionization rate as a function of position in each device is shown in Figure 11. At 500 V, impact ionization is low, and the rate increases significantly as the drain voltage is increased. When this field reaches approximately 3.2 MV/cm, defined as the critical field, avalanche breakdown can occur, and is consistent with ranges of electric field required for avalanche breakdown in 4H-SiC [23].

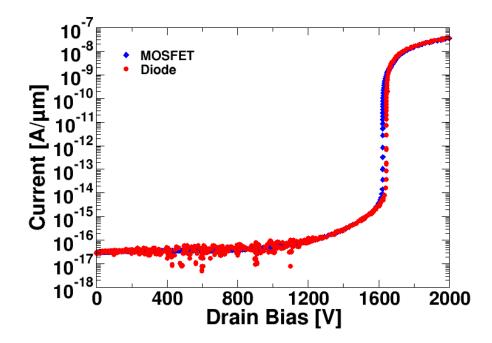

3D TCAD electrical breakdown simulation results as a function of reverse bias are shown in Figure 12 for the 1200 V SiC power MOSFET and JBS diode. Both devices were simulated in a reverse-bias condition up to 2000 V, and the simulation results in Figure 12 show that both devices enter avalanche breakdown with approximately

Figure 11: 3D TCAD-simulated electrical avalanche breakdown as a function of reverse bias for 1200 V SiC power MOSFET and diode

Figure 12: 3D TCAD-simulated electrical avalanche breakdown as a function of reverse bias for 1200 V SiC power MOSFET and diode

the same current-voltage relationships. Physically and electrically, these two devices are very similar.

# CHAPTER IV

# RADIATION-INDUCED SINGLE-EVENT EFFECTS BACKGROUND

Single-event burnout (SEB) is a phenomenon where a power MOSFET or diode, transitions from a stable, low-current state to non-recoverable, high-current state as a result of heavy-ion radiation exposure. This phenomenon was first reported in 1986 for a silicon power MOSFET [24]. An illustration of a power MOSFET in the OFF-state being hit by an ion and the transition of the device into an unstable operating region is shown in Figure 13. The ion, which deposits charge in the form of electron-hole pairs, acts as a current source, forcing the device into a high-current, high-voltage state that may be outside the safe operating area (SOA). The severity of the ion event is a function of particle energy and device bias, with a small deviation outside the SOA likely to result in a single-event transient (SET) of either current or voltage, or both. However, if the event is more severe, it may render the device permanently inoperable, typically as a result of significant current flow that may cause metal line failure, separation of semiconductor material interfaces, or excessive temperatures exceeding the melting point of materials in the device.

Although power MOSFETs and diodes are structurally very similar, it has generally been thought that there are separate mechanisms responsible for the catastrophic failures observed in silicon power diodes (localized avalanche breakdown due to ioninduced electric field spikes) and silicon power MOSFETs (parasitic bipolar junction transistor). The remainder of this chapter will detail the historical concepts driving single-event burnout in both types of devices, including some discussion on modeling techniques. This discussion is very important for this work for a variety of reasons. First, silicon power diodes are much more radiation tolerant than silicon power MOSFETs due to the differing mechanisms driving single-event burnout. Significant effort has been dedicated to understanding these differences through modeling and analysis, providing significant insight into the physical mechanisms behind singleevent burnout in silicon power devices. Second, while the SiC MOSFETs and diodes have been characterized through test campaigns (though far less so than silicon devices), little insight has been gained for the physical mechanism(s) that may be responsible for ion-induced single-event burnout. This dissertation identifies that the long-standing concepts for silicon single-event burnout are not specifically applicable to SiC single-event burnout, resulting in describing a new mechanism for singleevent burnout in SiC diodes and MOSFETs, while also developing a simulation methodology to capture this mechanism. Third, with silicon power MOSFETs significantly less susceptible to single-event burnout than diodes, much effort has been focused on increasing the single-event burnout tolerance of the MOSFETs, with much less attention on the diodes. SiC power MOSFETs and power diodes are equally susceptible to single-event burnout, and this work will demonstrate the potential to increase the single-event burnout tolerance for both devices using the same techniques.

Figure 13: Example of a power MOSFET in the OFF-state hit by an ion (left), forcing a high-current, high-voltage state that may be non-stable and outside of the SOA

## Space Radiation Environment

The Galactic Cosmic Ray (GCR) background radiation environment that exists in space consists of many high-energy, charged particles [25] that are capable of interacting with the materials used in microelectronic devices and circuits. Many of these energetic charged particles will produce free electron-hole pairs in a semiconductor material as the particle interacts with the crystal lattice. As the ion passes through the semiconductor, a plasma of electron-hole pairs is created, and the energy deposition is defined as the linear energy transfer (LET), which has units of [(energy/distance)/(mass/volume)]. The energy deposition can also be defined as stopping power which has units of [energy/distance]. The charge generated in the semiconductor is dependent on the original particle energy and the mass of the semiconductor, and can be calculated as

$$Q\left[pC\right] = \frac{LET\left[\frac{MeV-cm^2}{mg}\right] * \rho\left[\frac{mg}{cm^3}\right] * 1.6 \times 10^{-5}}{G\left[eV\right]} = L\left[\frac{pC}{\mu m}\right] * X\left[\mu m\right]$$

(10)

where the units of each variable is indicated in the brackets and Q is the total charge deposited along the particle path length. *LET* is the linear energy transfer of the ion,  $\rho$  is the density of the semiconductor material, and G is the electron-hole pair generation energy. This relationship can be rearranged to show the stopping power, which is L, along the ion path length, X. In silicon, the bandgap is 1.1 eV, and in SiC, the bandgap is 3.3 eV. Energy deposited in excess of the bandgap energy has the potential to create an electron-hole pair, however, much of the energy is thermalized in the lattice, requiring an average energy that is 2-3 times larger than the bandgap to create an electron-hole pair. In silicon, an average of 3.6 eV is required [26], [27], and in SiC, an average of 7.5 eV is required [28], [29].

In a semiconductor device, when a P-N junction is reverse-biased, a depletion region is formed. As the reverse-bias increases, the depletion region increases in width, and the electric field across the depletion region increases accordingly. Electron-hole pairs created by an ion passing through the depletion region are separated by the electric field, and holes move towards the p-type region, while electrons move towards the n-type region. A drawing of the ion passing through a depletion region and generating electron-hole pairs is shown in Figure 14, with the electrons moving to the n-type region and the holes moving to the p-type region. The currents that arise at the device terminals from the carrier movement is called ion-induced transient current and is a function of the magnitude of the electric field and the density of electron-hole pairs generated by the ion.

Figure 14: Schematic cross-sections for vertical power junction-barrier Schottky diode and power MOSFET indicating electron-hole pairs generated by the passage of a heavy ion

#### Single-Event Burnout - Si Power Devices

## **MOSFETs**

A single-event burnout current signature for a silicon power MOSFET during heavy ion irradiation is shown in Figure 15 [30]. The MOSFET is reverse biased in a steady state condition. Approximately 50 ns after the ion strike, the drain current shows a virtually instantaneous rise until the current compliance of the measurement system is reached, while the gate current remains unchanged. This indicates that a resistive short has been created between the drain and the source. The gate current remains relatively unchanged, indicating that the gate is undamaged. This is a classic example of drain-to-source single-event burnout in a power MOSFET [30]. Typically for single-event burnout, physical damage can be seen on the die, as shown in Figure 16 [30]. In this example, the die prior to single-event burnout appears pristine, and following single-event burnout, there is a visible crater on the surface of the die. Visible damage, combined with either a drain-to-source or a drain-to-gate short circuit is evidence of a single-event burnout event.

Single-event burnout in silicon power MOSFETs has historically been attributed to a positive feedback loop with avalanche carrier generation and the turn-on of a parasitic NPN bipolar transistor [24]. A visual interpretation of the parasitic BJT is shown in Figure 17, with the collector (drain), base (body), and emitter (source) labeled. In a typical power device configuration, the body and source are shorted together by the common metallization, so the body voltage has no ability to rise and forward-bias the body-source P-N junction. However, when the passage of a heavy-ion deposits charge in the device, lateral current flow along the P-type body

Figure 15: Example of SEB during heavy ion irradiation of a power MOSFET. Sudden drain current increase indicates drain-to-source short circuit after Titus *et al.* [30]

Figure 16: Before and after photos of SEB. Visible physical damage is a likely indicator of SEB after Titus  $et \ al.$  [30]

region allows the body voltage to rise, forward-biasing the body-source P-N junction, turning on the parasitic BJT. This occurs simultaneously with the avalanche carrier generation due to the high electric fields present in the device, which can be seen in TCAD simulation results from Liu *et al.* in Figure 18 [31]. These simulation results show the internal electric field is redistributed during the ion strike, peaking at the interface between the epitaxial and drain regions. The positive feedback loop between the parasitic BJT and the avalanching carriers, each with a positive gain, results in a condition where high current and high voltage are sustained sufficiently to physically damage the device through metal/semiconductor separation at the contact, burnout of metal lines, or thermal meltdown of the silicon.

Figure 17: Inherent N-P-N parasitic BJT transistor in a vertical DMOS device after Johnson *et al.* [32]

Figure 18: Electric field distribution pre-strike (A) and post-strike (B and C) for simulated ion strike in a power MOSFET. A to B to C represents an evolution of the electric field as a function of time after Liu *et al.* [31]

#### Diodes

In 1994, Kabza *et al.* reported the first single-event burnout in silicon power diodes [33], with the single-event burnout signature shown in Figure 19. The current shows a virtually instantaneous rise until current compliance of the measurement system is reached. The corresponding decrease in functionality of the diode to block the externally applied voltage indicates a resistive short created between the anode and the cathode. In addition to the electrical characteristics, Kabza reported "the failure pattern consisted of a spontaneous short without prior indication; the devices exhibited a pin hole size molten channel from cathode to anode". The physical damage in the silicon power diodes appeared to be consistent with physical damage observed in silicon power MOSFETs. However, in a silicon power diode, there is no parasitic NPN bipolar present, suggesting that the mechanism for single-event burnout in a silicon power diode is not the same that in silicon power MOSFETs. In the same work, Kazba presented 2D cylindrical TCAD simulations for charge deposition in a diode, concluding that the ion-induced charge resulted in re-distributed internal electric fields that were larger in magnitude than the pre-strike electric fields. Simultaneously, high current densities, combined with the increased electric fields contribute to very high local power densities, likely to cause local temperature increases and self-heating [33].

In 1998, Maier *et al.* investigated the impact of avalanche multiplication (which is exponentially dependent on electric field) on single-event burnout in silicon power diodes [34]. Charge generated in a silicon power diode from a single ion was measured with a charge-sensitive preamplifier, and the results are shown in Figure 20 [34]. At low voltages, below 850 V, a single charge collection peak is observed corresponding

Figure 19: Oscilloscope recording of reverse blocking current and voltage during failure. The destructive current develops in less than 10 ns after Kabza *et al.* [33].

to the direct energy loss of the ion. As the voltage increases, the charge collection peak both broadens and shifts, with the shift interpreted as a amplification of charge carriers from avalanche multiplication. Once the voltage is increased past 1100 V, all deposited charge contributes to avalanche carrier generation.