# CHARACTERIZATION, ANALYSIS, AND MITIGATION OF PROCESS, VOLTAGE, AND TEMPERATURE (PVT) VARIATIONS ON ELECTRICAL MASKING AND RADIATION–INDUCED TRANSIENTS

By

Semiu A. Olowogemo

Dissertation

Submitted to the Faculty of the Graduate School of Vanderbilt University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

May 12, 2023

Nashville, Tennessee

Approved:

William H. Robinson, Ph.D.

Arthur Witulski, Ph.D.

Brian Sierawski, Ph.D.

Hiba Baroud, Ph.D.

Ronald Schrimpf, Ph.D.

Copyright © 2023 Semiu A. Olowogemo All Rights Reserved

## DEDICATION

This dissertation is dedicated to God, the Creator of the planets and everything in and around them (Psalm 24:1), the Giver of life (Genesis 2:7), and the Owner of cattle on a thousand hills (Psalm 50:10-12), who strategically positioned resources and helpers along the journey of my life because of His love and unlimited grace on me.

#### ACKNOWLEDGMENTS

I want to thank my parents and family, whose prayers and support gave me the strength to keep searching for the knowledge they did not have the opportunity to get. Thank you, mum, for providing what I needed to sit like others in my elementary, secondary, and undergraduate classes. You started the journey by encouraging me to believe everything is possible with God.

I want to express my most profound appreciation and thanks to my advisor, Dr. William H. Robinson, for his continual support and mentoring throughout my graduate program at Vanderbilt University. As your graduate student, you gave me a rare opportunity to experience the quality education that Vanderbilt University offers to prepare students for societal challenges. You are always part of my success stories, from the Vanderbilt University classroom to the Hardware Design Engineer at Intel Corporation. You always give me the liberty to choose what is best for my family and me without holding back your invaluable advice and valued suggestions. You made my time at Vanderbilt University to be a memorable period of my career. Your advice on the next step of my academic journey and career gave me the hope I needed. Thank you for giving me the strength to continue trying even when I was weak to proceed.

I express my appreciation and thanks to all the committee members, Dr. Ronald Schrimpf, Dr. Arthur Witulski, Dr. Brian Sierawski, and Dr. Hiba Baroud, who graciously agreed to be part of my dissertation journey. My encounter with each member influences my dissertation. Thank you for sharing your knowledge and giving me good memories in your different classes, either as a graduate student, Graduate Teaching Assistant (GTA), or while serving as a member of my dissertation committee. Learning Solid State Effects and Devices under Dr. Ronald Schrimpf gave me much information about semiconductor physics and devices. Part of the experience I used to secure my current job at Intel Corporation as a PCB Test Card and Board Design Engineer was gained by working as a two-time GTA for a Microelectronics class under Dr. Arthur Witulski. While performing my role as a GTA, I also learned microelectronics design. The experience of Verilog coding in ASIC design flow could be traced back to my handful of practical experiences with Dr. Brian Sierawski's FPGA class. It has been an area of significant research activity in my dissertation. Dr. Hiba Baroud's question opened my research experience to a broader area I had never considered. The ability to take research studies on uncertainty opens my mind to fresh ideas about addressing reliability in a multi-stage design flow. I appreciate your guidance, instruction, and encouragement. Despite your tight schedules, you are always available for thought-provoking conversations and discussions on fulfilling the critical areas of my research. Thank you for taking the time to answer my questions and provide vital research information that helps me in completing this dissertation.

I appreciate my wife, Titilayo, for her prayers, encouragement, and support. It is a blessing to have someone like you when the journey seems lonely. Our beautiful daughters, Precious and Isabella, and son, Nathaniel, are sources of encouragement and bountiful joy as their presence brings much-needed support to keep going. Thank you for being so supportive when I concentrate on research and a full-time job. Your encouragement, prayers, and support always motivate me to continue this journey.

This appreciation would only be complete by mentioning those who allowed me to stand on their shoulders to achieve all these academic qualifications. First, I appreciate Mrs. F. I. Moluga for giving me a platform that opened the door to my undergraduate education at Obafemi Awolowo University. The opportunity allowed me to meet many families and students who impacted my academic journey and turned out to be family till today. Second, I appreciate Mrs. Taiwo Lawal and my beautiful sisters, Olamide and Olabisi, for your steadfast support. Third, thank you to Mrs. Sowole, who turned me into a family member and opened her doors anytime I found my way to her house. Likewise, my dad and mum, Prof. and Mrs. Kehinde, whose kindness and hearts of love gave me the support and resources that I needed during my academic program at Obafemi Awolowo University (OAU). Both of you showed me the path of life and the genuine manifestation of the love of the Lord Jesus Christ through your personal life and examples. Finally, I appreciate my in-laws, Mr. and Mrs. Adebayo, who picked my academic progress as their own and stood up as parents for me. Both of you surprised me with your gestures. I believe God positioned each family member strategically in my academic journey because each of you surfaced when I needed divine help. You gave me a platform and opportunity to continue through your rare love, kindness, financial resources, and connections. You even stood in for me with your name. You all risked it for me! Indeed, it takes a village to raise a child! Thank you all.

Many friends made marks that cannot be forgotten. It is a pleasure to know you all. First, thank you, Mr. Segun Lawal, for your help during the early days of my University education. The platform you gave me helped me build on the gift of personal discovery. Second, I appreciate Mr. Fadimu Olatunde. I could recollect when we wrote TOEFL and GRE without understanding their usefulness. Thank you for being a source of encouragement during that period. Funny enough, the GRE results brought us to the United States for our Master's degree. Third, I will never forget my dear brothers, Sgt. Abiodun Olaluwe and Mr. Kehinde Oladeinde for their tremendous support and information provided at the beginning of the journey of my graduate studies. Thank Mr. David Adejuwon, Dr. Adebowale Shadare, Dr. Olokodana Olatunde, Mrs. Olaobaju Folake, Mr. Stephen Adebayo, and Dr. Adebisi Ojo Adedolapo for your support and love for the family. Our relationships on the Obafemi Awolowo University (OAU) campus have always been a blessed memory of my life. Fourth, I appreciate the love of fellow brothers and sisters (too many to list here) that we studied together at the Texas A&M University-Kingsville (TAMUK) and Prairie View A&M University (PVAMU). Finally, my colleagues at the Security and Fault Tolerance (SAF-T) research group, Bor-Tyng Lin and Hao Oiu, thank you for your support and for being part of my journey. Both of you are brothers that I can call on anytime with an assurance of a positive result. I appreciate and love every one of you!

Major work of my research work was only possible with the help of Vanderbilt University IT department personnel and an ISDE Engineer. I commenced the dissertation at a difficult and historical time – the COVID-19 pandemic period. Hence, I could not complete this work without the effort of Vanderbilt University IT engineers Roger Jones and Dane Vick. They helped to prepare the environment I needed for my dissertation work. In addition, ISDE Engineer Andrew Sternberg helped install the necessary academic tools and resources for my simulation activities. I appreciate your help.

I want to thank Intel Corporation for allowing working as an intern in 2016 and 2019 and eventually offering me a full-time position in 2020. The experience I gained during the internship gave me a technical simulation idea to publish my first conference paper. You gave me a rare platform that shaped my studies and career. Thank you for creating a diversity program with managers that passionate about diversity. Thank you, Jean-Marc Mensah and Adrian Rodrigues, for your effort to retain employees with diverse backgrounds. Jean-Marc Mensah gave me my first industrial experience when I taught all hope was lost. To my manager, Adrian Rodrigues, your technical guidance has greatly helped me in my career to deliver my task. Thank you for your support and understanding while completing this dissertation.

Finally, I thank the National Science Foundation (NSF) and Vanderbilt University through Provost's Graduate Fellowship for funding my academic program. Thank you for giving me the opportunity. I am sincerely grateful for the beautiful experience and opportunity.

## TABLE OF CONTENTS

|    |                                                                                                                                                | Page        |

|----|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| LI | IST OF TABLES                                                                                                                                  | ix          |

| LI | IST OF FIGURES                                                                                                                                 | X           |

| LI | IST OF ABBREVIATIONS                                                                                                                           | XV          |

| 1  | INTRODUCTION                                                                                                                                   | 1           |

|    | 1.1Research Contributions1.2Dissertation Organization                                                                                          |             |

| 2  | SINGLE-EVENT EFFECTS (SEE) MECHANISMS                                                                                                          | 6           |

|    | <ul> <li>2.1 Generation, Deposition, and Collection of Charge in Silicon Devices</li> <li>2.2 Linear Energy Transfer (LET)</li></ul>           | 8<br>8<br>9 |

| 3  | MASKING PRINCIPLES AND VARIATIONS                                                                                                              | 12          |

|    | <ul><li>3.1 Types of Masking</li></ul>                                                                                                         | 13          |

|    | in sub-65-nm bulk MOSFET Nodes                                                                                                                 | 22<br>24    |

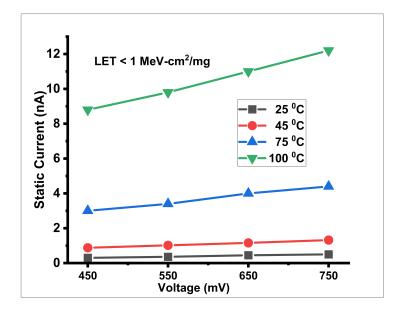

|    | <ul> <li>3.4 Validation of Simulation Results With the Experimental Data - Estimation of Static Current as a Function of Temperature</li></ul> | 24<br>25    |

| 4  | THE EFFECTS OF PROCESS, VOLTAGE, AND TEMPERATURE VARIATION ON PULSE PROPAGATION IN SYNTHESIZED DESIGNS                                         |             |

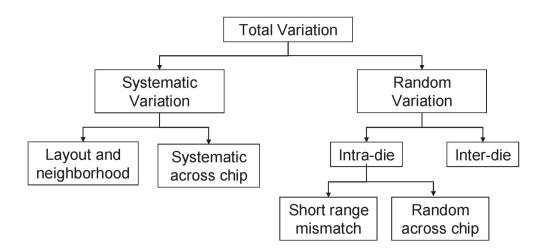

|    | <ul> <li>4.1 Process, Voltage, and Temperature Variations</li></ul>                                                                            |             |

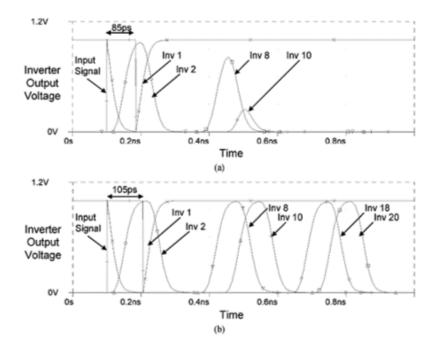

|    | 4.2 Pulse Broadening in Combinational Circuits with Standard Logic Cell Synthesis .                                                            | 32          |

|   |                                                                                                    | 4.2.1 PVT Variations on the Transient Pulses that Initially Pose no Significant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                           |

|---|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                    | Threat in Planar Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34                                                                                                                                                        |

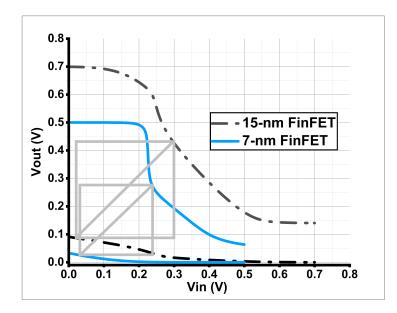

|   | 4.3                                                                                                | Evaluation of the Impact of Voltage and Temperature Variations on 7-nm FinFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                           |

|   |                                                                                                    | Technology Nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39                                                                                                                                                        |

|   | 4.4                                                                                                | Analysis of Pulse Broadening in 7-nm FinFET Technology Nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39                                                                                                                                                        |

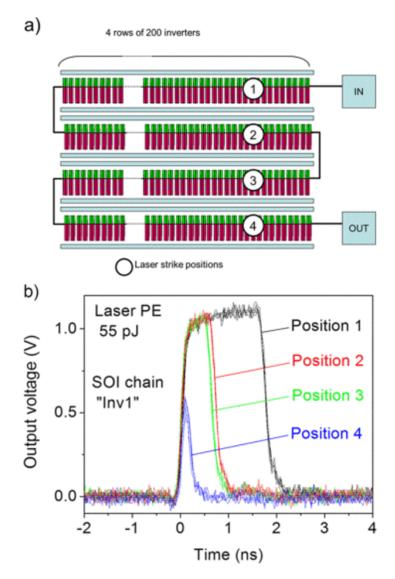

|   | 4.5                                                                                                | Validation of Simulation Results With the Experimental Data - Estimation of Pulsewic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | dth                                                                                                                                                       |

|   |                                                                                                    | due Elevated Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42                                                                                                                                                        |

|   |                                                                                                    | 4.5.1 Design Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                                                                                                        |

|   |                                                                                                    | 4.5.2 Discussion of Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44                                                                                                                                                        |

|   | 4.6                                                                                                | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44                                                                                                                                                        |

| 5 | TH                                                                                                 | HE IMPACT OF ADVANCED TECHNOLOGIES ON SRAM DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46                                                                                                                                                        |

|   | 5.1                                                                                                | SRAM Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46                                                                                                                                                        |

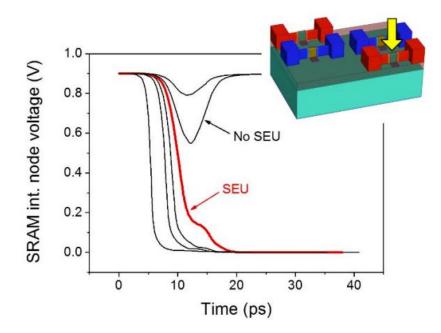

|   | 5.1                                                                                                | 5.1.1 Single-Event Upset (SEU) in SRAM Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48                                                                                                                                                        |

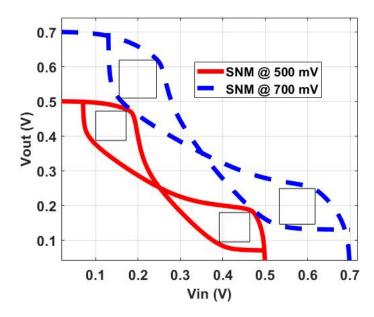

|   | 5.2                                                                                                | Simulation of the Impact of Scaling on Noise Margin, Threshold LET, and Critical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                                                                                                                                        |

|   | 5.2                                                                                                | Charge of an SRAM Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49                                                                                                                                                        |

|   |                                                                                                    | 5.2.1 Simulation Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4)<br>50                                                                                                                                                  |

|   |                                                                                                    | 5.2.1       Simulation Approach         5.2.2       Discussion of Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50<br>50                                                                                                                                                  |

|   | 5.3                                                                                                | Validation of Simulation Results with Experimental Data - Estimation of SER Us-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50                                                                                                                                                        |

|   | 5.5                                                                                                | ing a Model-Based Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53                                                                                                                                                        |

|   |                                                                                                    | 5.3.1 Design Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55<br>54                                                                                                                                                  |

|   |                                                                                                    | 5.3.2 Discussion of Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54                                                                                                                                                        |

|   | 5.4                                                                                                | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54<br>56                                                                                                                                                  |

|   | Э.т                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50                                                                                                                                                        |

|   |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                           |

| 6 | M                                                                                                  | ITIGATION TECHNIQUES FOR MINIMIZING OR ELIMINATING THE RADI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ATION-                                                                                                                                                    |

| 6 |                                                                                                    | ITIGATION TECHNIQUES FOR MINIMIZING OR ELIMINATING THE RADI<br>DUCED TRANSIENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ATION-<br>57                                                                                                                                              |

| 6 | IN                                                                                                 | DUCED TRANSIENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57                                                                                                                                                        |

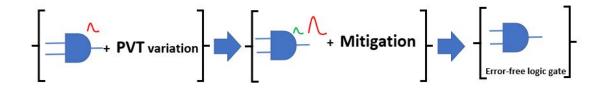

| 6 |                                                                                                    | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>57</b><br>57                                                                                                                                           |

| 6 | IN                                                                                                 | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1         Standard Cell Strength Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>57</b><br>57<br>57                                                                                                                                     |

| 6 | IN                                                                                                 | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1         Standard Cell Strength Approach         6.1.2         Selective Hardening Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>57</b><br>57<br>57<br>58                                                                                                                               |

| 6 | <b>IN</b><br>6.1                                                                                   | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1         Standard Cell Strength Approach         6.1.2         Selective Hardening Approach         6.1.3         Layout Placement Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>57</b><br>57<br>58<br>58                                                                                                                               |

| 6 | IN                                                                                                 | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1         Standard Cell Strength Approach         6.1.2         Selective Hardening Approach         6.1.3         Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57<br>57<br>58<br>58<br>58<br>59                                                                                                                          |

| 6 | <b>IN</b><br>6.1                                                                                   | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1         Standard Cell Strength Approach         6.1.2         Selective Hardening Approach         6.1.3         Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1         Mitigation of Pulse Broadening Amplified by PVT Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57<br>57<br>58<br>58<br>58<br>59<br>60                                                                                                                    |

| 6 | <b>IN</b><br>6.1                                                                                   | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57<br>57<br>58<br>58<br>59<br>60<br>64                                                                                                                    |

| 6 | IN<br>6.1<br>6.2                                                                                   | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM                                                                                                                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>58<br>58<br>59<br>60<br>64<br>68                                                                                                              |

| 6 | <b>IN</b><br>6.1                                                                                   | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewice                                                                                                                                                                                                                                                                                                                               | 57<br>57<br>58<br>58<br>58<br>59<br>60<br>64<br>68<br>dth                                                                                                 |

| 6 | IN<br>6.1<br>6.2                                                                                   | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewid as a Function of LET                                                                                                                                                                                                                                                                                                           | 57<br>57<br>58<br>58<br>59<br>60<br>64<br>68<br>dth<br>69                                                                                                 |

| 6 | IN<br>6.1<br>6.2                                                                                   | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewid as a Function of LET         6.3.1       Design Approach                                                                                                                                                                                                                                                                       | 57<br>57<br>58<br>58<br>59<br>60<br>64<br>68<br>dth<br>69<br>69                                                                                           |

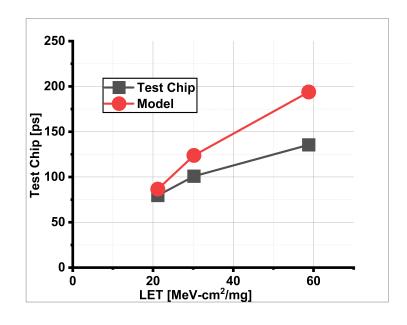

| 6 | <ul><li>IN</li><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                           | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewid as a Function of LET         6.3.1       Design Approach         6.3.2       Discussion of Results                                                                                                                                                                                                                             | 57<br>57<br>58<br>58<br>59<br>60<br>64<br>68<br>dth<br>69<br>69<br>71                                                                                     |

| 6 | IN<br>6.1<br>6.2                                                                                   | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewid as a Function of LET         6.3.1       Design Approach                                                                                                                                                                                                                                                                       | 57<br>57<br>58<br>58<br>59<br>60<br>64<br>68<br>dth<br>69<br>69                                                                                           |

|   | <ul> <li>IN</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul>                         | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewice as a Function of LET         6.3.1       Design Approach         6.3.2       Discussion of Results         Chapter Summary       Chapter Summary                                                                                                                                                                              | 57<br>57<br>58<br>58<br>59<br>60<br>64<br>68<br>dth<br>69<br>69<br>71<br>71                                                                               |

| 6 | <ul> <li>IN</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>CC</li> </ul>             | DUCED TRANSIENTS         Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewide as a Function of LET         6.3.1       Design Approach         6.3.2       Discussion of Results         Chapter Summary       Chapter Summary                                                                                                                                                                             | 57<br>57<br>58<br>58<br>59<br>60<br>64<br>68<br>dth<br>69<br>69<br>71<br>71                                                                               |

|   | <ul> <li>IN</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>CC</li> </ul>             | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewice as a Function of LET         6.3.1       Design Approach         6.3.2       Discussion of Results         Chapter Summary       Chapter Summary                                                                                                                                                                              | 57<br>57<br>58<br>58<br>59<br>60<br>64<br>68<br>dth<br>69<br>69<br>71<br>71                                                                               |

|   | <ul> <li>IN</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>CC</li> </ul>             | DUCED TRANSIENTS         Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewide as a Function of LET         6.3.1       Design Approach         6.3.2       Discussion of Results         Chapter Summary       Chapter Summary                                                                                                                                                                             | 57<br>57<br>58<br>58<br>59<br>60<br>64<br>68<br>dth<br>69<br>69<br>71<br>71                                                                               |

|   | <ul> <li>IN</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>CC</li> <li>RC</li> </ul> | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewid as a Function of LET         6.3.1       Design Approach         6.3.2       Discussion of Results         Chapter Summary       Chapter Summary                                                                                                                                                                               | <b>57</b><br><b>57</b><br><b>58</b><br><b>59</b><br><b>60</b><br><b>64</b><br><b>68</b><br><b>dth</b><br><b>69</b><br><b>71</b><br><b>71</b><br><b>72</b> |

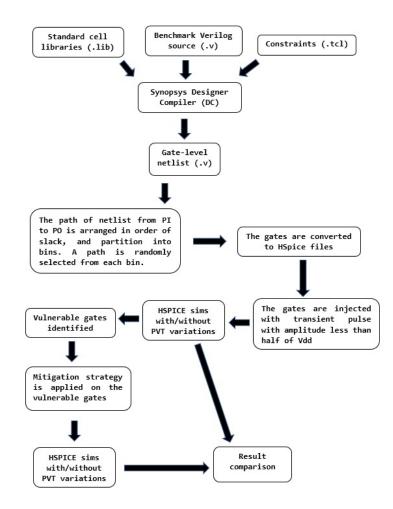

|   | <ul> <li>IN</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>CC</li> <li>RC</li> </ul> | <b>DUCED TRANSIENTS</b> Approaches to Mitigate Propagating Transients         6.1.1       Standard Cell Strength Approach         6.1.2       Selective Hardening Approach         6.1.3       Layout Placement Approach         Improvement of Masking Ability of Logical Gates Using 45nm Bulk Technology         6.2.1       Mitigation of Pulse Broadening Amplified by PVT Variations         6.2.2       Electrical Masking Improvement with Standard Logic Cell Synthesis         6.2.3       Minimize the Single Event Upset in SRAM         Validation of Simulation Results With the Experimental Data - Estimation of Pulsewid as a Function of LET         6.3.1       Design Approach         6.3.2       Discussion of Results         Chapter Summary       Chapter Summary         OST-TO-RELIABILITY TRADE-OFF TECHNIQUES FOR IMPROVING THE DISUSTNESS OF ADVANCED TECHNOLOGY DESIGNS         Analysis of Electrical Masking of Gate(s) Within Netlists | <b>57</b><br><b>57</b><br><b>58</b><br><b>59</b><br><b>60</b><br><b>64</b><br><b>68</b><br><b>dth</b><br><b>69</b><br><b>71</b><br><b>71</b><br><b>72</b> |

| Re | eferen | ces    |                                     | 0 |

|----|--------|--------|-------------------------------------|---|

| 8  | Su     | mmary  |                                     | 8 |

|    | 7.4    | Chapte | r Summary                           | 6 |

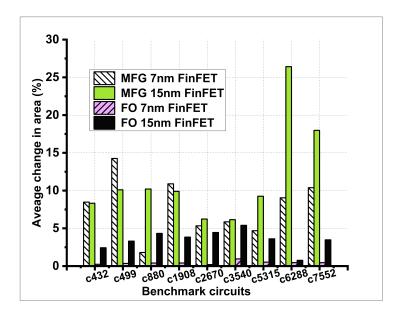

|    |        | 7.3.2  | One-to-Many Fanout Approach         | 9 |

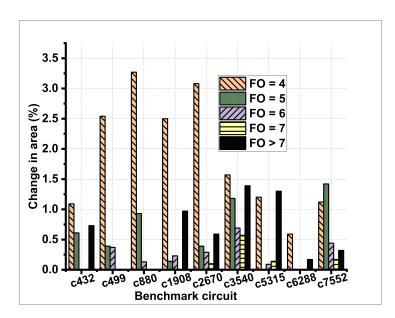

|    |        | 7.3.1  | Most Frequent Gates (MFG) Approach  | 7 |

|    | 7.3    | Analys | is of Cost-to-Reliability Trade-Off | 7 |

| A | Lat  | ex script                                                                                      | 97 |

|---|------|------------------------------------------------------------------------------------------------|----|

|   | A.1  | Latex script for creating the flow of the dissertation work in chapter 7                       | 97 |

| B | Pytl | hon script                                                                                     | 99 |

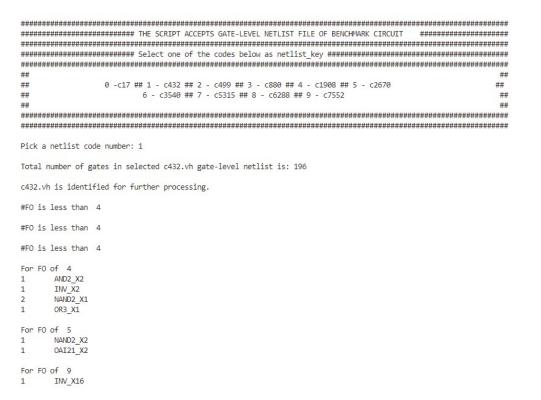

|   | B.1  | Python script to identify the fanout gates in a synthesis file shown in Table 7.3 $\therefore$ | 99 |

### LIST OF TABLES

| Table      | ]                                                                                                                                                                                                                                                                  | Page     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1        | The experimental data from [48] with an average charge collection efficiency, $\frac{Q_{coll}}{Q_{gen}}$ of 34% of the total charge deposited                                                                                                                      | 7        |

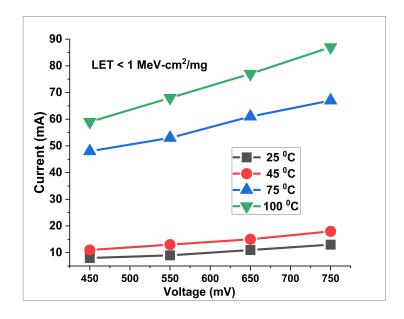

| 3.1<br>3.2 | Technology models and the number of inverters in the technology-dependent pipeline depth. The technology modes are obtained from Arizona State University's (ASU) Predictive Technology Model (PTM)                                                                | 16<br>23 |

| 4.1        | EPFL benchmark circuits with the information about the reference number, num-                                                                                                                                                                                      |          |

|            | ber of gates, and the area of synthesized circuits                                                                                                                                                                                                                 | 35       |

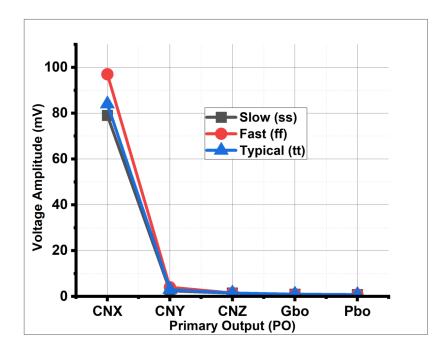

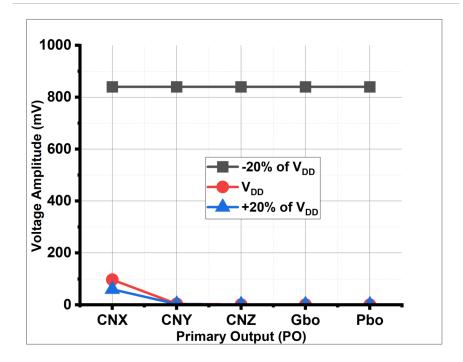

| 4.2        | The digital logic gates simulated to identify the most vulnerable gates based on<br>the resulting radiation-induced voltage waveform amplitude. The worst cases of<br>PVT variations on the vulnerable gates in the <i>Sine circuit</i> are reported in this table | . 38     |

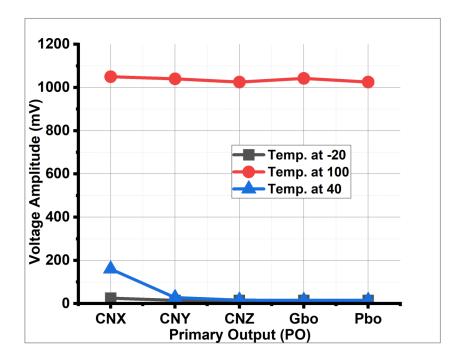

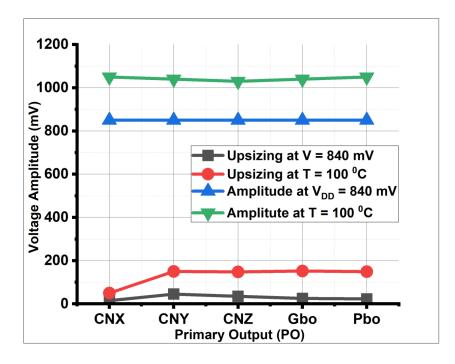

| 6.1        | Worst cases of PVT variations on the vulnerable gates in the <i>Sine circuit</i> using 45nm bulk technology. Vulnerable gates aid the propagation of radiation-induced transient by increasing the properties of the propagating transient.                        | 61       |

| 6.2        | The EPFL benchmark circuits with synthesized and vulnerable gates. The simulation column shows the percentage changes in the area after the mitigation approach is applied.                                                                                        | 62       |

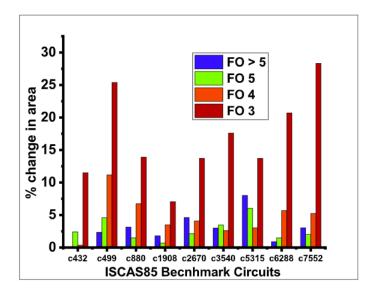

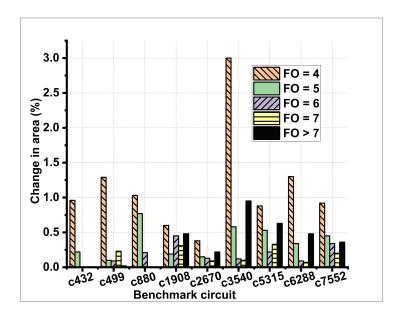

| 7.1        | The ISCAS85 benchmark circuits used in this dissertation work. Each circuit is synthesized to gate-level netlists using 7-nm FinFET, 15-nm FinFET, and 45-nm                                                                                                       |          |

| 7.2        | MOSFET technologies                                                                                                                                                                                                                                                | 76       |

| 1.2        | level netlist.                                                                                                                                                                                                                                                     | 78       |

| 7.3        | Gates with fan-out (s) in gate-level netlists of ISCAS'85 benchmark circuits us-<br>ing 7-nm FinFET, 15nm FinFET, and 45-nm MOSFET technologies.                                                                                                                   | 83       |

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

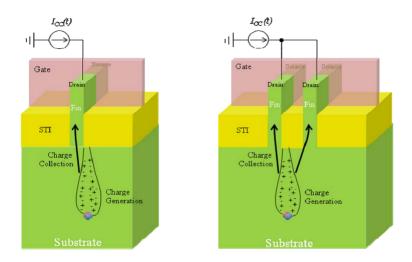

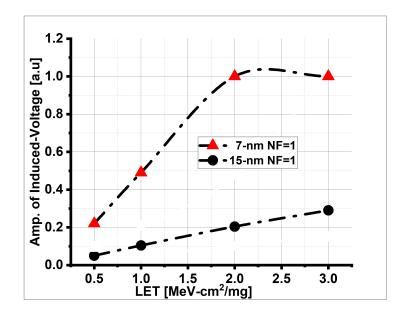

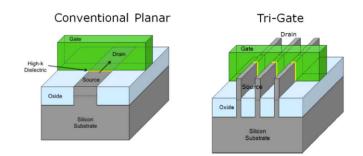

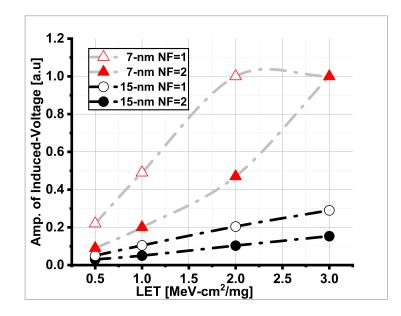

| 1.1    | Illustration of a simulation for the charge collection efficiency between (a) single-<br>fin and (b) double-fin structures as shown in [39]. The charge collection effi-<br>ciency depends on the sensitive volume and the number of fins                                                                                                                                                                                   | 2    |

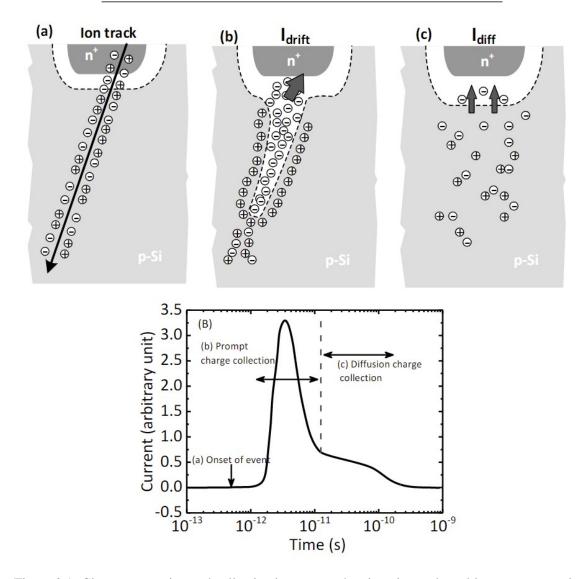

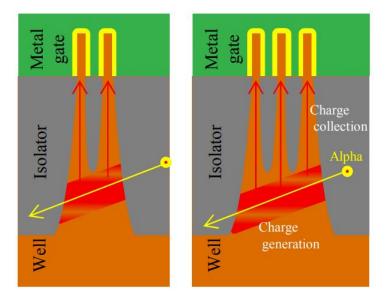

| 2.1    | Charge generation and collection in a reversed pn junction and resulting current transient caused by the movement of high-energy particle ions. [7]                                                                                                                                                                                                                                                                         | 7    |

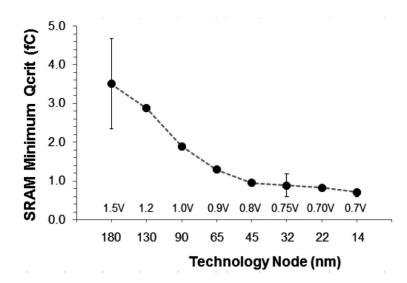

| 2.2    | The experimental data of the minimum critical charges for SRAM devices at                                                                                                                                                                                                                                                                                                                                                   |      |

| 2.3    | nominal technology voltages reported in [65]                                                                                                                                                                                                                                                                                                                                                                                |      |

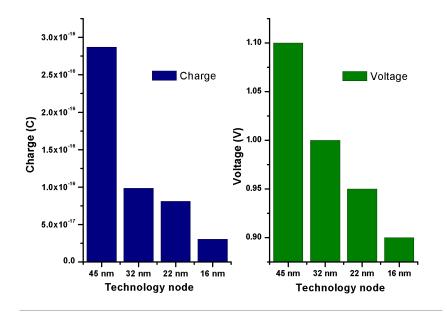

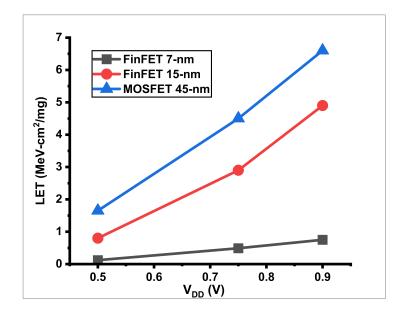

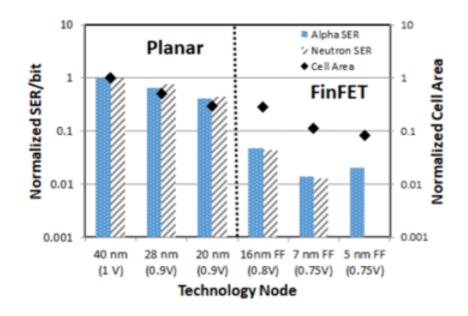

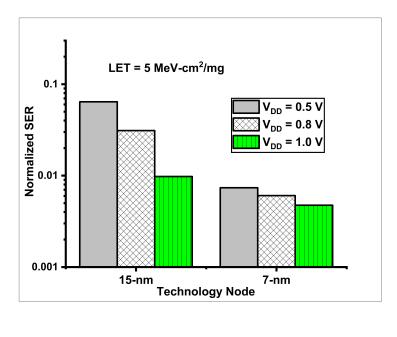

| 3.1    | The effect of scaling on the critical charge and the nominal voltage of 45 nm, 32 nm, 22 nm, and 16 nm technologies from the Predictive Technology Model (PTM) of Arizona State University (ASU) [1]. The critical charge and the nominal voltage reduce as technologies scale [54].                                                                                                                                        | 13   |

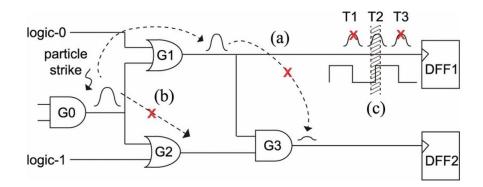

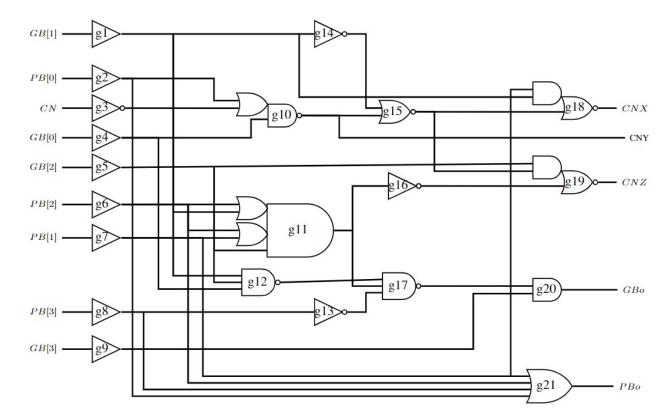

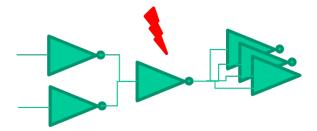

| 3.2    | Logic circuit implementation used to explain the logical, timing, and electrical masking principles. Gates <i>G0</i> is the source of the impact. Radiation-induced transients traverse to other gates through its fanouts [17]. The tendency of the induced transient to propagate through the gates varies with the masking under consideration.                                                                          |      |

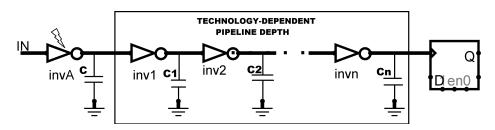

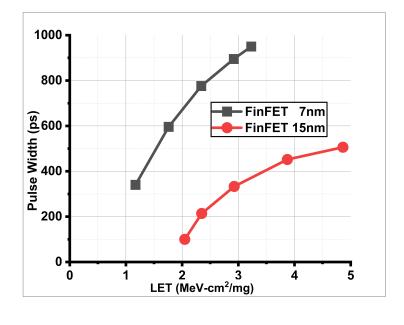

| 3.3    | Technology-dependent pipeline depth for inverter chain simulations. The number of inverters depends on the technology, as shown in Table 3.1. The minimum length corresponds to the technology, and the number of inverters is determined using the scaling factor $k = 0.7$ . In a technology-dependent pipeline depth, the number of gates increases.                                                                     |      |

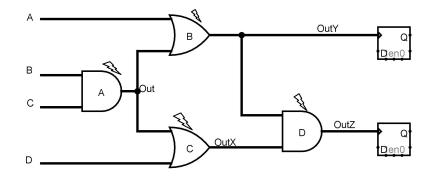

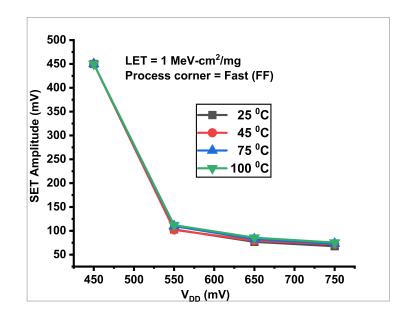

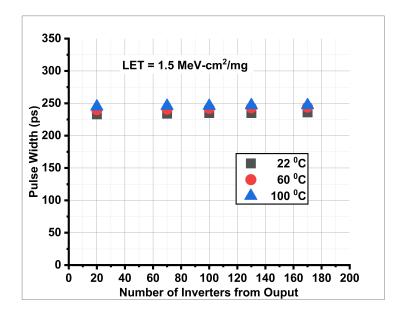

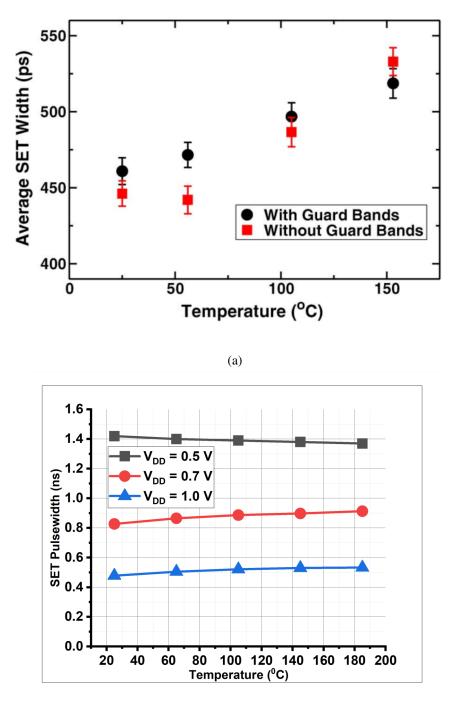

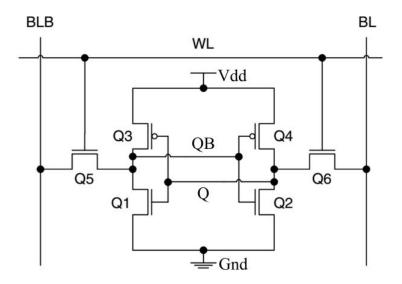

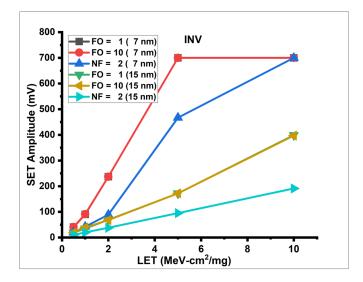

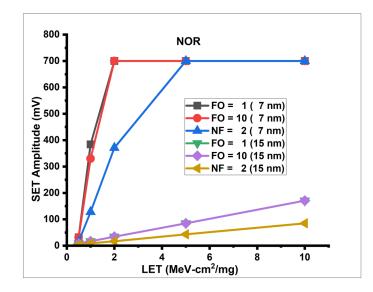

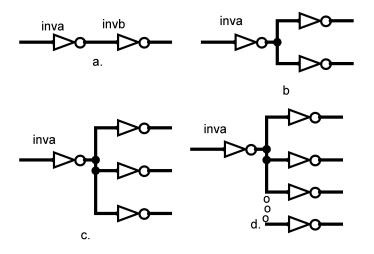

| 3.4    | Logic implementation to show the effects of different technologies and electrical masking under variations of voltage and temperature [33]. Logic gates with better nodal capacitance and electrical properties weaken the propagating radiation-induced transient.                                                                                                                                                         | 10   |

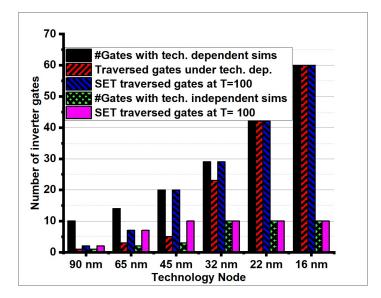

| 3.5    | The effect of technology and temperature on the number of inverters required<br>for masking the injected fault. For easy analysis, the same transient fault is<br>applied. With an increase in temperature, the number of inverters traverses by<br>the propagating transient increases in 22 nm and 16 nm nodes in a technology-                                                                                           |      |

| 3.6    | dependent case                                                                                                                                                                                                                                                                                                                                                                                                              |      |

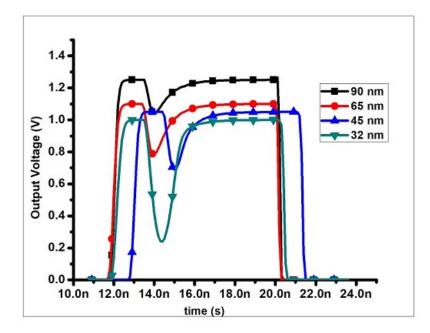

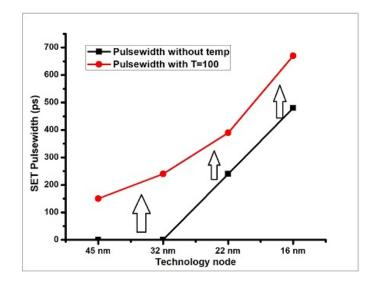

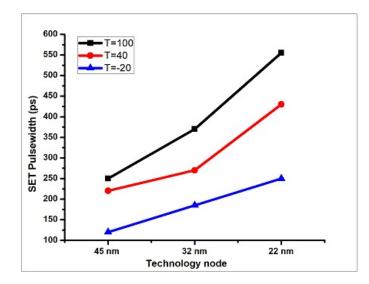

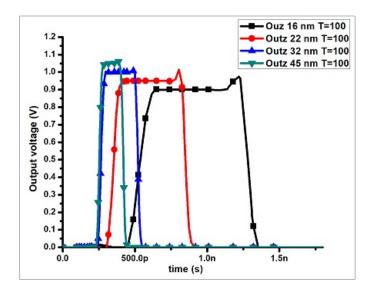

| 3.7    | Effect of different technology on induced transient propagation of a logic circuit implementation in Fig. 3.4. While it is fully masked in 45 nm and 32 nm due to an increase in nominal voltage, $V_{DD}$ , the transient propagates with an increase in pulsewidth in 22 nm and 16 nm nodes. With T = $100^{\circ}C$ , there is an increase in the pulsewidth for all the technology models. Increased temperature causes |      |

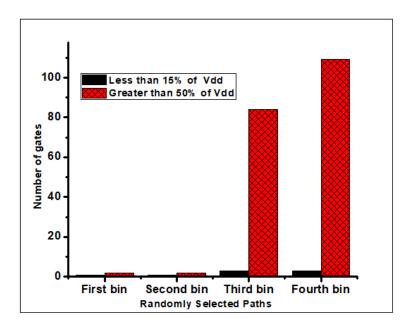

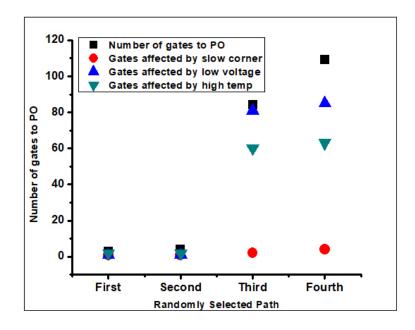

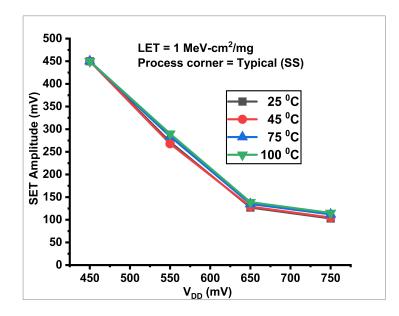

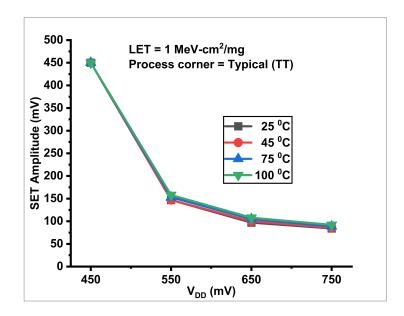

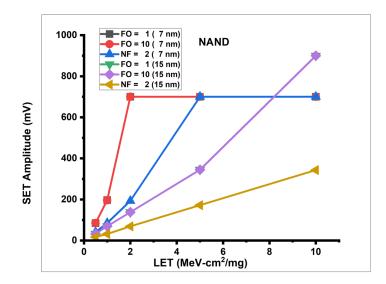

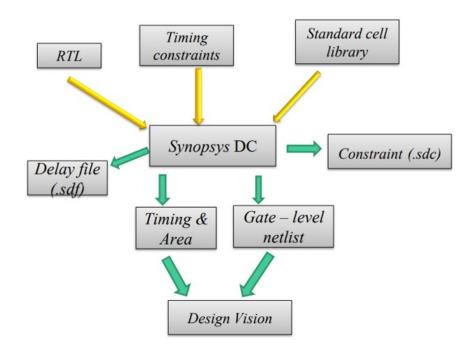

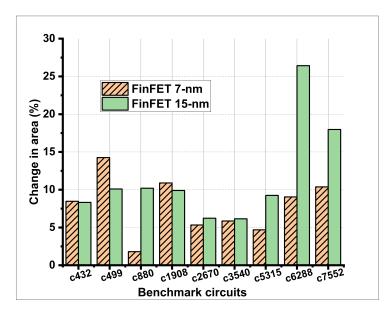

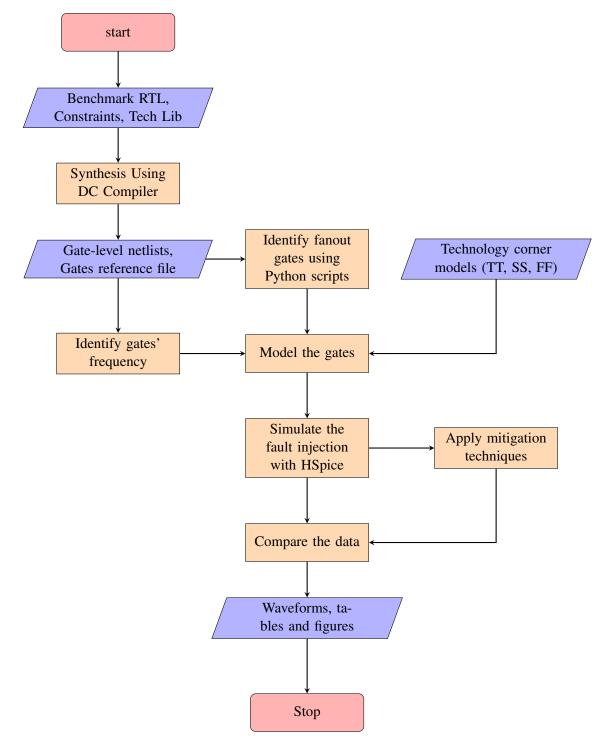

|        | charge carriers' lower mobility, leading to a lower drive current.                                                                                                                                                                                                                                                                                                                                                          | 20   |