# THE SPECIFICATION AND IMPLEMENTATION OF A MODEL OF COMPUTATION

By

Ryan Thibodeaux

Thesis

Submitted to the Faculty of the Graduate School of Vanderbilt University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

Electrical Engineering

May, 2008

Nashville, Tennessee

Approved:

Professor Gábor Karsai

Professor János Sztipanovits

To my family, for your unwavering love and support through all my endeavors.

# **ACKNOWLEDGEMENTS**

This work was sponsored by the Air Force Office of Scientific Research, USAF, under grant/contract number FA9550-06-0312 and the NSF/ITR, titled Foundations of Hybrid and Embedded Software Systems, award number CCR-0225610.

# TABLE OF CONTENTS

|         | F                                                                            | age                                                                  |

|---------|------------------------------------------------------------------------------|----------------------------------------------------------------------|

| ACKNO   | WLEDGEMENTS                                                                  | iii                                                                  |

| LIST OF | F TABLES                                                                     | vi                                                                   |

| LIST OF | F FIGURES                                                                    | vii                                                                  |

| LIST OF | F ABBREVIATIONS                                                              | viii                                                                 |

| Chapter |                                                                              |                                                                      |

| I.      | INTRODUCTION                                                                 | 1                                                                    |

| II.     | BACKGROUND: DEVS MODELING FORMALISM                                          | 5<br>5<br>6<br>7                                                     |

| III.    | DEVS MODEL OF A TIME-TRIGGERED PLATFORM  Time-Triggered Model of Computation | 8<br>11<br>11<br>15<br>17                                            |

| IV.     | AN OFF-THE-SHELF PLATFORM IMPLEMENTATION                                     | 20<br>20<br>23<br>26<br>26<br>27<br>31<br>33<br>35<br>39<br>40<br>41 |

|         | Timing Properties of FRODO                                                   | 43<br>44                                                             |

| V.     | USE CASE: TRIPLE-MODULAR REDUNDANCY       | 47 |

|--------|-------------------------------------------|----|

|        | Triple-Modular Redundancy                 | 47 |

|        | Experimental Description                  | 48 |

|        | DEVS Model and Simulation of a TMR System | 49 |

|        | Implementation of TMR on FRODO            | 52 |

|        | Comparing Results of DEVS and FRODO       | 55 |

|        | Summary                                   | 57 |

| VI.    | CONCLUSION                                | 60 |

|        | Future Work                               | 61 |

| BIBLIC | OGRAPHY                                   | 63 |

# LIST OF TABLES

| Table |                                                                             | Page |

|-------|-----------------------------------------------------------------------------|------|

| 1.    | Message communication timing properties                                     | 37   |

| 2.    | Summary of timing properties for current implementation                     | 46   |

| 3.    | Scheduled messages and tasks for TMR compass example (hyperperiod of 150ms) |      |

| 4.    | Segment of DEVS++ simulation output for TMR compass example                 | 53   |

| 5.    | FRODO output                                                                | 54   |

# LIST OF FIGURES

| Figure |                                                                   | Page |

|--------|-------------------------------------------------------------------|------|

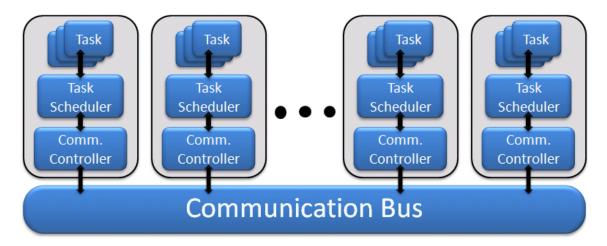

| 1.     | High-level architectural view of a TT system                      | 12   |

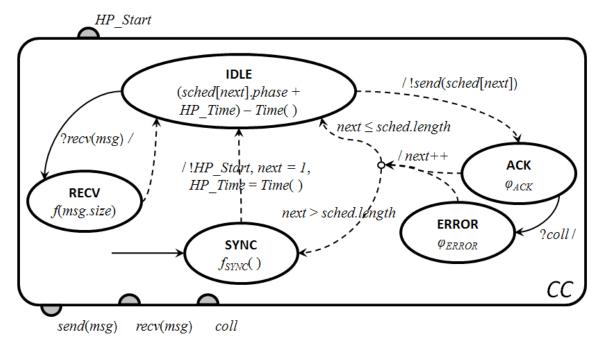

| 2.     | DEVS model of the time-triggered communication controller         | 14   |

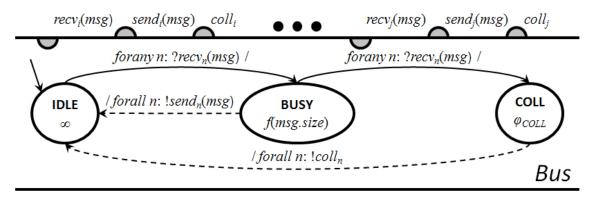

| 3.     | DEVS model of the communication bus                               | 14   |

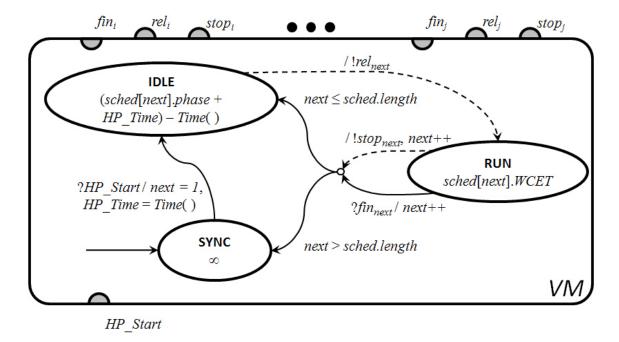

| 4.     | DEVS model of the time-triggered task scheduler                   | 16   |

| 5.     | DEVS model of a time-triggered task                               | 17   |

| 6.     | Activity timeline over the execution of a time-triggered schedule | 17   |

| 7.     | Coupled DEVS model of a TT MoC equipped node and the bus          | 19   |

| 8.     | System architecture of a single node                              | 22   |

| 9.     | General implementation configuration of nodes for experiments     | 24   |

| 10.    | Node synchronization process viewed from the bus                  | 28   |

| 11.    | Hyperperiod synchronization across four nodes                     | 30   |

| 12.    | Message communication timing properties                           | 38   |

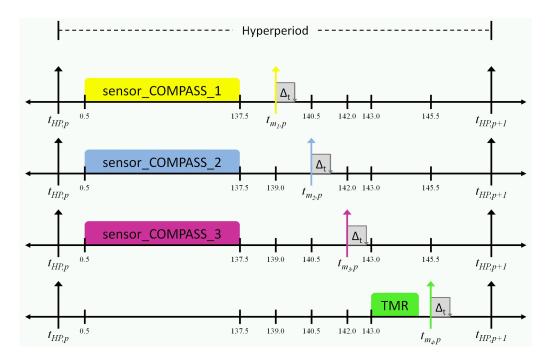

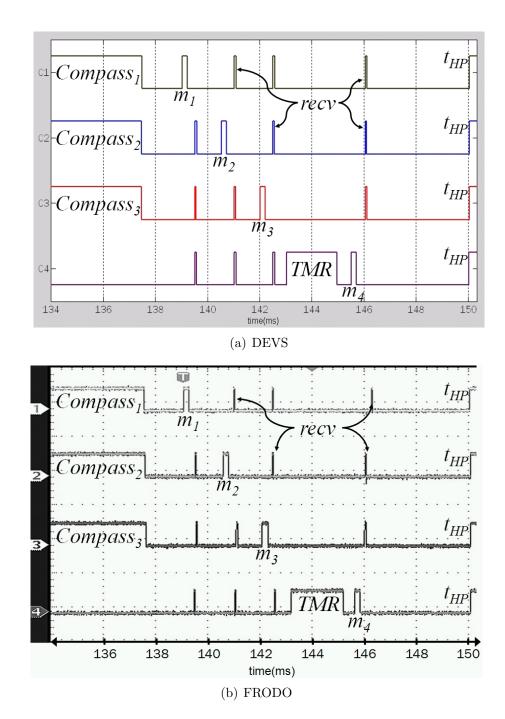

| 13.    | Timeline of events for TMR compass example                        | 51   |

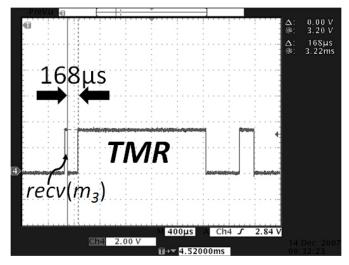

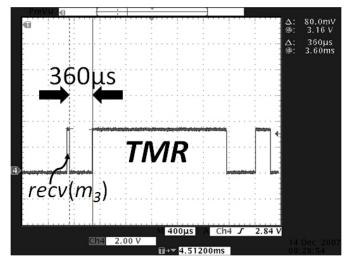

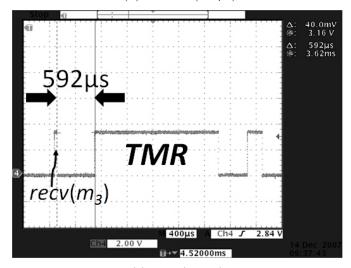

| 14.    | Varying response times to message "m3" on node "C4"               | 56   |

| 15.    | Execution traces of TMR example                                   | 58   |

# LIST OF ABBREVIATIONS

API Application Programming Interface

CNI Communication Network Interface

DEVS Discrete Event System Specification

ET Event-Triggered

MoC Model of Computation

TMR Triple-Modular Redundancy

TTMoC Time-Triggered Model of Computation

TT Time-Triggered

TTA Time-Triggered Architecture

TTP Time-Triggered Protocol

VM Virtual Machine

#### CHAPTER I

#### INTRODUCTION

The integration of computing devices into more and more of our surrounding technologies has been ongoing over the past two decades. The continuing trend in technologydriven fields (e.g. automotive industry, consumer electronics, automation, etc.) is to increase the available computational resources and software-based implementation in order to add functionality and lower costs. Unlike typical software systems targeted for personal computers and web-based applications, these embedded systems are subjected to physical constraints as a result of their necessary interaction with the physical environment and/or the limited availability of computational, communication, and physical (e.g. power) resources. This interplay between the continuous-time dynamics of the physical world and the discrete-time computational model of software only complicates the design process for embedded systems. Consequently, embedded software systems designers have tried to construct reasoning/modeling frameworks that leverage techniques from both continuous-time and discrete-time systems in order to alleviate some of the design challenges. Ultimately, any approach intended to design, model, and analyze embedded software systems can become an accepted technology only if it is adaptable to a variety of application domains and formal enough to provide logical assurances.

Typically in the design of software systems, partitioning a functional software specification into distinct modules or components is often considered a requirement of "good" software engineering practices. Each component provides some functional or behavioral utility, and the composition of the components across well-defined connections/interfaces is intended to result in the desired system behavior. Deriving any notion of the overall behavior from component-level descriptions is contingent upon an established understanding of the rules that govern the how the components are connected, i.e. the structure of the system and the legal interaction patterns between components that occur over time (the operational semantics). Generally, a collection of these rules targeted for a set of systems that share a common syntax is called a Model of Computation (MoC) [7].

Considering the MoC attributed to a design is fundamental to understanding the behaviors that can and will emerge during system execution, providing an unambiguous specification of the MoC and its influence over components is pivotal to successfully modeling run-time behaviors. Various tools and approaches have been developed to tackle the issue of describing MoC-s, each of which offers its own strengths and weaknesses depending on its underlying objective: mathematical rigor, simulation, verification, etc. We contend that all of these objectives are commendable and important to understanding embedded software systems; however, we hold that it should be primary to provide designers a mathematically precise reasoning framework that considers the operational description of a system fundamental to effective software engineering. Furthermore, effectively communicating the consequences of a component-based implementation over a chosen MoC requires that a modeling framework must be able to express characteristics inherently present in embedded systems, mainly heterogeneous classes of behaviors and temporally-aware computing.

Given the wide range of applications and complexity of embedded systems, it should come as no surprise that one computational model cannot be universally applied to describe all system behaviors and events. Instead, designers rely on a multitude of MoCs for capturing different types of components and interactions. In the most general case, how and when components logically execute and communicate with each other can be described by two types of responses: event-triggered (ET) and time-triggered (TT). ET responses are reactive: the occurrence of a discrete event (e.g. the arrival of a message, an interrupt request for service, or changing a variable) elicits a response from the system as fast as possible or with some measurable quality of service. Conversely, TT systems initiate an event or activity only at predefined moments of time laid out according to a fixed schedule. The synchronization of TT events across components implies they maintain an agreement on the current state and ongoing progression of "system" time. ET systems are much more unpredictable, whereas TT systems are fundamentally deterministic. Unfortunately, most implementations of embedded systems cannot be classified as strictly ET or TT, but contain a mix of both depending on the

function of a component or set of components (a subsystem). Obviously, the applicability of an approach for modeling embedded software hangs on its ability to sufficiently capture at least these general classes of behaviors (separately and intermixing them), and it must provide a mechanism to account for the continuous progression of time beyond discrete incremental changes of a fixed-resolution counter.

The need for capturing properties and characteristics of a MoC that greatly affect the run-time execution of a system has underscored the stated desirables of a modeling framework thus far. Attention to these implementation-specific details is often captured in a system model commonly referred to as an execution framework or platform. A platform provides the operational services dictated by the chosen MoC that orchestrate the behaviors and interactions of the constituent software components during execution. In embedded software systems, platforms can be real-time operating systems, middleware frameworks, component execution frameworks, or kernels. Many abstract specifications of software systems and MoC-s try to avoid if not outright reject the need to model implementation-specific details (e.g. protocols, timing, component scheduling, and synchronization mechanisms); however, there are specific embedded software domains where the precise knowledge and understanding of a platform and its execution logic is paramount to producing the desired system with a level of certainty regarding its performance and reliability. One such domain of systems is high-confidence real-time systems, where suboptimal performance or failures can result in loss of human life or property (e.g. flight control and avionics systems, automotive applications, robotics, manufacturing, health and safety monitoring, etc.).

## Thesis Objective

Considering the behavioral and temporal challenges prevalent throughout embedded software system design, we propose the development of a modeling framework that can describe various MoC-s and their influences on component-based software systems with a focus on their operational behaviors that unfold over the progression of time. We require the use of a modeling language that is not only mathematically precise and conducive

to reasoning techniques but also fully capable of expressing a system's state evolution as a result of the occurrence of events and the ongoing progression of time. Our proposed selection for the modeling approach, DEVS [10, 11], further extends our framework with the capability to rapidly prototype and simulate a modeled system (components, connections, and MoC(-s)) such that designers can evaluate resulting execution traces for logical and temporal correctness.

Furthermore, we will illustrate how to use the proposed modeling framework to develop an implementation of a strictly TT platform intended for deploying distributed real-time systems. A representative model of the platform will be constructed and then used to derive the execution logic of the platform, which will be implemented on off-the-shelf software and hardware components. We envision this exercise will show that modeling an execution platform intended for implementation has many benefits and consequences: it eases the process of developing the implementation by equipping the designer with a design blueprint, it allows evaluating the correctness of the implementation against the reference behaviors of the model, it provides system designers a framework to evaluate how MoC-s determine run-time behaviors of an application, and benchmarks/properties of the implementation can be integrated into the platform model to improve the fidelity of timed simulations.

#### CHAPTER II

#### BACKGROUND: DEVS MODELING FORMALISM

The Discrete Event System Specification (DEVS) formalism [10, 11] is a mathematical language intended to unambiguously describe time-driven systems. A DEVS system is characterized by states, input/output events, a time base, and functions that describe the evolution of the system state based on the occurrence of events and the passage of time. Like other discrete event formalisms, DEVS captures the changing variable values (event occurrences) over well-defined time segments; however, unlike most discrete event simulators, DEVS allows the instantaneous occurrence of events, i.e. the length of the time segments between events is variable (over continuous time) instead of over fixed time steps [12]. Initially, simpler (atomic) models are created to describe the fundamental dynamic behaviors of a system, and then larger (coupled) models are constructed from a network of the simpler models to produce a complete system specification.

#### **Atomic DEVS Models**

An Atomic DEVS model is represented by the 7-tuple structure [2]

$$M_A = \langle X, Y, S, s_0, \tau, \delta_x, \delta_y \rangle$$

, where

- X is a set of input events.

- Y is a set of output events.

- S is a finite set of discrete states.

- $s_0$  is the initial state.

- τ: S → R<sup>+</sup><sub>0,∞</sub> is the time advance function. It returns a non-negative real number (the lifespan of the current state) that indicates how long the system can remain in the current state without the arrival of new input events.

- $\delta_x: Q \times X \to S$  is the input transition function where

$$Q = \{(s, t_s, t_e) | s \in S, t_s = \tau(s), t_e = [0, t_s] \}$$

and  $t_e$  is the elapsed time since the last entering of state s.

•  $\delta_y: S \to Y \times S$  is the output transition function. It specifies the next internal state of the system and the generated output events whenever the lifespan of the current state expires.

Time is a continuous variable in all DEVS models with a constant rate of one. Note, this does not imply that the lifespan of a state,  $\tau(s)$ , is also a continuous variable; instead, the lifespan is given only as a result of evaluating  $\delta_x$  or  $\delta_y$ , i.e. upon entering a state.

Two types of transitions describe the evolution of state for a given atomic DEVS model: internal and external transitions. *Internal* transitions occur when the lifespan of a state is reached and result in entering some new state and the generation of some set of output events given by  $\delta_y$ . *External* transitions result from the arrival of a new input event that triggers a state change under the enabling conditions given by  $\delta_x$ . External transitions occur instantaneously and generate no output events.

#### Coupled DEVS Models

Like other automata-based modeling languages, constructing complex systems using one atomic or flat DEVS model is possible but very tedious and cumbersome. This approach is not only laborious but also prone to error, lacks generality, and most likely results in an incomprehensible system specification. DEVS helps steer designers away from this path by promoting the use of hierarchical and modular model specifications within its generalized framework. A large DEVS model can be constructed by coupling or composing simpler DEVS models across well-defined interfaces. Through this coupling, events generated from one subsystem model can be passed "horizontally" (between peer systems) and "vertically" through the hierarchy to other subsystem models (where subsystems are atomic or coupled models as well).

A Coupled DEVS model is given by the 7-tuple structure [2]

$$M_C = \langle X, Y, D, \{M_i\}, EIC, ITC, EOC \rangle$$

, where

- $\bullet$  X is a set of input events.

- Y is a set of output events.

- *D* is a set of names of sub-components.

- $\{M_i\}$  is a set of DEVS models where  $i \in D$ .  $M_i$  can be an atomic or coupled DEVS model.

- $EIC \subseteq X \times \bigcup_{i \in D} X_i$  is a set of external input couplings where  $X_i$  is the set of input events of  $M_i$ .

- $ITC \subseteq \bigcup_{i \in D} Y_i \times \bigcup_{i \in D} X_i$  is a set of internal couplings where  $Y_i$  is the set of output events of  $M_i$ .

- $EOC \subseteq \bigcup_{i \in D} Y_i \times Y$  is a set of external output couplings.

The semantics for the progression of time and state evolution within a coupled DEVS model follow directly from the semantics of an atomic DEVS model. Whenever  $M_C$  receives an input event, the coupled DEVS transmits the input event to the sub-components through the set of external input couplings, and when a sub-component produces an output event, the coupled DEVS transmits the output event to the other sub-components through the set of internal couplings and it also produces an output event of  $M_C$  through the set of external output couplings.

# Summary

DEVS provides a general modeling formalism for describing discrete-event systems with semantic constructs for physical time, discrete events, discrete states, and hierarchical composition of models. Accordingly, its wide-scale applicability, mathematical underpinnings, and model simulation support provided by various tools and libraries (e.g. DEVS++ [2], DEVSJAVA [12], Adevs [8], etc.) make it a viable option as a modeling framework for capturing and investigating MoC-s and their effects on software systems.

#### CHAPTER III

#### DEVS MODEL OF A TIME-TRIGGERED PLATFORM

This chapter introduces the use of the DEVS modeling formalism for specifying MoC-s for execution platforms in an implementation-independent manner. Given a set of software components and their connections, a selected execution platform and its MoC determine the execution semantics of the individual components and the legal interactions between components. We believe that the following approach enhances a software developers reasoning about a system design by providing simulation/prototyping capabilities for models of software components and their couplings over a selected MoC. In this example the interested platform is a TT MoC motivated by the Time-Triggered Architecture (TTA) [4] of the Vienna University of Technology and Dr. Hermann Kopetz.

# Time-Triggered Model of Computation

Once a chosen MoC is attributed to a software system, the MoC defines the structural, behavioral, and temporal properties that will characterize the system's behavior throughout execution [7]. Furthermore, the precise specification of a MoC is fundamental to understanding how system-level properties will arise from the component-level behaviors and interactions, i.e. compositionality. The use of the DEVS modeling framework is intended to leverage its precise mathematical foundations for unambiguously specifying MoC-s, and the operational nature of DEVS models will facilitate the analysis of modeled system behaviors and serve as a logical framework for migrating from models of MoC-s to their implementation.

The application domain of distributed real-time systems (industrial processes, aviation, automotive, etc.) depends on software-based implementations of physical control systems [3]. These applications are typically modeled by the following behavior: sense environmental/physical data (speed, heading, temperature, etc.), perform some process calculations based on the sensed input, apply an adjustment to the environment through

actuators (motor, piston, pump, etc.), and repeat this process continuously. This continual operation of trying to achieve a desired reference level of performance through repetitive processing steps motivates the use of strictly periodic models of system behavior. Safety and reliability are of the utmost criticality for any implementation intended to meet the desired controlled operation for such systems; failures may result in physical harm (if not death) to humans, animals, or property. Consequentially, these expectations on such systems have motivated the use of techniques that will guide designers towards implementations that are analyzable and verifiable regarding system performance.

One such approach for building dependable, periodic control systems is through the use of the Time-Triggered Model of Computation (TT MoC) [3]. In a TT system, triggering signals are generated over the progression of time according to statically defined schedules produced in the design phase. The requisite a priori knowledge of when events and actions are to occur through the use of static schedules produces systems that are more conducive to predictive modeling and analysis. Typically, these systems are constructed by partitioning the software-based functionality into concurrently executing software components, called tasks, that execute over a set of computational hardware units or processors, called nodes, and nodes are connected via a network for passing data between tasks within messages. An execution platform that implements the TT MoC on a node will use the TT control signals to initiate/terminate task execution, start the transmission of data messages, and initiate interactions with the physical environment or other systems.

The TTA [4] developed at the Vienna University of Technology by Dr. Hermann Kopetz is an industrial-level development framework produced by TTTech Computertechnik AG that provides the aforementioned services of the TT MoC for the dependable execution of safety-critical real-time systems. TTA further maintains the dependable execution of TT systems by offering redundant communication buses, a fault-tolerant time synchronization algorithm, and infrastructure for the replication of hardware and software subcomponents. The TTA requires the strict synchronization of system time and real-time data (i.e. state of variables) across all constituent nodes along with the

complete separation of the TT execution of software tasks from the TT communication protocol via a well-defined hardware interface (the Communication Network Interface or CNI). This separation along with the well-defined interaction mechanisms that determine how and when information may cross (if at all) the CNI are intended to further ensure the temporal and operational accuracy of executing systems. Furthermore, these restrictions support the use of the TTA as a composable architecture capable of handling the dynamic integration of nodes during run-time along with the use of heterogeneous node-level implementations in both hardware and software.

The logical and physical separation at the CNI allows a system built using the TTA to rely on various communication protocols for transporting messages between nodes. However, any viable candidate must be able to reliably transmit all TT messages according to the strict periodic message schedule with the necessary guarantee that data will be transmitted from the source to the receiver in the well-defined time interval between which the application-level tasks update the CNI and retrieve data from the CNI on their respective nodes. The TTA offers two Time-Triggered Protocols (TTP-s) as possible candidates: TTP/C and TTP/A. TTP/C [5] is intended for high-confidence systems that require the highly dependable transmission of TT messages between nodes and multiple mechanisms for avoiding faults or deleterious behaviors. TTP/A [6] is a low overhead implementation of a TTP that relies on a non-fault-tolerant master/slave configuration of nodes for passing TT messages. TTP/A is intended for lightweight sensor/transducer-level applications of distributed real-time systems, e.g. process control systems and low-level sensing in automotive systems.

In purely TT systems, the schedules that describe the tractable execution across all nodes are strictly periodic. For both task execution and message passing, the execution is separated into continuously repeating periods or cycles, called *hyperperiods*. Consequentially, this periodicity requires that the schedules specify only those timed events and actions that are invoked over a single hyperperiod. Each schedule sequentially orders all task execution or message instances in a given hyperperiod, and it is the foremost responsibility of the TT execution platform to maintain the timely execution of the schedules

over each hyperperiod cycle while the system is operational. Due to the causal dependencies between tasks executing and their resulting data that gets passed in the scheduled messages, the hyperperiod must be the same for both schedules.

The TT MoC DEVS specification presented below captures the general TT execution services required for the strictly periodic execution of software-based control systems: scheduled execution of software tasks or components, scheduled transmission of data messages, and synchronization mechanisms for ensuring lock-step execution of the system across all nodes. As this specification grows, mechanisms for fault-tolerance and improved robustness common to platforms such as TTA will be included. However, the objective of this framework is to be flexible enough to investigate the heterogeneous composition of MoC-s that allow behaviors other than those offered by strictly TT systems; therefore, the abstract specification of the individual DEVS components is of critical importance.

## Time-Triggered Platform Modeling Framework

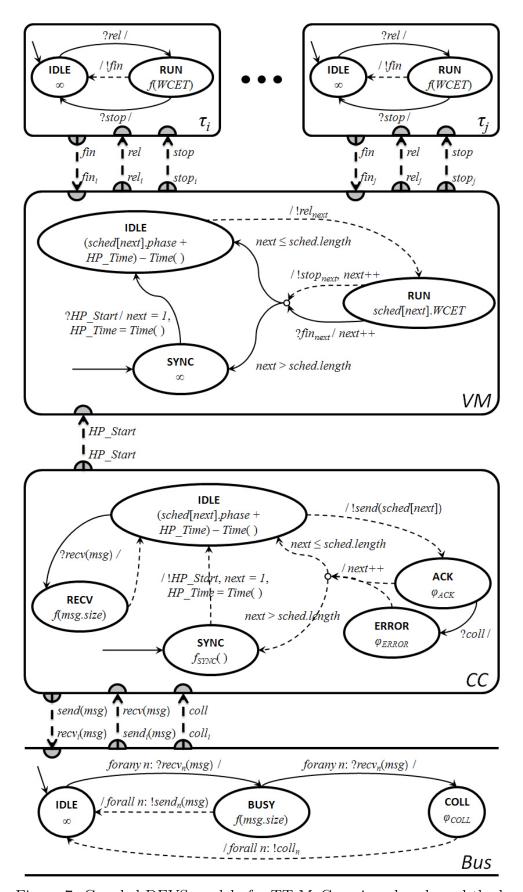

We now present the corresponding DEVS model of an execution platform that provides the aforementioned services of the TT MoC for a networked system of nodes (see Figure 1). The following sections will describe the primary components running on a single node that are responsible for maintaining the scheduled transmission of messages and execution of software tasks, the TT communication controller and TT task scheduler respectively. Also, models of a communication bus and software tasks are provided in order to illustrate how the modeling framework could be used to prototype a specified system. In the current manifestation of the modeling framework, all of the DEVS models are constructed using the DEVS++ C++ library [2] created and maintained by Dr. Moon Ho Hwang.

#### Time-Triggered Communication Controller

The primary responsibility of a TT communication controller is to accurately follow a fixed message schedule. A message schedule is generated offline, passed as an input to the platform, and cyclically evaluated throughout the execution. Unlike the strict time division multiple access scheduling rules of TTA and the TTP/C protocol [4, 5],

Figure 1: High-level architectural view of a TT system

this platform does not place any minimum or maximum on the amount of data that can be sent from a node in a round/cycle of the hyperperiod except those constraints that maintain the feasibility of the message schedule. Instead, the static message schedule specifies which node sends a message at an exact scheduled offset (the *phase*) with respect to the start of the hyperperiod. Each schedule round is one hyperperiod long, and the hyperperiod is of fixed duration. A node will be allotted no messages/slots if it is not expected to transmit any data within a schedule round. If a message is expected to be sent with a frequency greater than one within a round, it will be listed as many times in the schedule as it is expected with each appropriate scheduled transmission time. The length of each message, in bytes, is also indicated in the message schedule.

Establishing and maintaining TT communication across a network of nodes implemented using this platform proceeds according to the listed steps (see below). Figure 2 below is a DEVS model specification of the behavior as well. Within the DEVS representation, the italicized text (e.g. f(msg.size)) directly below a state label (e.g. **SYNC**, **RECV**, and **IDLE**) indicates the lifespan of its corresponding state. Also, a lifespan labeled as f() is a function of its argument, and a lifespan labeled with  $\varphi$  represents a constant. Variables next and  $HP_-Time$  are used to indicate the index (starting from 1) of the next scheduled message and the start time of the current hyperperiod respectively. The function Time() returns the current global time value. The event-triggered (external) and time-triggered (internal) transitions between states are represented by solid and

dashed black arrows respectively. The semicircles on the boundaries of the model represent the event ports of the model: protruding ports are output ports and inlayed ports are input ports. Lastly, not present in Figure 2 but used in Figure 3, the subscript of a label (e.g.  $rel_i$  and  $stop_{next}$ ) corresponds to an index value.

The logical execution steps for the TT communication controller proceed in following manner:

- 1. Synchronize all of the nodes on the network. Extremely important for ensuring the nodes begin executing the message schedule simultaneously. The amount of time to synchronize is dependent upon the underlying hardware and the chosen synchronization algorithm.

- 2. Transmit the hyperperiod start signal (marks the beginning of schedule execution).

- 3. Transmit data messages according to their strictly scheduled order and phase. Concurrently, allow reception of messages from other nodes. If a message is transmitted, ensure that a collision on the communication bus does not take place and proceed to the next scheduled event (either sending the next message or waiting for the end of the hyperperiod). If a message is received, process the message so that it can be used by software applications. The processing time depends on the size of the message data.

- 4. End of hyperperiod is reached (a schedule cycle has been completed).

- 5. Repeat process starting from step 2.

The requisite model (for simulating multi-node systems) of the communication bus is straightforward (see DEVS model in Figure 3). The model makes no assumptions regarding a specific hardware or protocol implementation for the bus, but all of the system nodes are expected to be connected to the bus for broadcast communication. Also, only one message can be on the bus at any given time; however, the message schedule for the TT MoC is typically constructed with this constraint in mind.

Indicated in Figure 3, the bus is initially idle and will remain so until a message is received on any of its recv() ports. In this model a unique triple of ports (recv(), send(),

Figure 2: DEVS model of the time-triggered communication controller

and coll() is created for each node in the system, and the nodes and their respective ports are differentiated by an index value (i and j in this example). Following the reception of a message, the bus will remain busy for some amount of time that is a function of the size of the data message, i.e. the transmission time over the bus. If no other message arrives during this time, the message will be sent to all nodes on the network. Conversely, if a new message does arrive from any node while the bus is busy, a collision occurs, the collision signal is sent to all nodes, and the data messages are lost.

Figure 3: DEVS model of the communication bus

### Time-Triggered Task Scheduler

Much like the communication controller, the TT task scheduler is primarily responsible for initiating the periodic execution of the software tasks based on a static task execution schedule initially passed as an input to the system. The current implementation model does not allow the preemption of tasks, i.e. only one task is released for execution at any given time and it finishes its execution before another task is allowed to begin executing. In order to properly maintain the timely execution of all tasks according to the schedule, the TT task scheduler is also responsible for terminating executing tasks that have yet to finish prior to reaching their worst-case execution time (WCET).

The task schedule for a node is similar to the message schedule mentioned in the preceding section. The schedule first specifies the hyperperiod that must match that of the message schedule. Next is an ordered listing of all task invocations. An invocation is listed for each time a task is to execute within a hyperperiod, and each listing specifies the scheduled release time (the phase) and WCET of the task invocation. Synchronizing the execution of the task schedule with the message schedule maintains the correctness of execution with respect to the system performance; therefore, each new round of the task schedule has to be initiated by the arrival of an event from the underlying communication controller indicating that a new schedule round is beginning. If no such event is received, then no tasks will be released for execution.

Not surprisingly, the implementation logic of the TT task scheduler is not dissimilar from the TT communication scheduler. Following along with the DEVS model in Figure 4, the execution steps are:

- 1. Synchronize the execution of the task schedule with the message schedule. Task execution cannot begin until the hyperperiod start signal is received from the communication controller.

- 2. Release tasks for execution according to their scheduled order and phase.

- 3. Upon the halted execution of the previously released task, move on to the next scheduled event: either the next task invocation or resynchronizing with the communication controller. Halted execution of a task is the result of either its self-completion or forced when its WCET is reached.

- 4. End of the hyperperiod is reached.

- 5. Repeat process starting from step 1.

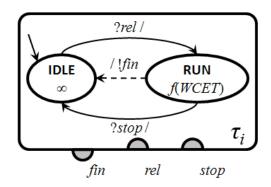

Figure 4: DEVS model of the time-triggered task scheduler

The DEVS TT task model (see Figure 5) is very simple since it is not intended to capture the actual logic of the software or how data is manipulated; instead, it merely supplies the timed execution traces for TT tasks. As indicated by the model, a task will remain idle until it is released for execution by the task scheduler. The task will continue executing until it finishes or it is forced to terminate by the TT task scheduler. The execution time of the task (the lifespan of the state **RUN**) is modeled as a probabilistic function based on the task's WCET. On an actual system, the execution time of a software task would be dependent upon many factors (hardware, software, and environmental

activity); however, the DEVS model must make the assumption that the WCET parameter was determined as a reasonable estimate based on the possible execution profiles of the system.

Figure 5: DEVS model of a time-triggered task

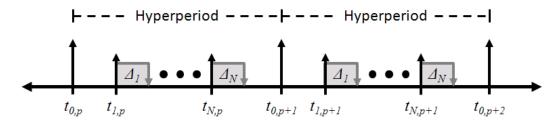

Putting all of these components together yields a coupled DEVS model for a single node that is presented in Figure 7. Also, Figure 6 is an example snapshot of a continuously executing TT system representative of the periodic execution of TT schedules. In Figure 6 each labeled time  $t_{i,p}$  indicates the occurrence of event i in the hyperperiod round p and  $\Delta_i$  is the events corresponding durative action time (e.g. transmission delay of a message or execution time of a task).

Figure 6: Activity timeline over the execution of a time-triggered schedule

# Summary

In this chapter we have presented a modeling framework for describing MoC-s and execution platforms in a non-implementation specific context using the DEVS modeling formalism. This framework is intended to facilitate the specifying of MoC-s and their

interactions in a mathematically precise and analyzable way, and the use of DEVS and its various tools allows software developers to construct executable models of their software systems. With this prototyping capability, developers can evaluate how a chosen MoC influences the behavior and temporal properties of their software applications.

Furthermore, an example MoC based on the TTA [4] was specified using the modeling framework. This platform, commonly used digital control systems, is based on the strictly periodic execution of software tasks and transmission of data messages to promote deterministic system performance. The underlying logic responsible for ensuring the behavioral characteristics of the MoC along with a template for modeling software tasks were provided to illustrate how to construct a model of a single node, and a simple communication bus model for sharing data between such nodes was provided for building larger models of networked nodes (a distributed system). The following chapter will present an implementation of the discussed TT MoC on off-the-shelf hardware and software components that used the preceding DEVS model as a logical guide for developing the execution platform.

Figure 7: Coupled DEVS model of a TT MoC equipped node and the bus

#### CHAPTER IV

#### AN OFF-THE-SHELF PLATFORM IMPLEMENTATION

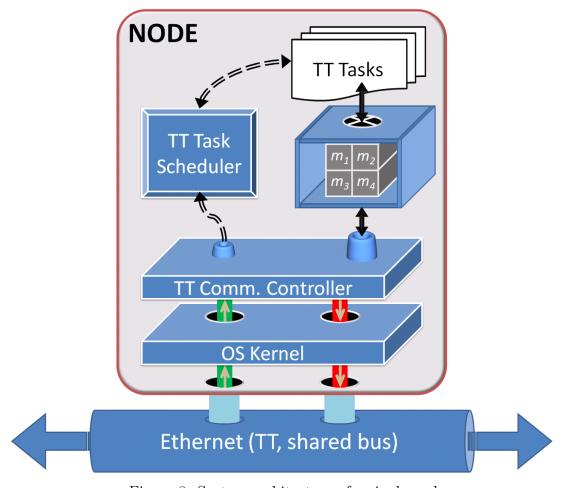

This chapter presents how the previously introduced TT MoC was implemented on off-the-shelf hardware and software components as a possible target execution platform for periodic digital control systems. Although the TTA has been developed and matured over many years in both research and industrial settings, it lacks the flexibility and extensibility for introducing other MoC-s or behaviors into the execution platform. These restrictions motivated the following execution platform that offered the same deterministic execution of the TTA with a hardware/software-independent platform Application Programming Interface (API). The resulting platform uses an abstract Virtual Machine (VM), FRODO, for executing TT software tasks coupled with a communication controller that provides the TT transmission of data messages between networked nodes, all of which is implemented using readily available infrastructure.

# Platform Implementation Architecture

The platform's implementation architecture is based on the logical separation principles similar to those of other TT platforms like Giotto [1] and TTA [4]: the periodic execution of software tasks is determined solely by the passage of time and the current operational mode of the system, i.e. events such as the arrival of new data messages do not affect the timing of task execution. Accordingly, only the most recent data values, representative of some control signals, are relevant to calculations performed by TT tasks; therefore, a globally shared memory construct is used to read-in and update data throughout execution. The resulting architecture is provided below in Figure 8. In the figure, solid black arrows represent the flow of data throughout the system whereas the dashed black arrows (see TT Task Scheduler) indicate the sending of events.

As indicated at the lowest level of Figure 8, a shared bus architecture is used for the transmission of TT messages between nodes. There are no explicit restrictions placed on the communication protocol used; however, it needs to be a relatively high bandwidth

connection that can be isolated from other networks to ensure communication integrity with as little overhead as possible. Currently, a standard Ethernet connection utilizing UDP broadcast communication is used to connect nodes in an isolated network across an Ethernet hub, a Netgear DS104 (with 4 10/100 ports). The physical nodes used in the deployment are Soekris net4801 units. These embedded boards come with a 266MHz 586 processor, 256MB of SDRAM, 3 10/100 Ethernet ports (each with an individual network interface controller), 2 serial ports, and 12 general purpose I/O pins. Also, each board is running a Linux 2.6.x kernel with no supplemental real-time patches. Linux was chosen since it is not only free but also widely accepted for embedded applications; however, in the near future, other deployments will be evaluated with an emphasis on porting the execution platform to other hardware/software configurations with an interest in operating systems that offer more "real-time" execution capabilities. Also, the selected programming language for the current implementation was C++.

Also illustrated in Figure 8 is the shared memory structure used to hold the relevant data that results from the calculations of the TT tasks (see the box in between the TT Communication Controller and TT Tasks) and is passed between nodes in the TT messages. This data structure contains one memory location for each unique message instance defined in the message schedule. Over the execution of a hyperperiod, all of the nodes should maintain the same data set, i.e. each node updates the respective memory location of a received data message regardless of which task (even if it is not on this node) will potentially use the data. The data is persistent as long as it is not updated; however, it is immediately overwritten whenever new data is available, i.e. there is no queuing of data. The representation of the shared memory in Figure 8 also indicates that the memory locations must be accessed controlled (see the white "X" across the access point on the top of the box). This is to prevent race conditions if both a TT Task and the TT Communication Controller are trying to update the same memory location. Currently, a POSIX mutex variable that functions as a binary semaphore is used to regulate access to the shared memory. In future extensions to the platform, it would be advantageous to pursue other approaches to synchronizing/regulating access to the shared memory

that did not involve potential blocking conditions on the calling threads. One approach could use two buffers and an indicator variable: the indicator points to the buffer that was previously updated by the last write operation and is currently ready to provide data upon a read operation. The next write operation updates the other buffer, and the indicator variable will switch to the newly updated buffer when the write is complete. This switching occurs with every new write operation. Accordingly, a write operation, even for large data sizes, never blocks a concurrent read operation, unlike the mutex.

Figure 8: System architecture of a single node

From the details presented thus far concerning the implementation, we see that the active components running at any given time on the platform can be the TT communication controller, the TT task scheduler or VM, and any currently active TT task. Consequently, the implementation must provide mechanisms for handling the concurrent

execution of these entities. Linux provides two types of such concurrency objects: processes and POSIX threads. POSIX threads were selected for this implementation since they require less overhead and a suite of threads in the same process share the same memory space. Furthermore, they do not place any restrictions on the use of C++ as the selected programming language.

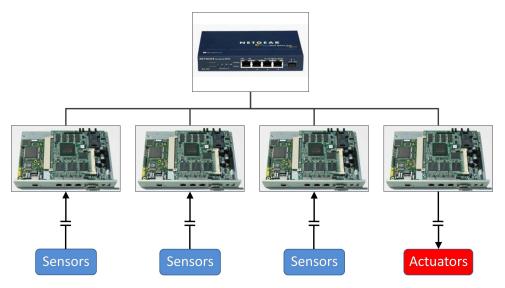

Throughout the rest of this chapter and the following one, a common system configuration (see Figure 9) is used for experiments and benchmarking the execution platform. There are up to four independent nodes connected via a shared Ethernet network. Anywhere from zero to three nodes will have some sensing device used as a data input and either zero or one device will have an actuator output device. Each specific example will be briefly described when it is used, but this is the common configuration.

Concerning the experimental configurations as well, for reasons that will become evident in subsequent sections, an additional input to the system is required at run-time beyond the already mentioned message and task execution schedules. This additional input is a configuration file that lists the set of nodes that are expected to be on the network and part of the system during operation. The file merely contains unique identifiers that are used to differentiate between the nodes, and each node is provided its corresponding unique identifier during system initialization. The system will not go into operation unless all nodes are present and each node matches with a specified unique identifier.

## High Resolution Timeouts and Scheduling in Linux

Linux supports halting the execution of a thread for an arbitrary amount of time with microsecond resolution using the clock\_nanosleep() function. This function uses a predefined POSIX timer object as the reference clock for timeouts, and it can timeout for a specified amount of time or until it reaches some specific time value in the future. This function was used as the baseline method for scheduling events on the platform since the typical applications required a timing resolution around the one half to one millisecond range; however, this function was not without its limitations.

Figure 9: General implementation configuration of nodes for experiments

First, the Linux documentation indicates that even though the scheduling and timing mechanisms behind clock\_nanosleep() guarantee that it will never return from a timeout prior to the specified target time, it provides no guarantees regarding how long after the target time it will return. This is a non-ideal implementation for real-time systems with strict timing requirements; however, we had no other available options using Linux routines or access to hardware-level interrupts and timers that would have provided a higher-level of timing safety.

Considering the general applications that would be running on the platform (mainly a suite of strictly periodic threads) and the isolation of the system, it became apparent that the scheduling overhead and computational demand on the system during execution would be periodic if not nearly constant. Further analysis of the system and use of the clock\_nanosleep() function indicated that there is a baseline or minimum overshoot from the target timeout value, and this error typically stabilizes to a slightly larger value during system operation. The minimum overshoot or baseline resolution of the function was determined to be about  $40\mu$ s. This implies that no matter what non-negative, non-zero value is specified as the target timeout value, the function will return no sooner than  $40\mu$ s after it. Unfortunately, the error encountered during operation is typically computational load dependent; therefore, a dynamic adjustment approach was implemented to try to

minimize this error to ensure the most accurate timing as possible for scheduling. The resulting high-resolution timeout routine was implemented using the following process.

First, the clock\_nanosleep() minimum offset is determined during system initialization using test calls. All subsequent calls to timeout a thread (the communication controller or VM thread) are reduced by the current offset value for that thread (note: a different offset is maintained for each thread). If the desired timeout is less than the current offset, the system will busy-wait until the desired time is reached and then return. Otherwise, the offset reduction is taken and the new value is passed to clock\_nanosleep() as the new desired timeout value. Upon returning from the timeout, the error is measured (difference between the current time and the desired time), and the offset value is adjusted by adding or subtracting some proportion of the error as long as the error is not too large such that the new adjustment would cause instability or oscillations in subsequent calls, i.e. extremely large errors must be ignored since the system will most likely not produce similar results in subsequent calls.

This offset adjustment approach is similar to using a proportional feedback controller from control theory to correct for operational errors; however, this implementation would have to be modified to fit a strict proportional controller model in order to discuss the stability or performance (e.g. steady-state error) of the controller. To be analyzable as such, the use of a discrete-time proportional controller would require that the timeouts would have to be strictly periodic with a fixed timeout value and continuously running even when a timeout by the communication controller or VM has not been requested. This option was explored as an interesting application of a control-theoretic approach to achieving accurate sub-millisecond timeouts in Linux; however, the overhead from running the adjusted timeouts with periods ranging from  $150 - 500\mu$ s resulted in starving the other executing threads of computation time and increased the response time of the communication controller and VM threads.

Since the system load is currently very predictable during execution, the adjustment value typically reaches a stable value very quickly once the execution of the schedules begins, i.e. there is little ramp-up time or "pipeline filling". Testing has shown that

this method is accurate enough to yield consistent timeout errors less than  $20\mu$ s. Unfortunately, as the system's load and external interactions with other networks and/or applications become less predictable, this correction scheme will no longer be effective or nearly as accurate. At such a time, the need for fine-grained timing control (hardware-level access and/or interrupts) will become a necessity to meet the strict timing demands of most TT systems.

# **Communication Controller**

Given a system configuration and the cyclic message and tasks schedules, it is the responsibility of the TT communication controller on each node to maintain communication with the other nodes of the system and their partnered TT task schedulers in order to properly execute over the schedules in a synchronized manner. We will now detail the specific implementation approaches and performance benchmarks of the current off-the-shelf platform implementation using the previously detailed hardware/software configuration.

#### Initialization and Node Discovery

We now provide the implementation details of how the system nodes initially synchronize to confirm all are ready to begin executing. In this preliminary version of the execution platform, a fault-tolerant algorithm for establishing and maintaining node synchronization was not utilized since this is a non-trivial task in of itself for embedded and real-time systems. Instead, a simple master-slave approach that makes assumptions concerning the possible execution conditions and bus activity was chosen; however, improving the approach to be more robust (like the method used in TTA) would be worthwhile.

At initialization, each node must determine if it is the "master" node or one of the "slaves". Currently, the master is assigned to be whichever node has the first unique identifier listed in the system configuration file, and accordingly, all other nodes assume the role of a slave. As the designated master, a node must first ensure that all of the nodes listed in the configuration file are present before execution is allowed to begin (the

node discovery process). The master node begins the discovery process by transmitting a synchronization message onto the network. The execution can proceed only if the master receives a synchronization acknowledgment message from each and every slave listed in the configuration file. Until all acknowledgements are received, the master will continually transmit the synchronization message every (N+1)\*5 milliseconds, where N is the number of slave nodes. Conversely, when a slave node starts its initialization and reaches the node discovery step, it will wait indefinitely until it receives the synchronization message. Upon receipt, it will transmit its synchronization acknowledgement message at pos\*5 milliseconds after receipt, where pos is the integer index of the slave node's unique identifier in the configuration file. Accordingly, the discovery process is complete when all slaves have acknowledged the synchronization message, and the master node will conclude the process with the transmission of multiple completion messages.

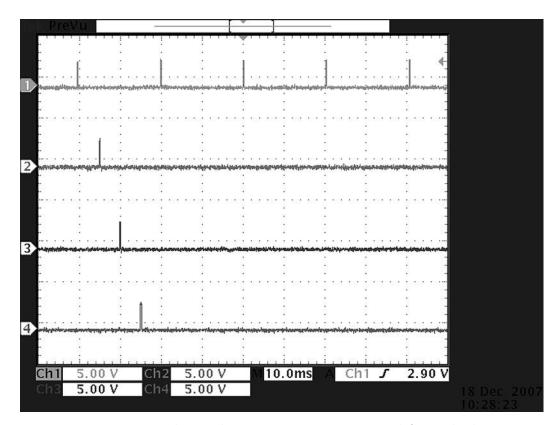

Figure 10 shows an oscilloscope output of the message activity for this process with four nodes (note: the major intervals of the time axis are 10ms apart). The top channel corresponds to the master and the three other channels are the slaves. The brief pulses on each channel represent the transmission of a message. Initially, the master transmits the synchronization message, each slave then acknowledges the message at the proper 5ms intervals, and finally, the master sends out four synchronization complete messages at 20ms intervals (tries to ensure that all slaves receive this completion signal). This process is fairly rudimentary; however, all experiments on an isolated network have never failed to properly synchronize during initialization.

# Synchronization of the Hyperperiods

Once the master is sure that all nodes are present, it is now responsible for initiating and maintaining a synchronized start of the hyperperiod (message schedule execution) for every cycle the system is operational. This is critical to maintaining functional correctness of the system, because the misaligned execution of the message schedule could increase the latency between the sampling of an input and the subsequent application

Figure 10: Node synchronization process viewed from the bus

of a control-related adjustment on the output of the system, i.e. degrade controller performance. Unfortunately, the current implementation's selected infrastructure (Linux, POSIX threads, non-hardware level timers, etc.) constrains the allowable overhead or computational requirements that the execution platform can introduce; therefore, the current method for synchronizing the hyperperiods is not fault-tolerant or robust. Ideally, the migration of this platform to more "real-time" capable hardware/software will enable the development of more thorough synchronization methods.

Similar to the discovery process, the slave nodes will not start the upcoming hyperperiod unless the appropriate message is received from the master node. After completing the discovery process or concluding a previous schedule round, the master transmits the hyperperiod start message on the network, and each individual node will immediately begin executing the message schedule after receiving this message, including the master. The master receives the message as well since the UDP broadcast protocol will send it to all nodes in the addressed subnet regardless of the sender. Once the message is received, each communication controller stores the current time as the start epoch of this round

of the schedule and then transmits the scheduled TT messages that originate from its data set. The precision of this approach rests squarely on the uniform arrival time of the message to all of the nodes, including the master. This too is a naive approach to maintaining correct system performance; however, the current implementation characteristics (especially the restrictions on outside network activity) seem to provide a stable environment for yielding only marginal errors in the accuracy of the start time of each hyperperiod (see Figure 11(a)).

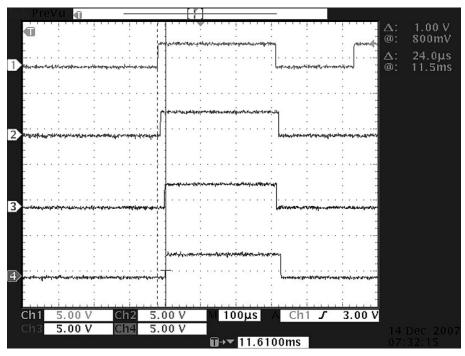

Figure 11(b) is another oscilloscope output of the activity of a set of four nodes over two hyperperiods of execution. Ignoring the details of how to interpret the various pulses on each channel, attention must be directed towards the two vertical cursor lines (a solid line on the right and a dashed line on the left). The cursors are positioned at the start of two hyperperiods, and the vertical pulse on each channel that is aligned with each cursor represents when each node began executing the hyperperiod. In this example the hyperperiod was 20ms and channel one corresponds to the master node. We can see at both hyperperiod synchronization instances that all four nodes begin executing at nearly the same time (usually within  $30\mu s$  for all nodes, see Figure 11(a)). Also, the two cursors are placed to measure the time interval between these instances, and we can see that the measured time interval between the synchronization points was near 20.1ms. This error of about  $100\mu$ s represents a deviation of 0.5% for this single instance; however, further data analysis over thousands of hyperperiods of varying lengths yielded an average hyperperiod error of about  $40\mu s$  with a standard deviation on the order of  $10\mu$ s. This means that it will typically take greater than 20,000 hyperperiods or schedule rounds before the accumulated deviation of the execution reaches one second.

Currently, this error between consecutive hyperperiods goes uncorrected in terms of when the messages are scheduled in the currently executing hyperperiod, e.g. the transmission of a message scheduled to occur 1ms after the start of the hyperperiod,  $t_{HP}$ , will occur at time  $t_{HP} + 1ms$  even if the current hyperperiod started  $50\mu s$  later than it should have (the corrected time would be  $t_{HP} + 1ms - 50\mu s$ ). A more robust implementation (like TTA) with better clock synchronization and/or hardware-level timing capabilities could

(a) Difference in hyperperiod start times

(b) Length of hyperperiod

Figure 11: Hyperperiod synchronization across four nodes

account for this deviation (or possibly provide perfectly periodic execution); however, the inability to truly guarantee how accurately the master can send out the synchronization message (based on a timeout) or how quickly the communication controller can be notified of the arrival of a new message (from the select() routine) make adjusting for this deviation a risk with serious ramifications in tightly scheduled systems (e.g. skipping message instances).

Since the synchronization is based on the transmission of a message across the network, the delay introduced by transmitting a message has to be accounted for when the master node is determining what time to schedule the transmission of the synchronization message. Network isolation allows this delay to be compensated for using a fixed offset to indicate how long before the start of the next "ideal" hyperperiod that the synchronization message should go out on the bus. Through extensive testing and benchmarking, the current conservative compensation value was determined to be  $250\mu$ s. This is considered conservative since it produces the presented synchronization accuracy with very few cases where the start of the next hyperperiod occurred earlier than the ideal time. Larger compensation values have been tried to reduce the average error to near zero; however, they always increased the likelihood of starting a schedule round early.

### Synchronization of the Communication Controller with the VM

The simultaneous execution of both the message and task schedules is one of the primary requirements of the TT MoC for maintaining proper controller performance (keeps the tasks operating on the most current data). Upon establishing the start of a given hyperperiod across the nodes, the communication controller of each node must further synchronize the start of the hyperperiod with its respective TT task scheduler or VM (see "HP\_Start" event in Figure 7). Given the selected Linux platform, the simplest and least computationally restrictive method of signaling to the VM to begin executing the task schedule was through the use of a POSIX mutex (a binary semaphore). The specifics of the VM execution semantics will follow in a later section, but we briefly mention some details here.

The communication controller is always given possession of the mutex during the system initialization process. Directly following the synchronization of the hyperperiods across all of the system nodes, the communication controller releases the mutex and briefly halts execution for a specified amount of time (currently  $350\mu s$ ). This pause allows the underlying operating system to reschedule the thread execution to allow the VM thread to acquire the mutex long enough to save the current time value as the start of its hyperperiod. The VM immediately releases the mutex, the operating system reschedules the awaiting communication controller thread, and the communication controller reacquires the mutex and begins executing over its message schedule. Each subsequent hyperperiod must be synchronized between the two threads as well; therefore, the VM must try to reacquire the mutex at the end of each its hyperperiods (it will be blocked) such that it is ready to save the new hyperperiod start time the next time the communication controller releases the mutex.

Obviously, using a mutex introduces a time lag between when the communication controller stores the current time value for the start of the hyperperiod versus when the VM can do the same (since the operating system has to reschedule the threads); however, this error can also be mitigated by subtracting a fixed offset value from the VM's saved hyperperiod start time. Once again, the predictability of this error results from the restriction that no other activity will be taking place on either the communication bus or the node itself while the system is operational (common underlying assumptions of the TT MoC for digital control applications). The current offset adjustment value is  $130\mu s$  and the measured average error between the saved hyperperiod start times for the two threads is typically  $15-20\mu s$  with very little deviation. This too is a conservative adjustment value, i.e. the message schedule runs slightly ahead of the task schedule; however, the TT MoC (especially in TTA [4]) dictates the primacy of accurate data sets over the scheduled execution of tasks. Once again, the values of  $350\mu s$  and  $130\mu s$  for this process had to be determined by benchmarking the chosen platform since both are highly software and hardware specific.

## Transmitting and Receiving TT Messages

Now that all of the main tenants of synchronizing the communication controllers have been presented, the process of transmitting and receiving TT messages can be discussed. The logical operation of this process has already been presented in the DEVS description of the communication controller (see Figure 2); it is similar to most cycle executive operations over a pre-defined schedule. The communication controller properly transmits messages according to the sequential message schedule, and it must also listen for any incoming data messages on the communication bus while waiting to send out the messages. When a scheduled transmission time is reached, the communication controller obtains the current value of the data message from shared memory, packages the message for transmission, sends the message out on the shared communication bus via the underlying communication library, and moves on to repeat the process for the next scheduled message or awaits the start of the next hyperperiod if the end of the message schedule has been reached. Even though the high-resolution timeout mechanism (adjusted clock\_nanosleep() routine) discussed above is capable of accurately scheduling the communication controller to awake when it is time to transmit a scheduled message, it cannot concurrently notify the communication controller when an incoming message has arrived via the communication bus. A different mechanism is required for this behavior, and it is provided by the select() function.

As a brief note, we would like to indicate how a message is packaged for transmission such that the reception side of message passing can be as quick as possible. The current implementation first retrieves the message data from the shared memory, and then the following string is attached to the front of an outgoing message: "(msg\_pos)". Here, msg\_pos indicates the index of the message in the message schedule. Since all nodes use the same message schedule, any node that receives this message can quickly determine from this index value which memory location to update with the new data. This implementation was also intended to add as little overhead as possible to the message communication process.

The select() function allows us to specify that we would like to listen to a communication endpoint (a UDP socket in this implementation) for any activity, i.e. the arrival of a new data message. If any message comes in on this endpoint after calling select(), it will return from being called indicating that a new message is available. Furthermore, a timeout alarm can also be specified that will cause select() to return if the timeout expires and no new message has yet been received (a timeout of length "null" will allow select() to wait for a new message indefinitely). This seems to provide all of the features needed by the communication controller to schedule message transmissions and concurrently listen for new data messages; however, the underlying implementation of select() is not without its limitations.

According to the Linux documentation, the timeout feature of select() is influenced by the operating system's timer interrupt. Regarding the select() function, this periodic signal, called a "jiffy", indicates the periodic points in time that the operating system will check to see if the timeout of the select() has expired. Our Linux kernel uses a jiffy with a period of 4ms; therefore, select() will only check the timeout alarm's status every 4ms. Obviously, any application that requires sub-millisecond resolution for scheduling cannot depend purely on this function, and such is the case for the TT communication controller. However, it does not mean the select() function's capabilities cannot be used if properly handled.

Instead of calling select() when a timeout must be specified for sending the next message and listening to the communication bus, the communication controller simply calls a "listen" routine and indicates the target time of the next scheduled event. This routine will use select() as described in the previous paragraph only if the timeout is greater than two times the jiffy period (8ms in this case). Any less of a timeout runs the risk of not being properly handled by the scheduler since a timeout that expires in between two jiffy signals is not handled until the later one. For example, a timeout of 4ms that starts  $100\mu$ s after the jiffy signal will actually last 7.9ms. When it is safe to use select(), the new timeout value ( $TO_{new}$ ) is an integer multiple of the jiffy period ( $P_{jiffy}$ ) given by the following equation.

$$TO_{new} = P_{jiffy} * (\lfloor TO_{curr} \div P_{jiffy} \rfloor - 1) \tag{1}$$

When the desired timeout is less than 8ms, it is necessary for the listening routine to busy-wait and periodically check the communication endpoint for a new message. Busy-waits can be very expensive if they poll too quickly, but they can also increase response time to new messages if they do not check often enough. When the minimum allowable time interval between consecutive messages is 1ms (this is the typical constraint placed on all experiments thus far), a busy-wait period of  $400\mu$ s was determined to be quick enough without using up too much processing time such that other threads (such as the VM) were starved.

After repeatedly performing the busy-wait operation, eventually the busy-wait period will be larger than the amount of time until the desired target time is reached. When this occurs, a timeout for the exact amount of remaining time is requested. Both the busy-wait calls and the final timeout request are handled using the offset-adjusted clock\_nanosleep() routine described earlier.

#### Timing Properties of Message Passing

Throughout the description of the communication controller's implementation on the deployment platform of the Soekris net4801 boards running the Linux operating system, various detailed timing properties or limitations were provided to give a reasonable expectation of how accurately this off-the-shelf implementation could follow a predefined message schedule given certain assumptions. While these details are of the utmost importance to the schedule generation process for determining the schedulability of a designed system, the timing properties of physically sending, receiving, and processing message data on this implementation have yet to be discussed. Not only are these properties extremely important to schedule generation but they also exhibit the most variability.

Through various experiments and tests, the logical correctness of this implementation has been proven and its degree of accuracy in scheduling events has been quantified. Now, we must look at how the chosen platform affects the main phases of passing a message between nodes: from memory to the communication medium (transmission delay), across the communication medium from transmitter-to-receiver, and from the medium to the memory of the receiver (reception delay).

In order to gather results over a range of message sizes that could potentially be used in real-world applications, the following data was gathered assuming communication buffers of 4096 bytes (or 4KB). These are the buffers used by the underlying communication library (responsible for implementing the UDP protocol) that interacts directly with the operating system to move data on and off the communication medium. This buffer size is also used in the communication controller for retrieving message data from the shared memory; however, the actual size of the messages in memory is specifically provided in the message schedule and not equal to the buffer size. The only stipulation is that all messages must be of a size less than the message buffer, i.e. splitting-up message data across multiple messages is not allowed.

First, the timing properties of the communication medium in this implementation are the least influential. Given any medium (100Mbps Ethernet in this case) with dedicated hardware and well-defined message protocols, generating an estimate of how long it takes to physically move data across the medium is fairly straightforward with access to properties such as packet size, bandwidth, etc. On this platform, the transmission time was only readily measurable by the time interval starting when the communication library relinquishes control of a data message to the operating system to move onto the communication medium and ending when the "listen" routine of the receiver's communication controller determines a new message has been received. Every test has shown that this time interval is typically  $70 - 80\mu s$ ; however, a conservative approach would be to assume  $100\mu s$ .

On the sending side of a message transmission, the transmission delay was measured starting from the point the communication controller is awakened from a timeout for the next scheduled message transmission to the point where the communication library has successfully passed all of the message data to the operating system to put onto the communication medium. The converse is true for the reception delay of a message: it starts when the listening routine is notified a new message has arrived and ends when all of the updated message data has successfully been written into the shared memory of the receiving node. In summary, these values try to capture the entire message passing overhead that is introduced by both the operating system and the communication controller's implementation.

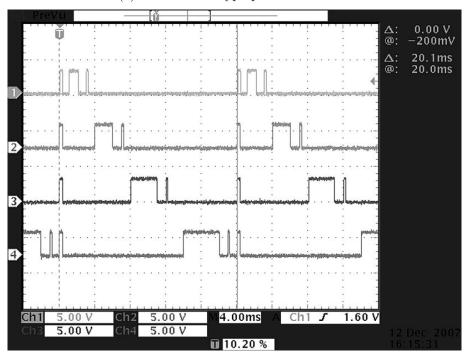

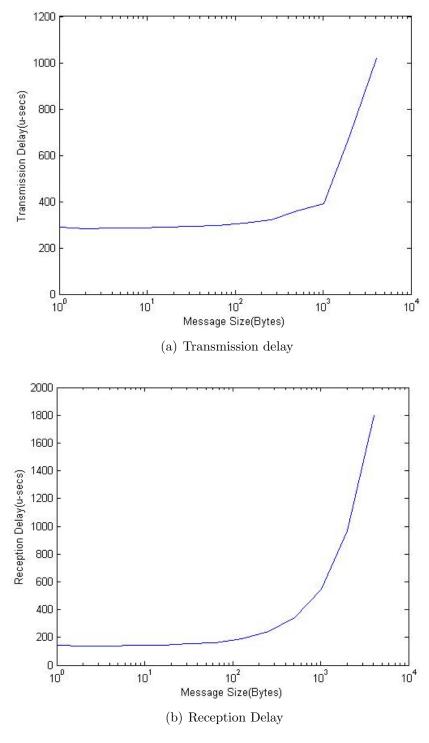

The following data (see Table 1 and Figure 12) was captured by testing a configuration of four nodes where each node was responsible for sending two messages of the same size each hyperperiod. Each test was conducted using four different configurations such that all four nodes assumed the role of master at least once. In total, the following values were determined from sending over 4000 messages per specified message size. These tests assumed an ideal scenario for uninterrupted communication where no periodic tasks were running and each message was scheduled 12ms apart from the next message (avoids any effects of the busy-wait implementation of the listening routine). Consequently, these results are a baseline or starting point for determining how closely messages can be scheduled provided a specific design.

Table 1: Message communication timing properties

| Message Size(Bytes) | Transmission Delay( $\mu$ s) | Reception Delay( $\mu$ s) |

|---------------------|------------------------------|---------------------------|

| 1                   | 288                          | 141                       |

| 2                   | 283                          | 139                       |

| 4                   | 287                          | 139                       |

| 8                   | 287                          | 142                       |

| 16                  | 290                          | 146                       |

| 32                  | 292                          | 153                       |

| 64                  | 295                          | 163                       |

| 128                 | 306                          | 192                       |

| 256                 | 321                          | 241                       |

| 512                 | 359                          | 342                       |

| 1024                | 390                          | 549                       |

| 2048                | 686                          | 970                       |

| 4091                | 1021                         | 1801                      |

Figure 12: Message communication timing properties

## Summary of Results for Communication Controller

The results from the above description of the communication controller provide the relevant timing properties that determine how closely a set of messages could be scheduled with relative confidence that messages would arrive at the receiver nodes before the new data is used by the TT tasks for calculations. From the results we can see that the use of large messages (> 512 bytes) can very quickly require consecutive messages in the schedule to be separated by more than 1ms in order to have any certainty that collisions or insufficiently slow response times will not occur. Still, the variability of the timings that result from the use of Linux timing utilities (e.g. clock\_nanosleep() and select()) dictate that it is not recommended to schedule any set of messages (regardless how small the message sizes are) with a separation interval smaller than 1ms. Furthermore, the reception delay values for the various message sizes must be taken into consideration when scheduling the TT tasks as well; the data in Table 1 must be used as a baseline for determining when a message must be transmitted so that the data is available to a task when it is released for execution.

Concerning the average timing properties: overshoot of timeout utilities  $(20\mu s)$ , misalignment of hyperperiod start time between nodes  $(30\mu s)$ , deviation from ideal hyperperiod intervals  $(40\mu s)$ , hyperperiod synchronization lag between the communication controller and VM  $(20\mu s)$ , and the message passing delays between nodes (see Table 1), the deviation from the ideal hyperperiod intervals is the least readily accounted for by either fixed offset adjustments or sufficient slack time between scheduled events. Currently, this deviation does accumulate over the operation of the system; therefore, the start of each hyperperiod will more than likely be misaligned from the ideal hyperperiod start time. This error would affect the controller performance since the accumulation effectively alters the period of execution of a control task (analogous to changing the sampling rate of a controller). Adaptive strategies in the communication controller and/or the tasks themselves could try to account for this; however, this underlying problem must be mitigated for this platform (in any of its potential hardware/software manifestations) to be applicable to safety-critical systems.

In conclusion, the presented implementation for the communication controller is capable of scheduling the periodic transmission of data messages over a shared communication bus with tens of microseconds accuracy. Granted that assumptions regarding the isolation (from external forces) of the network and the individual nodes seem idealistic, they are not atypical in the applications such an execution platform is intended for since it is often necessary to take as many precautions as possible to provide guarantees for reliability, robustness, and quality of performance. However, there are extensions and improvements to be made in order to provide a deployable TT communication controller.