# Error Estimation and Error Reduction with Input-Vector Profiling for Timing Speculation in Digital Circuits

By

Xiaowen Wang

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

May 10, 2019

Nashville, Tennessee

Approved:

William H. Robinson, Ph.D.

Bharat Bhuva, Ph.D.

Daniel Loveless, Ph.D.

Marcus H. Mendenhall, Ph.D.

Aniruddha Gokhale, Ph.D.

#### **ACKNOWLEDGEMENTS**

This is a long journey. I am glad that I finally here after all difficulties and obstacles during these years. For this important achievement in my life, the first and foremost person I would like to thank is my dear advisor, Dr. William H. Robinson, for his continuous guidance and support not only in academic field but also in my life. He always encourage me to follow my curiosity and been there when I need help. I also want to thank all of my committee members, Dr. Bhuva, Dr. Mendenhall, Dr. Loveless, and Dr. Gokhale, for their insightful comments. Thank Vanderbilt University and National Science Foundation for providing all resources and financial support.

Along this journey, I am so grateful to my husband, Zhengyu, for his hearted encouragement during my down time. Without his love and fully support, I am not sure if I have the strength to make to this point.

Lastly, thanks to my parents for always believe in me, you guys are awesome! To my son, Marvin, and my grandparents, I love you!

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                                                                                            | Page     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------|----------|

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ACK  | NOWLEDGEMENTS                                                                                              | ii       |

| I. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LIST | OF FIGURES                                                                                                 | V        |

| I. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LIST | OF TABLES                                                                                                  | vi       |

| Better-Than-Worst-Case design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | СНА  | PTER                                                                                                       |          |

| Variations that impact timing Motivation Research contributions 7  II. BACKGROUND AND RELATED WORKS 9  Timing analysis 9  Path activation probability analysis 12  Timing speculation methodologies and error resilience in BTWC design 15  Evaluation Methods for BTWC designs 22  Multi-threshold technology in VLSI designs 27  Timing speculation vs. Instruction speculation 29  III. RESEARCH METHODOLOGY AND BTWC DESIGN FLOW 36  General EDA design flow and the customized design flow in this work 36  Value change dump files 32  IV. ALL-CLOCK-FREQUENCY ERROR-ESTIMATION 36  Obtaining outputs settling behavior 36  Categories of primary outputs 36  Error count estimation and error rate calculation 42  Error estimation results discussion 47 | I.   | INTRODUCTION                                                                                               | 1        |

| II. BACKGROUND AND RELATED WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | Variations that impact timing                                                                              | 4        |

| Timing analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                                                                                            |          |

| Path activation probability analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | II.  | BACKGROUND AND RELATED WORKS                                                                               | 9        |

| Multi-threshold technology in VLSI designs 27 Timing speculation vs. Instruction speculation 29  III. RESEARCH METHODOLOGY AND BTWC DESIGN FLOW 30 General EDA design flow and the customized design flow in this work 30 Value change dump files 32  IV. ALL-CLOCK-FREQUENCY ERROR-ESTIMATION 36 Obtaining outputs settling behavior 36 Categories of primary outputs 39 Error count estimation and error rate calculation 43 Error estimation results discussion 47                                                                                                                                                                                                                                                                                            |      | Path activation probability analysis  Timing speculation methodologies and error resilience in BTWC design | 12<br>15 |

| General EDA design flow and the customized design flow in this work Value change dump files 33  IV. ALL-CLOCK-FREQUENCY ERROR-ESTIMATION 36  Obtaining outputs settling behavior 36  Categories of primary outputs 39  Error count estimation and error rate calculation 43  Error estimation results discussion 47                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | Multi-threshold technology in VLSI designs                                                                 | 27       |

| Value change dump files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | III. | RESEARCH METHODOLOGY AND BTWC DESIGN FLOW                                                                  | 30       |

| Obtaining outputs settling behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                                                                                            |          |

| Categories of primary outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IV.  | ALL-CLOCK-FREQUENCY ERROR-ESTIMATION                                                                       | 36       |

| Error count estimation and error rate calculation 43 Error estimation results discussion 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                                                                                            |          |

| ( ) =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | Error count estimation and error rate calculation                                                          | 43<br>47 |

| V.   | OFF-LINE ERROR-CHECKING METHOD                                            | 55 |

|------|---------------------------------------------------------------------------|----|

|      | General error checking and off-line error checking methodology comparison |    |

|      | Reformatting .vcd file for off-line error-checking                        |    |

|      | Implementing the off-line error-checker                                   |    |

|      | Error estimation vs. error checking results comparison                    |    |

|      | Conclusion                                                                | 63 |

| VI.  | DUAL-THRESHOLD VOLTAGE APPROACH FOR TIMING ERROR                          |    |

| RED  | UCTION                                                                    | 64 |

|      | Dual-threshold voltage approach for re-timing                             | 64 |

|      | Identification of critical cells.                                         | 65 |

|      | Error reduction results comparison and discussion                         | 68 |

|      | Conclusion                                                                |    |

| VII. | SUMMARY AND FUTURE WORKS                                                  | 74 |

| APP] | ENDIX                                                                     | 76 |

| REFI | ERENCES                                                                   | 84 |

# LIST OF TABLES

| I                                                                                                                                                                           | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 1: Summary of several EDAC methodologies                                                                                                                              | 24   |

| Table 2: Overview of the circuits used in the analysis                                                                                                                      | 30   |

| Table 3: Comparison of C1908 static delay, switching activity rate and active cycles rate Output N2899 has longest delay and Output N2891 is the greatest error-contributor |      |

| Table 4: Benchmark circuit static propagation delay of all error-possible outputs                                                                                           | 48   |

| Table 5: Comparison of error composition from critical path and greatest error-contributed PO other than the critical path                                                  |      |

| Table 6: Total error numbers and the Dynamic Replacement improvement                                                                                                        | 72   |

| Table 7: Low-V <sub>t</sub> cell usage comparison between Full Path Replacement (FPR) and Selection Cells Replacement (SCR)                                                 |      |

| Table 8: Leakage power (μW) comparison of baseline, Full Path replacement (FPR) and Selected Cells Replacement (SCR)                                                        |      |

# LIST OF FIGURES

| Page                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1: Block diagram of BTWC design general structure                                                                                                                                                             |

| Figure 2: An example of critical path delay distributions: (a) Before the variations (b) After the variations [7]                                                                                                    |

| Figure 3: An example to illustrate the relationship of the timing error probability with circuit performance (a) Timing error probability versus clock frequency, (b) Circuit performance versus clock frequency [8] |

| Figure 4: Dynamic behavior curve of two paths with the same static delay time. [17]13                                                                                                                                |

| Figure 5: Block diagram of Razor logic. [22]                                                                                                                                                                         |

| Figure 6: The circuit-level schematic of the shadow latch used in Figure 5. [22]                                                                                                                                     |

| Figure 7: The pipeline recovery using global clock gating. (a) The pipeline structure. (b)  The pipeline operation timing. [28]                                                                                      |

| Fig. 8: The pipeline recovery using counterflow pipelining. (a) The pipeline structure. (b) The pipeline operation timing.[28]                                                                                       |

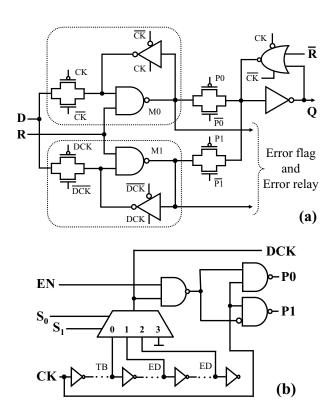

| Figure 9: Circuit-level schematic of Razor II flip-flop. (a) Flip-flop schematic. (b)  Transition detector schematic. (c) Detection clock generator. [29]                                                            |

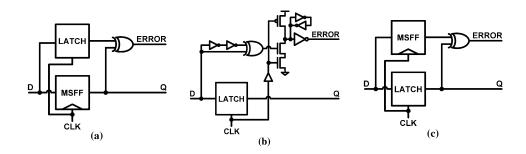

| Figure 10: Different ways to implement Razor flip-flop to detect timing errors. [32]20                                                                                                                               |

| Figure 11: Schematic of TIMBER flip-flop. (a) Main flip-flop part. (b) Clock signal control and generating part.[33]                                                                                                 |

| Figure 12: TIMBER latch schematic. (a) Main latch part. (b) Clock signal control and generating part.[33]                                                                                                            |

| Figure 13: The customized EDA flow with Synopsys tools                                                                                                                                                               |

| Figure 14: The proposed design flow chart                                                                                                                                                                            |

| Figure 15: An example of value change dump file. (a) is the header part, and (b) is the body part                                                                                                                    |

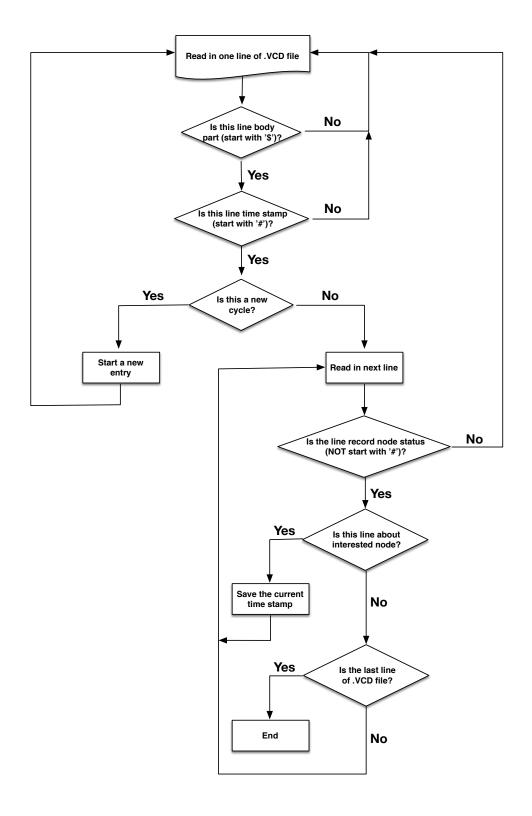

| Figure 16: Algorithm flow chart of switching time stamp extraction for a specific node38                                                                                                                             |

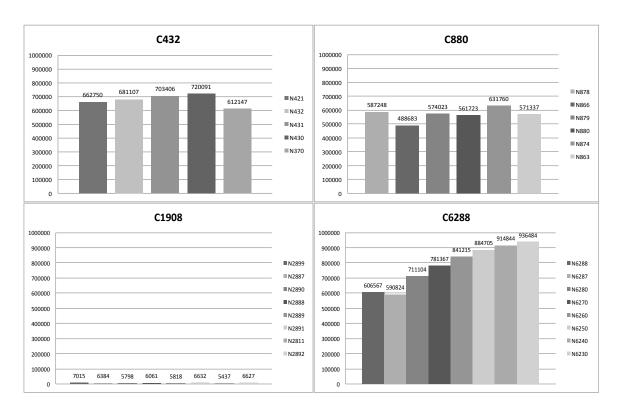

| Figure 17: The total active cycles out of 1 million cycles of error-possible outputs.  Benchmark circuits (a) C432, (b) C880, (c) C1908 and (d) C628840                                                              |

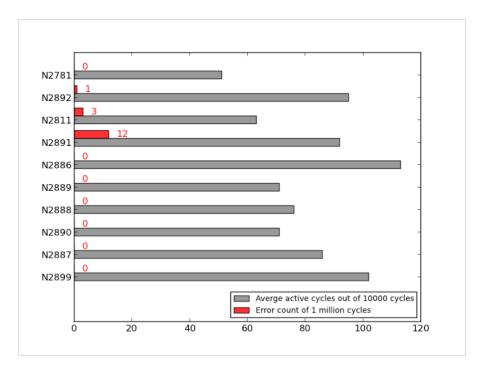

| Figure 18: Benchmark C1908 outputs with the average active cycles out of 10,000 cycles (using 100 simulation trials), and the total error counts for 1 million cycles at clock period of 1.7 ns.                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

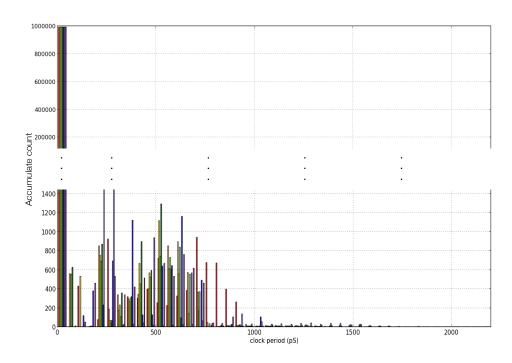

| Figure 19: Benchmark C1908 settling time histogram of each error-possible PO. The x-axis is the settling time in picoseconds, and the y-axis is the accumulated number within each bin                                                                                                                                |

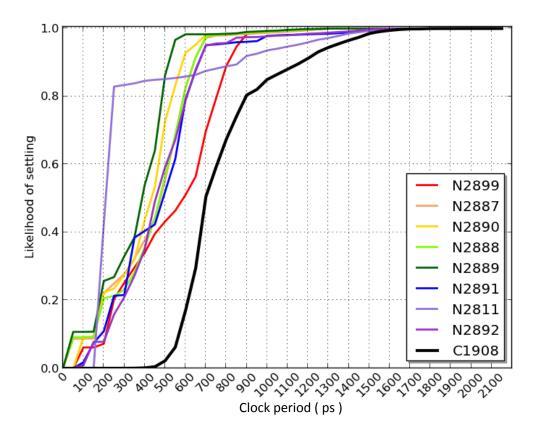

| Figure 20: Benchmark C1908 stablization probability of each error-possble PO45                                                                                                                                                                                                                                        |

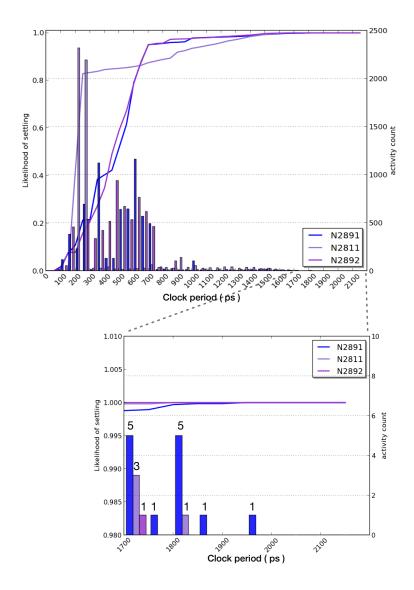

| Figure 21: Benchmark C1908 settling time histogram and stabilization probability density function of outputs N2891, N2911, N2892                                                                                                                                                                                      |

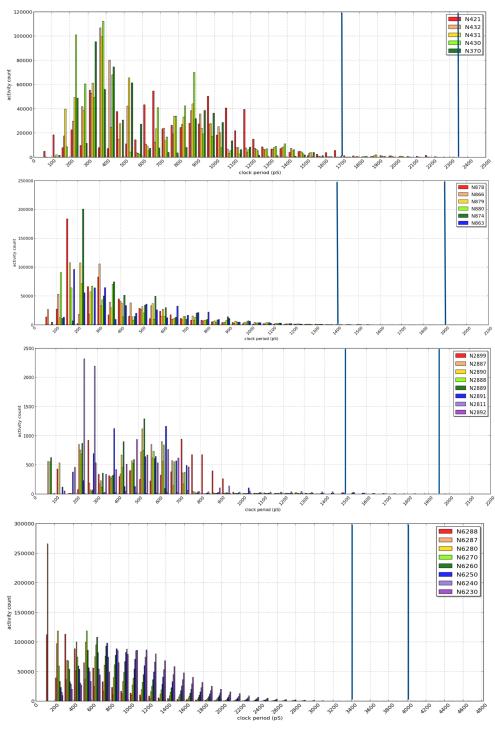

| Figure 22: Outputs settling time histogram with 1 million random input vectors of four benchmark circuits C432, C880, C1908 and C6288.                                                                                                                                                                                |

| Figure 23: Zoomed settling time histogram between 70% of orignal clock to the error-free clock of four benchmark circuits                                                                                                                                                                                             |

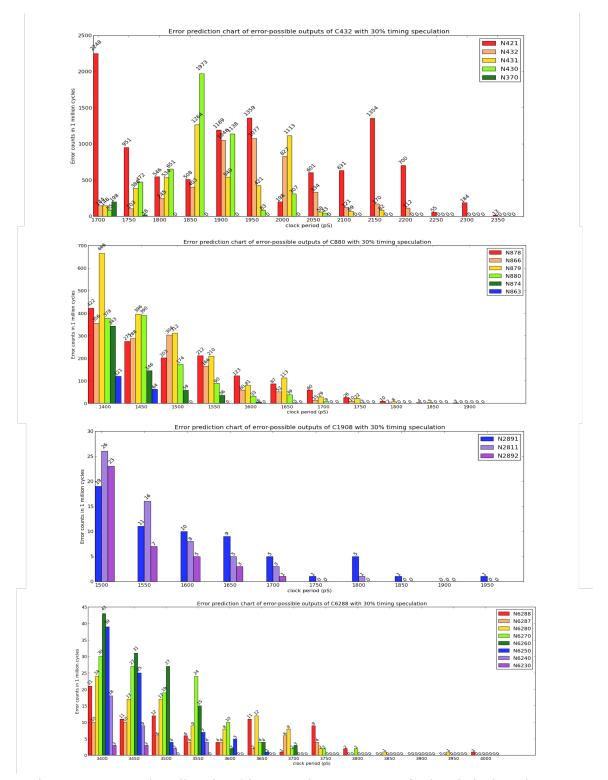

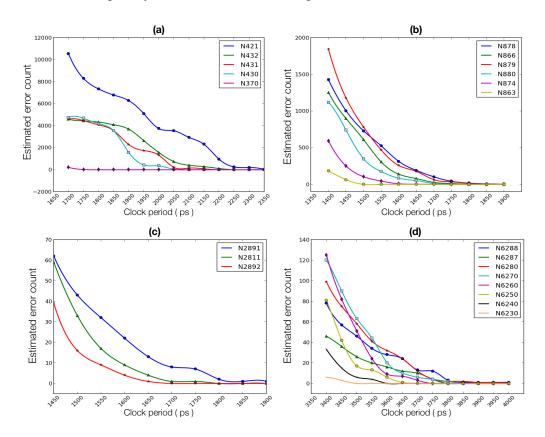

| Figure 24: Estimated error count of each error possible outputs of (a) C432, (b) C880, (c) C1908, and (d) C6288, from 70% of original clock period to the error-free clock period                                                                                                                                     |

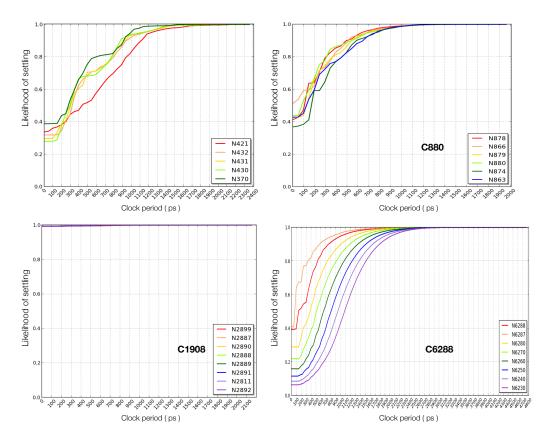

| Figure 25: The stabilization probability of four tested benchmark circuits for the given workload from start to end of the clock period.                                                                                                                                                                              |

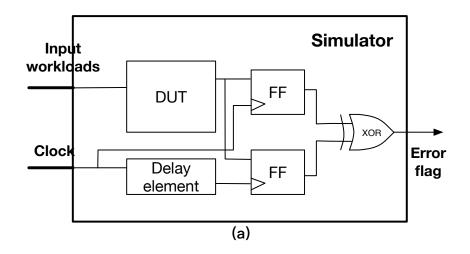

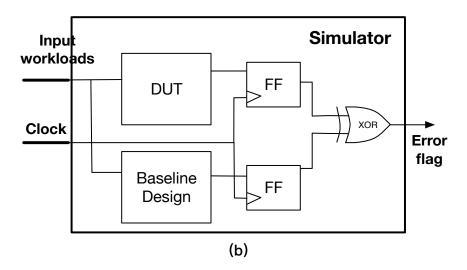

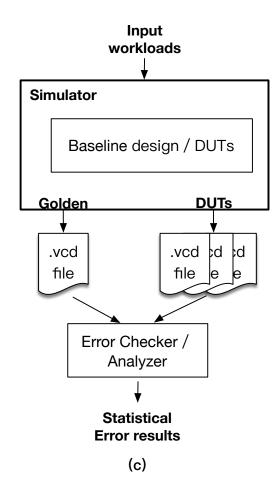

| Figure 26: The general structure of (a) transition detection method                                                                                                                                                                                                                                                   |

| Figure 27: The general structure of (b) duplication module/path method                                                                                                                                                                                                                                                |

| Figure 28: The general structure of (c) proposed off-line error checking method                                                                                                                                                                                                                                       |

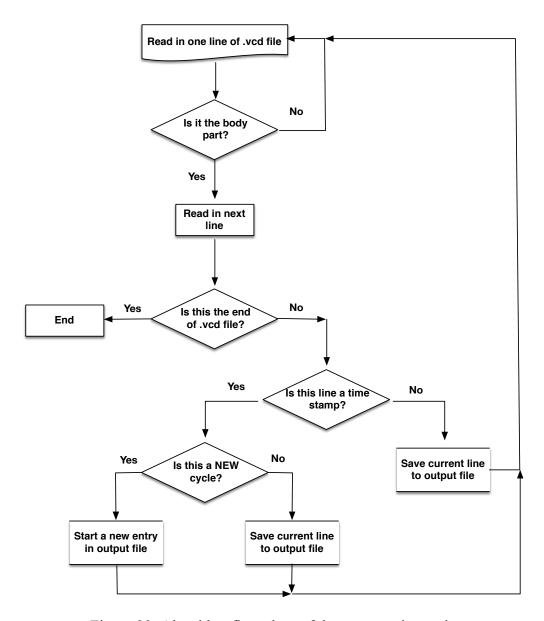

| Figure 29: Algorithm flow chart of data preparation script.                                                                                                                                                                                                                                                           |

| Figure 30: The example of partial activity file extracted from .vcd file                                                                                                                                                                                                                                              |

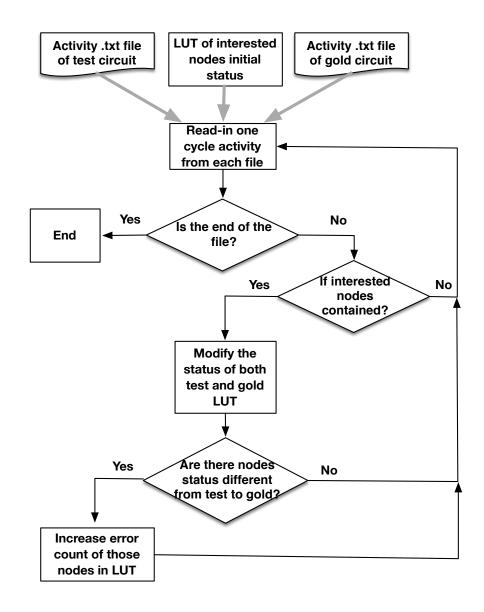

| Figure 31: The flow chart of the Extract and Compare script's algorithm                                                                                                                                                                                                                                               |

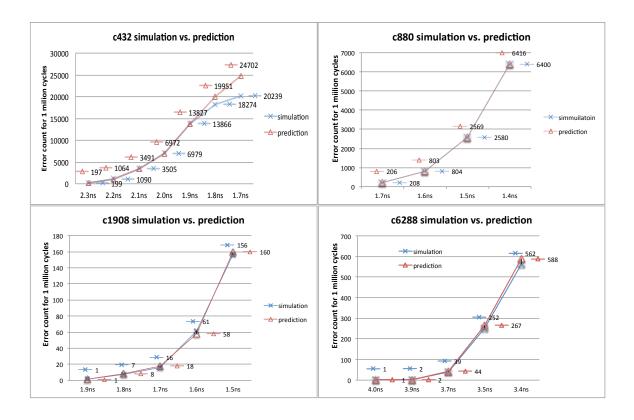

| Figure 32: The comparison between simulated results and total error estimation trends of four tested benchmark circuits.                                                                                                                                                                                              |

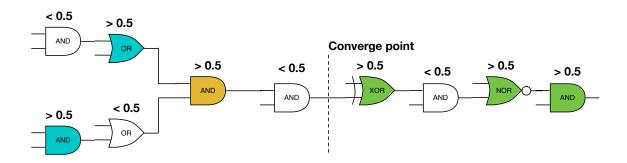

| Figure 33: A partial circuitery to differentiate three types of critical cells that are going to be replaced in this work                                                                                                                                                                                             |

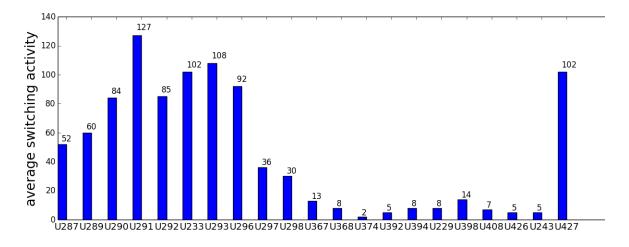

| Figure 34: Benchmark C1908 critical path's cells activity                                                                                                                                                                                                                                                             |

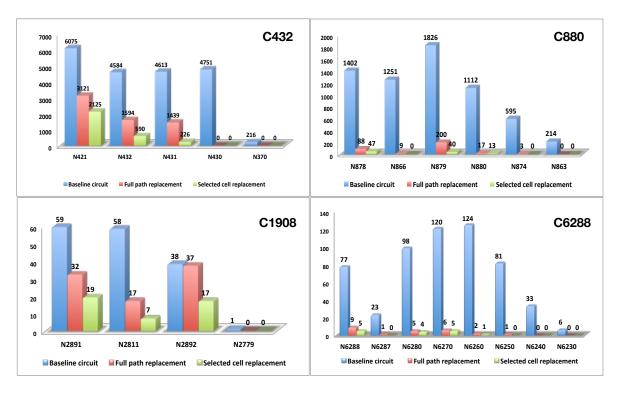

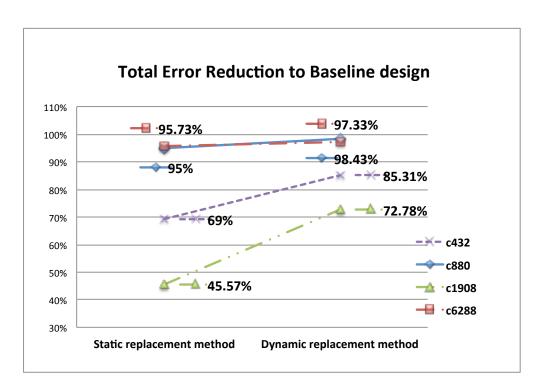

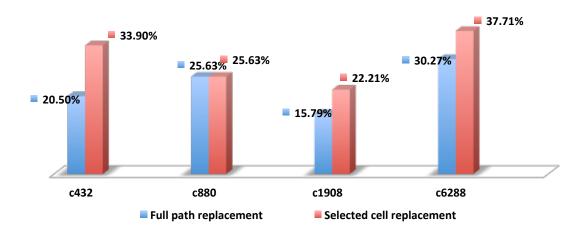

| Figure 35: Error counts of each error-possible PO before and after error reduction method Full Path Replacement and Selected Cell Replacement. The operating clock period of C432 is 1.7 ns (70% of 2.41 ns), C880 is 1.4 ns (70% of 2.01 ns), C1908 is 1.5 ns (68% of 2.2 ns), and C6288 is 3.4 ns (70% of 4.82 ns). |

| Figure 36: Total error reduction improvement from Full Path Replacement to Selected     |      |

|-----------------------------------------------------------------------------------------|------|

| Cells Replacement, when operating at 70% of original clock period                       | 72   |

| Figure 37: Error Free speed up comparison of Full Path Replacement method and Selection | cted |

| Cells Replacement method.                                                               | 73   |

#### CHAPTER I

## INTRODUCTION

With nanometer fabrication technologies, system-on-a-chip (SoC) design enables the potential of billions of transistors to implement a wide range of functionality. But along with the size scaling, transistors are becoming more sensitive to environmental conditions [1], within die variations [2][3], and even input workload variations. Designs reliability has become a greater concern for integrated circuits (ICs) [4][5]. The design corners are analyzed to determine the worst-case delay possibility. Based on these design corners, designers include additional timing margins as a guard band on critical paths. However, using the worst-case design plus guard bands can be very pessimistic, which translates into a loss of performance while executing real applications [6].

#### **Better-Than-Worst-Case Design**

To avoid performance loss because of infrequently-occurring, worst-case scenarios, Better-Than-Worst-Case (BTWC) design was introduced to bridge the gap. It is a design style that was first introduced by Bob Colwell, architect of the Intel Pentium Pro and Pentium IV processor. A traditional design methodology sacrifices performance to contain the extreme cases, so as to ensure an error-free design. The essential idea of BTWC design emphasizes operating on average-cases. BTWC design improves performance by allowing certain timing errors to occur during the normal operation, while preserving the correct operation by adding error detection and correction to the

design. By controlling the probability of the timing errors to a desired level, a trade-off can be made that results in an overall net performance gain with the error correction penalty.

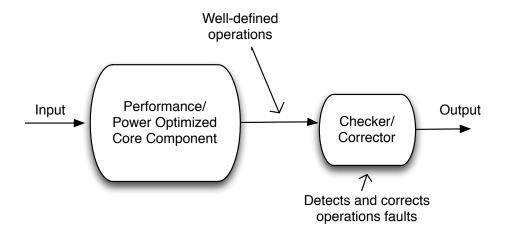

Figure 1 illustrates a general approach for BTWC design that includes a core computational component coupled with a checker mechanism that validates the semantics of the core's operations [8]. The additional circuitry of a BTWC design will consume extra power and take time to correct any errors. Thus, several features the Checker/Corrector must be considered: (1) small area, (2) power efficiency, and (3) fast correction capability.

Figure 1: Block diagram of BTWC design general structure

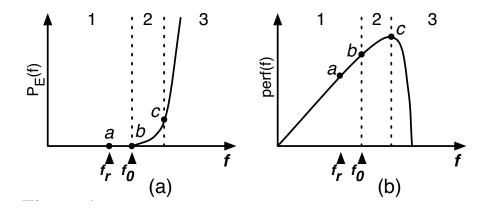

Figure 2(a) is an example of a critical path delay distribution of a circuit under a certain workload. Figure 2(b) shows the change of the delay distribution of the same path after considering all types of variation. Instead of using clock l' as operating clock frequency, BTWC design will select clock l to operate at an ultra-high speed, as shown in

Figure 2(b). The gray area represents the error probability. Traditional designs will require a slower clock frequency (i.e., a longer clock period) to avoid errors caused by the probability within the gray area. The advantage of BTWC design is the capability to derive additional performance based upon typical operation cases, and use the error detection and correction (EDAC) circuitry to handle the errors that occur occasionally. However, it will always need a checker/corrector module as long as it contains the possibility of errors. The extra circuitry of the EDAC module will consume extra power and take time to correct any errors. Thus, making the EDAC module small and efficient is important, but selecting a well-balanced operating clock frequency to keep the errors at an ideal level is also the key to maximize performance gain.

Figure 2: An example of critical path delay distributions: (a) Before the variations and (b) After the variations [7].

The operating clock frequency can be categorized into three regions, as illustrated in Figure 3. **Region One** is the error-free zone, where the clock frequency is usually selected as shown as point *a*. **Region Two** is where applying timing speculation has a positive performance gain. Timing errors begin to appear beyond point *b*. Point *c* is the optimized clock frequency to maximize performance. **Region Three** is where performance gain becomes negative when applying timing speculation. BTWC designs work within Region Two, therefore identifying the point *c* is the ultimate goal of BTWC design.

Figure 3: An example to illustrate the relationship of the timing error probability with circuit performance (a) Timing error probability versus clock frequency, (b) Circuit performance versus clock frequency [8].

## Variations That Impact Timing

The guard-band is the traditional design approach that tries to contain the timing uncertainties with extra design space. Those timing uncertainties are mostly caused by all kinds of variations, which influences on circuit timing. They can be categorized into static and dynamic sources.

#### Static variation sources:

Static variation does not change with time and depends on physical factors, such as internal connections and device dimensions. The geometry of the circuit's layout and structure determines the operational parameters. Physical parameter variations (e.g., critical dimension, oxide thickness, channel doping, wire width, wire thickness) lead to electrical parameter variation (e.g., saturation current, gate capacitance, threshold voltage, wire resistance, wire capacitance), and electrical variations result in delay variation. The inability to control precisely the fabrication parameters during manufacturing is called process variation [9]. The partially correlated process variations make the problem complicated to solve. A model of process variation and a model of timing errors for a processor's microarchitecture was described in [7]; it predicts the failure rate of micro-architectural blocks as a function of clock frequency and the amount of variation. A novel approach was proposed in [10] that isolated the failing path to avoid timing errors caused by process variation for fabricated chips.

## Dynamic variation sources:

Dynamic variations, on the contrary, are time-related and depend upon the operating conditions, like the fluctuation of: (i) V<sub>cc</sub> droops, (ii) temperature, (iii) transistor drain current, (iv) cross-coupling capacitance, and (v) multiple inputs switching (MIS) in logic gates [11]. V<sub>cc</sub> droops are induced from the internal switching activity, and lead to current transients. Dynamic voltage (IR) drop under real switching activity was analyzed in [12]. Temperature depends on input workload, environmental conditions, and heat-control methods. An adaptive system was discussed in [1] that accurately estimates

Transistor drain current aging is related to the gate bias and temperature. Cross-coupling capacitance change due to the adjacent wires switches will cause RC delay on the wire.

MIS is related to input workload that affects the circuits' internal activity and the settling time of the outputs. Paths with the same static propagation delay could have dramatically different distributions of their settling time because of the input workload variation.

There are researches like [13] and [14] who have studied the circuit behavior curve under input workload.

## **Motivation**

If the worst static propagation delay of an output is longer than the operating clock period, then there is a probability to observe errors at this output. But a timing error occurs only when the output settling time extends later than the specified clock period. However, when increasing the operating clock frequency, the error probability increases are not linear. Estimating error probability just based on the circuit's static delay information may lead to a severe misunderstanding of the circuit's behavior. The error probability is highly related with the output settling time and the operating clock period. As introduced earlier, there are many factors, including input workload variation, that could influence an output settling time. Most of influences are subtle. It is the input vectors that determine the path usage. Together with circuit's previous status, the basic shape of the circuit dynamic activity curve is formed.

BTWC design is all about finding the optimal operation clock frequency. Timing speculation is associated with errors, but a well-balanced operating clock frequency will

contain the error rate at a desired level, so as to realize performance improvement. An accurate error estimation method based on the circuit's dynamic behavior gives BTWC designers insight on how the error trends occur with the increase of clock frequency.

The error rate from each output may vary with different input workload. When a circuit operates at an ultra-high clock frequency, an understanding of the dynamic activity for each circuit path will help to identify the most error-prone output, thereby making the error reduction more efficient. BTWC design requires error estimation for all potential clock frequencies for the given input workload. Therefore, a design flow for BTWC design has been developed to extend the capability of commercial electronic design automation (EDA) tools for dynamic path activity and output settling analysis. The design flow utilizes customized scripts that process standard output files from the commercial EDA tools.

#### Research Contributions

This research focused on performance improvement in digital integrated circuits (ICs) by considering path activity behavior under a given input workload. Timing analysis and timing closure are critical steps in digital circuit design. Many factors affect the delay distribution of the outputs, but the input workload determines the basic shape of the distribution. The longest static delay path(s) may not be very active for a certain input workload, and therefore would not frequently generate timing errors. Obtaining the actual delay distribution of the outputs for given workload could help designers to estimate the error rate for each output so as to select the well-balanced operating clock frequency, which is the fundamental challenge for BTWC design.

This work contributes the following: (1) The Off-line error checking method that enables detailed statistical analysis on selected cells activities. Design and verifications does not require test bench that compares models operating in system work; (2) The All-clock-frequency error estimation method that predicts error rate for all-possible operation frequency of each PO. Characterizes each PO settling curve under given input workload. Identifies the typical-case error contributor according to circuit internal activity. (3) Dual- $V_t$  method for effective error reduction on selected cells. The selection focuses on the fan-in cone of identified error contributors by using weights determined with circuit activity level. [15].

The rest of this dissertation is organized as follows. Chapter II describes related methodologies and related backgrounds, including: (1) static timing analysis (STA) and statistical static timing analysis methods (SSTA), (2) path stabilization probability analysis for given input workload, and (3) general EDA design flow. Chapter III provides information about the research methodology, simulation setup environment, and the overall design flow used in this work. Chapter IV describes the error-estimation method and the error-checking method used in this research, which aided in identifying the greatest error-contributing primary outputs (POs) and the critical standard library cells that contribute to the propagation delay for the given input workload. Chapter V describes the error reduction method of using multi-threshold standard cells and analyzes the error-reduction results. Chapter VI summarizes the work and offers some future extensions of this work. The customized Python scripts for error checking and error estimation are provided in the Appendix.

#### CHAPTER II

#### BACKGROUND AND RELATED WORK

Device reliability is an important concern for the operation of integrated circuits (ICs). Design margins are incorporated into the final design to ensure an error-free IC. BTWC design can be used with timing speculation to reclaim the lost performance when incorporating the design margins associated with corner cases. Timing analysis and path activation probability analysis are necessary to prepare for BTWC design. Understanding the circuit behavior under typical cases is the key to success. The timing error rate of a BTWC design needs to be controlled at an optimized level in order to have an improvement in performance while avoiding the negation of the performance gain because of the error correction penalty.

This chapter provides background on techniques for timing analysis. It also discusses the analysis of path activation probability, which is used to determine how the input workload can affect the visible errors at the primary outputs. The chapter also reviews techniques for timing speculation with error detection and correction (EDAC) circuitry.

#### Timing Analysis

The original Static-Timing Analysis (STA) was brought into very-large-scale-integration (VLSI) chip design in the early 1990s, and it has been one of the successful and matured tools in digital circuits design [16]. This timing analysis tool could be

widely accepted because the runtime is linear to the circuit size, and the results are relatively safe for traditional digital circuit design. The original STA tools are deterministic and calculate circuit delay with one specified corner case to represent the design boundary. However, the transistor size scaling amplified the impact from process variation. The deterministic attribute of traditional STA causes inaccuracies for digital circuits.

The fundamental weakness of traditional STA is that there is no statistically rigorous method for modeling multiple corner files. Therefore, Statistical-Static-Timing-Analysis (SSTA) emerged to improve the timing analysis method. Rather than giving a single result, SSTA evaluates the timing of gates and interconnects with probability distributions. Over the past decade, there are hundreds of papers published in this field, and D. Blaauw et al. [16] discussed the evolution of STA to SSTA. The basic goal of traditional STA is to find the delay of the longest path in the circuit, and the SSTA aims to find the latest arrival-time distribution of the output. The SSTA can be generally categorize into three approaches:

1. Numerical-Integration Method: The delay distribution of a set of paths that approach the maximum delay can be expressed as a function of physical parameters in order to select a certain region under a specific circuit delay. That region is then integrated numerically to explore the possible physical parameter space, and then compute the circuit's statistical results of the timing. This approach is generic and can include different types of models to account for process variation, but the significant amount of computation time

- is a problem, especially for a well-balanced circuit with a large set of paths that approach the maximum delay.

- 2. Monte Carlo simulation method: The basic idea behind this approach is to perform sufficient independent sampling for the circuit delay using traditional STA using the probability distribution function (PDF) of the physical parameters. The circuit delay distribution can be found by sweeping the timing constraint. Like numerical integration, this method is completely general. Because the traditional STA methods are mature, Monte Carlo simulation is faster than the numerical integration method. However, due to the inner loop calculation inside of the simulation for STA, the run times are still significant. The second weakness of Monte Carlo simulation method is the difficulty to perform incremental analysis. If any change is made to the circuit, then the whole simulation procedure needs to be restarted to obtain an updated circuit delay distribution.

- 3. *Probabilistic analysis method:* Unlike the previous two methods that are based on the sample space, this method models the gate delay and the arrival time of signals with random variables. There are two main approaches to implement probabilistic analysis.

- a. Path-based approaches: This approach selects a set of most-likely critical paths, and then adds the gates and interconnection delays of each path within the set to approximate the circuit delay distribution.

The paths selection must be done before the statistical analysis, so the accuracy of the approximation depends on the selection of likely high-

delay paths. This approach, therefore, has two split steps: First, find the paths, and second, calculate the path delay. The difficult task is how to find the best set of paths.

b. **Block-based approaches:** This approach is based on the traditional STA algorithm, and deals with the circuit graph in a topological manner. To compute the arrival time for each node, the edge delay is added with the source node arrival time for each fan-in edge, and then the latest arrival time is selected as the final result for each node. The block-based approach has a runtime advantage, especially because incremental analysis is allowed by using this method.

Although SSTA makes the analysis more comprehensive, there are challenges and limitations associated with it. It is too complex when dealing with realistic delay distributions. It is also very difficult to apply within an optimized algorithm or flow.

Both of traditional STA and SSTA method are designed to avoid the impact from input vectors. It is good for traditional design because including rare cases when testing design limitations makes the design more reliable. However, this advantage becomes an obstacle when using a BTWC design style that optimizes a design according to circuit behavior for typical input workloads.

## Path Activation Probability Analysis

Because the rare cases are not emphasized for BTWC design, information from regular timing analysis tools are not enough for BTWC design. Two Primary Outputs (POs) with the same static path delay, according to timing analysis tool, could have

dramatically different distributions of path stabilization (i.e., settling time) in a real application [17].

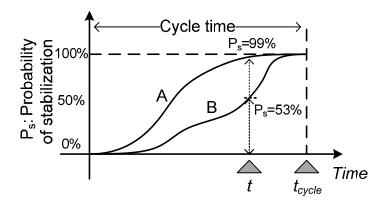

Figure 4: Dynamic behavior curve of two paths with the same static delay time. [17]

Figure 4 shows an example that the path delay time does not equal to the path settling time. The labels A and B represent two outputs that have the same worst-case propagation delay. However Output A and Output B have distinct probability curves for their settling time. With the same input workload, Output A has a 99% probability that it will settle by time *t*, while Output B has a 53% probability to be settled at time *t*. This means Output B is more dynamically critical and should be weighted higher when analyzed for errors during the BTWC design process. By enhancing the speed along the path to only Output B, assuming the circuit only has two paths, then most errors will be reduced, and the circuit could operate at cycle time *t* with very little penalty for error correction.

The circuit's dynamic stabilization curve will be affected by many types of variations, but the curve's basic shape is decided by the input workload. A rigorous analysis of path activation probability, which describes the typical dynamic behavior of

the circuit's response to a common-case workload, would provide insight that helps the BTWC designers to maximize the performance gain. Wan and Chen proposed several circuit optimization techniques for timing speculation based on the circuit's dynamic activity in [17], [18], [19].

In [18], Wan and Chen proposed a circuit-level optimization tool called DynaTune that combined TCF (Timed Characteristic Function) [20], an ATPG (automatic test pattern generation) method, and BDD (binary decision diagram) [21] to derive the circuit's dynamic behavior curve to understand the impact of input workload on a circuit's settling time; based on that information, it selects a targeted operating clock frequency and the corresponding settling probability. Then, it selectively resynthesized the cells along the timing-critical paths that exceed the threshold for delay and activity probability so as to improve performance while mitigating errors. The timing speculation techniques used in DynaTune are the Razor logic [22] (which is discussed in more detail later in the chapter) or the Telescopic Unit [23].

DynaTune has several drawbacks: (1) The use of Global BDD is only suitable for small circuits; (2) TCF analysis is sensitive to the node's value, and it requires structural information of the circuit to perform the analysis. (3) During the analysis, the input was set to a static probability, which likely is not representative of the real application input workload, which could have distinct phases of operation.

Wan and Chen also purposed a method to analysis circuit-level dynamic behavior with new data structure, called timed Ternary Decision Diagram (tTDD) [17]. The tTDD is created based on the TDD and TCF. Ternary Decision Diagram is similar to Binary Decision Diagrams (BDDs). BDD's basic idea is Shannon expansion, and it is a graph

based rooted but directed data structure that is used to represent Boolean functions. Bryant [24] added restrictions on the ordering of decision variables in vertices, which enables BDD to manipulate representations in a more efficient manner. Ternary decision diagram, As discussed by Sasao in [25], has three possible outgoing branches for each node, which solves BDD incapability of modeling not settled cases. But this method requires circuit partitioning, and the partitioning algorithm is crucial because it will affect both structure correlation and calculation cost. The estimation error complexity becomes relative high when dealing with larger circuits. Detailed timing model that extracted from standard delay format (SDF) was used in this method, but input change impaction on cell delay did not include yet.

CCP [19] resynthesizes a circuit according to a probabilistic manner that creates functionally equivalent but shorter logic paths for paths with high activity. The rarely active paths are resynthesized with a longer delay. To identify the common cases, a global behavior profile is obtained by generating a set of primary input vectors according to given typical case characteristics [8] [26], and then it uses the synthesis engine in ABC [27]. Input vectors are selected according to the typical-case characteristics. The global behavior profile can be reused for all sub-circuits. To promote the common case, the TCF information of common cases is used to build redundant sub-functions for common cases, and the sub-functions are merged into the original design to improve performance.

#### Timing Speculation Methodologies And Error Resilience in BTWC Design

A BTWC design can be separated into two main parts: Timing speculation part and Error resilience part. Timing speculation is the part to improve the performance (e.g.,

increase speed, or reduce power usage), which could be implement at different design level. Error resilience part aims to preserve the reliability of the design. In this work, we are focus on the circuit-level timing speculation, and the most popular one is Razor logic structure, like Razor [28], Razor II [29].

## Timing speculation methodologies:

Researchers at the University of Michigan developed a circuit-level approach called Razor to implement Dynamic Voltage Scaling (DVS) processors [22][30][29]. It combines a circuit-level error detection mechanism with a microarchitecture-level error recovery technique.

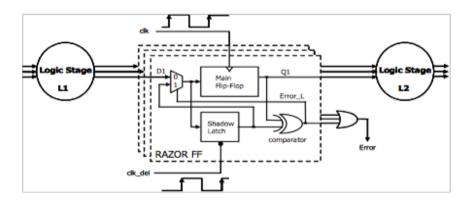

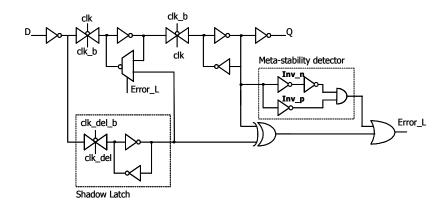

Razor [22] proposed a more aggressive but realistic approach to DVS. It tunes the supply voltage by monitoring the error rate during the operation. The timing error detection is implemented by using a delayed latch, called a shadow latch, to compare with the corresponding state element in the design. The value in the shadow latch is guaranteed to be correct since it uses the worst-case timing (Figure 5). Figure 6 shows how the Razor flip-flop was designed. When an input signal transitions at the same time as the clock, meta-stability may occur in the Razor flip-flop.

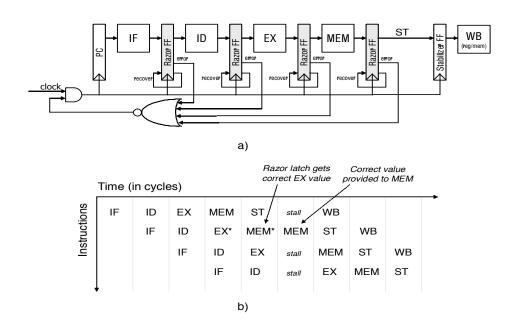

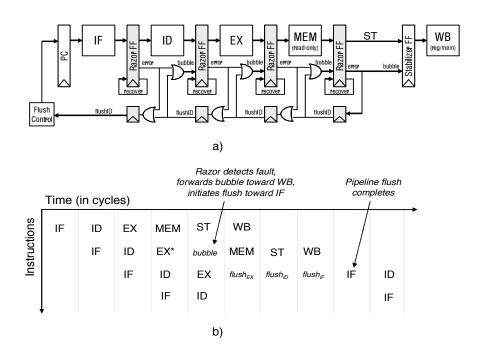

Razor relies on both the combinational circuit and the architecture for an efficient EDAC method. It has been applied with a pipeline structure to correct timing errors. Two recovery mechanisms have been proposed [28]. The mechanisms use either clock gating or a counterflow pipeline, as shown in Figure 7 and Figure 8 respectively. The clock gating mechanism simply asserts a global stall for all stages in the next cycle after the error flag is issued. However, global clock gating is not ideal for the clock tree, so the counterflow pipelining approach is introduced. When an error is detected, a bubble signal

propagates to next stage, and a pipeline flush is initiated from this stage back to the first stage. The pipeline restarts from the first stage.

The voltage is increased or decreased according to the error rate. A low error rate means that the voltage could be reduced. A high error rate suggests that the supply voltage violates the timing constraints too much and should be increased. A properly selected reference error rate is very important to maximize the performance gain.

Figure 5: Block diagram of Razor logic. [22]

Figure 6: The circuit-level schematic of the shadow latch used in Figure 5. [22]

Figure 7: The pipeline recovery using global clock gating. (a) The pipeline structure. (b)

The pipeline operation timing. [28]

Fig. 8: The pipeline recovery using counterflow pipelining. (a) The pipeline structure. (b) The pipeline operation timing.[28]

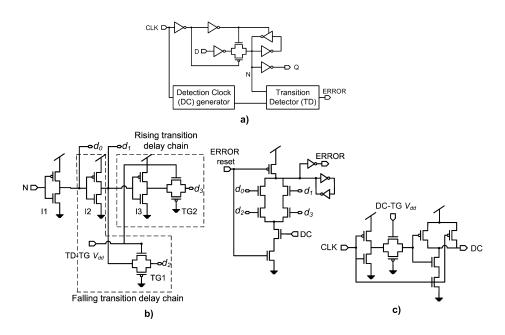

The original Razor design not only detects errors but also restores the correct results from the shadow latch. However, generating the restore signal from the pipeline makes it harder to implement an aggressively clocked microprocessor. Razor II [29] proposed a new flip-flop that only detect errors, and uses the technique of architectural replay to handle the correction. Because it uses architectural replay, the Razor II flip-flop is smaller in size and complexity but pays a higher penalty on recovery, as measured by the throughput, Instructions Per Cycle (IPC). The advantage of architectural replay is that it is a mature technique used in many existing speculative processors [31].

Figure 9: Circuit-level schematic of Razor II flip-flop. (a) Flip-flop schematic. (b) Transition detector schematic. (c) Detection clock generator. [29]

The Razor II flip-flop is a positive level-sensitive latch. Since it is level-sensitive, when the clock is high, any input change will be captured. In Razor II, any transition that

happens during the latch's transparent phase is considered an error. Figure 9 illustrates the circuit structure of the Razor II flip-flop.

Other than Razor and Razor II, there are several EDAC flip-flops that use transition detection with time borrowing (TDTB) as in Figure 10(b), and double sampling with timing borrowing (DSTB) as in Figure 10(c). These techniques were proposed to solve the meta-stability issue that exists in the previous Razor design [32]. Figure 10(a) shows the regular structure of Razor flip-flop.

Figure 10: Different ways to implement Razor flip-flop to detect timing errors. [32]

TIMBER [33] proposed two timing elements to provide online masking of timing errors for a pipelined structure. The author found that timing errors due to dynamic variations often only span one pipeline stage on successive clock cycles and therefore can be masked by timing borrowing. TIMBER has flip-flop version and latch version, and both are illustrated in Figure 7 and Figure 8. When **EN** is high, the TIMBER flip-flop works in the timing-borrowing mode. Node **M0** and **M1** are designed for error checking. If they are not the same, then the value sampled by **M1** will mask the previous value after the delay time. The delay time is controlled by **S1S0**. Similar in TIMBER latch, when **EN** is high, the latch is in the timing-borrowing (TB) mode. The input value is latched by

transmission gate **M** during the **TB** time interval, while transmission gate **L** is always on for entire checking period in the timing-borrowing mode. If signal arrives after the **TB** interval ends, then the timing error will be masked without an error flag. If signal switching occurred during **ED** interval, then the error flag will be inserted. Both the TIMBER flip-flop and the TIMBER latch do not have meta-stability issue.

Figure 11: Schematic of TIMBER flip-flop. (a) Main flip-flop part. (b) Clock signal control and generating part.[33]

Figure 12: TIMBER latch schematic. (a) Main latch part. (b) Clock signal control and generating part.[33]

TEAtime [34] (Timing error avoidance) uses a methodology that in situ adjusts the clock frequency to avoid operating a circuit at an unnecessarily low frequency. The longest critical path is used as a checker for the main circuitry to ensure correct operation, shown in Figure 13. A toggle flip-flop feeds into the checker to test whether the results could propagate beyond the longest delay under the current clock period. When the checker remain equal, the counter increments, the voltage increases, and the clock frequency increases. The clock frequency can be decreased by implementing the process in reverse. A bi-directional counter, a digital-to-analog (D/A) converter, and a voltage-controlled oscillator (VCO) are used in TEAtime. The prototype design can experience meta-stability.

#### Error resilience mechanisms:

Error resilience is another part of BTWC designs. The mechanism of each methodology could be categorized as follow:

- 1. *Error detection* + *Rollback/Instruction replay*: Normally the approaches that use this scheme include duplicated registers or a transition detection mechanism with a delayed clock to capture signals that violate timing. To recover from the timing errors, the main system is suspended and restored to the correct value from either the duplicated register or a replay of the instruction. Pitfalls of this scheme normally are: (1) a limited detection window, (2) a prolonged hold time requirement, and (3) the issue of meta-stability.

- 2. *Error masking*: For a given logic circuit, errors can be masked by an approximate logic circuit that predicts the correct value [35], [36]. For every output, the logic could be either expressed with a 0-implication or a 1-implication approximate function. These functions are used to detect 1-to-0 or 0-to-1 errors. The type of approximate function for the output is determined by computing the dominant type of errors.

The work for this dissertation first needed to identify the optimized operating clock frequency (with the assumption of a known threshold value for maximum error tolerance). Then, the design is modified to reduce errors according to the typical activity for the given input workload. The traditional EDAC modules cannot provide an estimation of the error rate for a speculative operating clock frequency unless the simulation is actually performed. However, conducting simulation sweeps through all-

possible clock frequencies is too inefficient to accept in a real-world design flow.

Therefore, an all-clock-frequency error estimation method has been developed as part of this dissertation research, which enables an accurate error prediction for all-possible speculative operating clock frequencies of each primary output with only one simulation at the original, error-free operating frequency.

Table 1: Summary of several EDAC methodologies

|                 | Detection<br>Methods        | EDAC type                                               | Recovery<br>Method                        | Application<br>Structure    | <b>Pros and Cons</b>                   |

|-----------------|-----------------------------|---------------------------------------------------------|-------------------------------------------|-----------------------------|----------------------------------------|

| Razor           | Shadow latch                | Detection                                               | Restore from register                     | Pipeline                    | Meta-stability;<br>Complexity          |

| Razor II        | Transition detection        | Detection                                               | Architecturally handle instruction replay | Pipeline                    | Complexity                             |

| Bubble<br>Razor | Shadow latch                | Detection                                               | Local replay                              | Pipeline                    | Less hold time to restore              |

| TIMBER          | Duplicate paths             | Partial Error<br>detection;<br>Partial Error<br>masking | No                                        | Standard sequential circuit | Limited functions                      |

| TEAtime         | Monitor<br>critical<br>path | Error<br>masking                                        | Instruction replay                        | Standard sequential circuit | One path<br>monitor;<br>Meta-stability |

## Evaluation Methods For BTWC Design

Circuit's performance can be evaluated from three aspects: (1) operational speed, (2) power consumption, and (3) operational reliability. BTWC designs attempt to either enhance computational efficiency or lower the energy usage while maintaining a robust design.

## Performance:

The metric for operational speed can use the clock frequency (f), but normally the throughput is used to measure the performance of a BTWC design. The input may need to stall several cycles for the correction penalty when a timing error occurs in a BTWC design. For a traditional design, all the primary outputs (POs) are bounded with the desired cycle time ( $T_{cycle}$ ), so the probability ( $P_s$ ) of each PO to stabilize (i.e., settle) within the cycle time is 1. Therefore, assuming that one operation is completed per cycle, the throughput for the traditional design should be [19]:

Throughput =

$$P_s \cdot f = f = 1/T_{cycle}$$

However, idea of BTWC design is to make the highly active paths with a long delay to settle before the cycle time, while permitting some of the less time-critical paths to exceed the boundary on occasion. Thus, considering the error correction penalty (r), the equation to calculate BTWC design throughput is [19]:

Throughput =

$$P_s \cdot f + (1 - P_s) \cdot \frac{f}{r}$$

,

and the energy cost of BTWC designs is inversely proportional to the throughput.

#### Power:

The power consumption in the conventional CMOS digital circuit can be separated into three types of dissipation [37][38][39][40]: (1) switching power, (2) short-circuit power, and (3) leakage power consumption. The switching power represents the power dissipated during the signal transitions when energy is drawn from the power supply to charge-up the device capacitances. Short-circuit power is produced during the moment that both the PMOS network and the NMOS network are simultaneously on in CMOS

logic. The MOSFETs in CMOS logic normally will have some non-zero reverse leakage and sub-threshold current, which causes the leakage power dissipation. The sum of switching power and short-circuit power can be categorized as dynamic power, while the leakage power is also called static power dissipation [41]. Dynamic power is dominated by switching power, while leakage mainly comes from the sub-threshold leakage current. The static power increases faster than dynamic power with the shrinking of feature size. Reducing supply voltage is an efficient way to reduce total power consumption, but it may lead to timing delay and exponential leakage increase [29][31]. Multi-threshold voltage, where a low-threshold voltage is used with cells on critical paths and a high-threshold voltage is used for the other cells, is a widely accepted technique to reduce power [43]. It has also been used in BTWC design to improve power.

## **Reliability:**

The reliability in BTWC design focuses on the detection and correction of timing errors. Because of the nature of BTWC design, timing errors would invalidate the results during the operation. An effective error detection and correction (EDAC) mechanism is crucial. The evaluation criteria includes answering the following questions:

- How complex is the implementation of the method?

- What penalty is the design going to pay?

- What is the detection/correction rate for the method?

Timing speculation is the idea where various methodologies are used to enhance the operational speed to the point where timing errors occur while equipping the design with techniques to detect and correct those timing errors [44][8]. Based on this idea,

BTWC design allows the timing error rate to a certain point where the performance gain (either in speed or in power) is effectively balanced with the penalty cost for reliability.

BTWC design has adopted a cross-layered approach [45][46][47] from the architectural level down to circuit level.

# <u> Multi-threshold Technology In VLSI Designs</u>

Threshold voltage is the minimum voltage applied on a MOSFET gate to create a conducting path between the source and the drain. The MOSFET acts like a switch ideally. However, during the OFF stage, there are mobile carriers (i.e., electrons or holes) that travel through the semiconductor junctions, which is called sub-threshold leakage. With the technology scaling, the leakage power consumption is now a major concern for current semiconductor industry, and the sub-threshold leakage is the main contributor to the leakage current.

The sub-threshold leakage is directly related to the threshold voltage as it controls the size of the depletion region. A higher threshold voltage could reduce the sub-threshold leakage, but it limits the cell's response speed. On the other hand, a lower threshold voltage reduces the propagation delay but will result in a dramatic increase of leakage power with such small geometry devices.

Many previous works studied how to use multiple threshold voltages on one design. Mutoh et al. [48] introduced the multi-threshold technology for 0.5-μm CMOS that uses low-threshold MOSFETs to enhance speed while high-threshold MOSFETs are used to reduce leakage power. Wang and Vrudhula [49] introduced a heuristic algorithm based on circuit graph enumeration to effectively reduce leakage power of CMOS digital

circuit without too much impact on speed. Wei et al. [50] proposed a dual threshold approach to reduce leakage power by assigning high-threshold voltage cells to non-critical paths, and using low-threshold voltage cells on critical paths, and introduced an algorithm to optimize the selection.

The tradeoffs for dual  $V_t$  CMOS circuits has been has been explored by Wang and Vrudhula in [51]. The detailed simulation has performed to investigate short circuit power dissipation of dual  $V_t$  technology, and the short current impact of low- $V_t$  MOSFETs on gate delay. Multiple power models of dual  $V_t$  technology create challenges to EDA tool development as well.

Jayakuamr and Khatri [52] prepared pull-up circuit and a pull-down circuit with different  $V_t$  standard cells for standby mode. After the traditional mapping using regular cells, they then replace the cells with prepared low-leakage cells according to the simulation results of each gate's output. The methodology is compared with regular multi-threshold CMOS methodology and shows better performance on leakage reduction.

Most of previous  $Dual-V_t$  /Multi- $V_t$  methodologies were targeted to reduce power consumption or to ensure resiliency when applying dynamic voltage scaling (DVS). In this research, the  $Dual-V_t$  technology will be used to adjust the timing of specific paths to precisely reduce timing errors during timing speculation.

## Timing Speculation vs. Instruction Speculation

Speculation could have different interpretations for people from different research fields. One ambiguity comes from the computer architecture field where researchers commonly refer to the speculative execution based on the branch prediction or out-of-

order executions. Based on the history of branch executions, the speculative execution schemes allow the instructions to be scheduled ahead when the outcome of a conditional branch has not yet been determined, in order to utilize the microarchitectural resources in a more efficiently way [31]. However, this widely used optimization technique in modern computer architecture shows security vulnerabilities in January 2018, which affects Intel x86 microprocessors, IBM POWER processors, and some ARM-based microprocessors. One of the vulnerability, Meltdown [53], occurs between memory accesses and privilege checking during instruction processing. The microprocessor's cache holds the unauthorized address because of the out-of-order execution, from which the data can be recovered. The other vulnerability, Spectre [54], uses the information leakage from branch predictions via cache timing as a side-channel attack to manipulate the target process.

The timing speculation discussed in this dissertation is approached from the circuit-level. The traditional clock frequency is bounded by the worst-case delays.

Operating the circuit at a higher clock frequency to gain execution speed is the purpose of circuit-level timing speculation. There is no structural modification to the circuit, or out-of-order instruction manipulation in this work to achieve circuit-level timing speculation. Therefore, it does not enable the side-channel attack that has been used for Spectre and Meltdown.

#### CHAPTER III

### RESEARCH METHODOLOGY AND BTWC DESIGN FLOW

This chapter introduces the details of the methodology used for the research in this dissertation. The chapter describes the simulation environment setup as well as the BTWC design flows used to evaluate the approach. Four benchmark circuits from ISCAS85 [48][49] were used to represent four different types of functions (Table 2).

Table 2: Overview of the circuits used in the analysis

| Name  | Function                        | Input # | Output # | Cell# |

|-------|---------------------------------|---------|----------|-------|

| C432  | 27-channel interrupt controller | 36      | 7        | 160   |

| C880  | 8-bits ALU                      | 60      | 26       | 383   |

| C1908 | 16-bit SEC/DED                  | 33      | 25       | 880   |

| C6288 | 16x16-bit multiplier)           | 32      | 32       | 2406  |

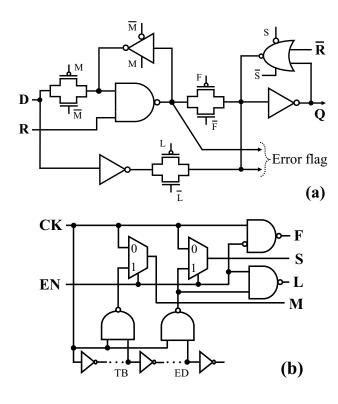

### General EDA Flow And The Design Flow Used In This Work

The General EDA flow with Synopsys tools [57] is shown in Figure 13 to give a brief introduction to using the Synopsys design tool kit. Circuit functionality is verified during RTL simulation. Design Compiler (DC) synthesizes the benchmark source file with standard cell modules to generate a gate-level netlist. IC compiler (ICC) performs Place-and-Route, which will generate accurate timing information and store the

information in the .sdf file. The post-simulations are performed in VCS with backannotated timing information (.sdf). The .vcd file stores the simulation results with all the switching activity information for the circuit across the entire simulation time; this file is the essential raw data for the research.

Figure 13: The customized EDA flow with Synopsys tools.

In Figure 14, the customized design flow used in this research is shown. The whole design flow uses the Synopsys Design tool suite (Design Compiler, IC Compiler, PrimeTime, and VCS) with the Synopsys 32-nm library and customized Python scripts to implement, simulate, and analyze the designs.

- After implementation with Design Compiler, the test circuit is place and routed by IC Compiler. The whole circuit delay information, including wire interconnection delay, is saved in the standard delay format file (.sdf file). The gate-level net-list from IC Compiler is simulated in VCS with timing information .sdf file back-annotated. After simulation, the value change dump file (.vcd file) is generated, which records all nodes' switching activity during the simulation time. For the same given input workload of a test circuit, each possible operating clock frequency will have a .vcd file.

- There are several customized scripts to process the .vcd files, which perform the following tasks: (1) Process the .vcd files to prepare and extract the important information for later use; (2) Produce error estimation for a specific speculative clock frequency based on the statistical histogram of each PO's settling time to identify the real error-contributing PO for the given workload; and (3) Calculate the desired internal cells activity level to identify the critical cells.

- According to the cell replacement rule, re-synthesize the test circuit with low threshold voltage (Low-V<sub>t</sub>) cells on identified critical cells.

- After the Dual- $V_t$  resynthesis method, use the proposed error-checking method to test the real error rate. The error-checking method uses the same activity .txt file processed from .vcd files as error-estimation. Compare the POs' settling status of the

speculative clock frequency's .vcd file with the golden copy's .vcd file cycle by cycle, and calculate the error count of the POs.

The details of each step are discussed in more detail in the following Chapters.

Figure 14: The proposed design flow chart.

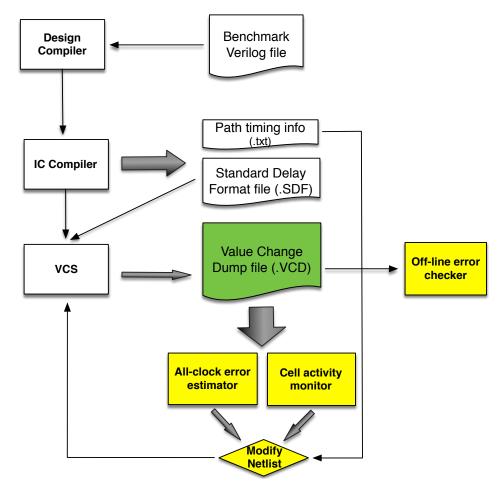

# Value Change Dump Files

The .vcd file was a significant component in this work. It was used not only for the error checking method, but it was also the basis for error estimation and other activity

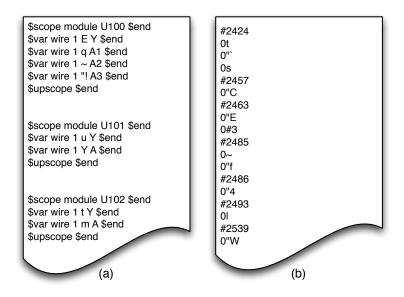

analysis in this work. The .vcd file contains both the switching activity and the timing information that is generated during the simulation. The .vcd file used in this work is generated from the Synopsys simulator. Figure 15 is an example of a .vcd file from an actual simulation. A .vcd file records the switching activity of all the nodes or a selected hierarchy. Figure 15(a) is the header file that defines the corresponding relationship between the node name and the symbol that is used later in the .vcd file. Each node has an assigned symbol. Figure 15(b) records the value change activity of all nodes throughout the simulation time. The entries starting with the symbol "#" are timestamps. The subsequent entries are the nodes that switched at the time point. The first digit is the current value of the node, and the remaining digits are the corresponding symbol of the node. The time unit is ps. One node may change multiple times within one cycle.

Figure 15: An example of value change dump file. (a) is the header part, and (b) is the body part.

With the understanding of the .vcd file contents, the special customized error estimator and error checker in this work are all based on the information contained in

.vcd file. More details about error estimation and error checking methods will be introduced in Chapter IV and Chapter V.

#### CHAPTER IV

# ALL-CLOCK-FREQUENCY ERROR-ESTIMATION

In traditional design, the designer normally focuses on the task of reducing propagation delay of the static critical paths in order to improve the operating speed of the circuit. The timing errors are observed at the PO when: (1) the PO is activated by an input vector during that cycle, and (2) the settling time is longer than the current operating clock frequency. The PO corresponding to the static critical path may not always lead to the largest error-contributor. The identification of the real error-contributors will help to reduce errors more effectively. However, no existing commercial EDA tool directly provided internal activity analysis coupled with error estimation information. In this chapter, the detailed methodology of the all-clock-frequency error-estimation is described, and error estimation results are discussed.

#### Obtaining Outputs Settling Behavior