# ANALYSIS OF PARAMETER VARIATION IMPACT ON THE SINGLE EVENT RESPONSE IN SUB-100 NM CMOS STORAGE CELLS

By

Amy V. Kauppila

Dissertation

Submitted to the Faculty of the Graduate School of Vanderbilt University in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

in

Electrical Engineering

May, 2012

Nashville, Tennessee

# Approved:

Professor Bharat L. Bhuva

Professor Ronald D. Schrimpf

Professor Lloyd W. Massengill

Professor W. Timothy Holman

Dr. Shi-Jie Wen

Copyright © 2012 by Amy V. Kauppila All Rights Reserved

#### ACKNOWLEDGMENTS

The execution of the body of research this document represents would not have been possible without the advice, instruction, and encouragement of many individuals. Thanks are due to my advisor, Dr. Bharat Bhuva, for his guidance and recommendations during the accomplishment of the research. His encouragement to pursue the doctoral degree is particularly appreciated. Appreciation is owed also to Dr. Tim Holman, Dr. Lloyd Massengill, Dr. Ron Schrimpf, and Dr. Shi-Jie Wen. Their advice, insights, and recommendations during the entirety of the research have been very valuable. I am grateful to the members of the dissertation committee for their input and review of papers and my dissertation.

Thanks are owed to Cisco Systems, Inc., the Defense Threat Reduction Agency, and the National Science Foundation for their financial support of this work.

The continued encouragement and support from my family has provided me with the opportunity to pursue this goal. I am grateful for their wisdom and their generous efforts to enable me to maintain a work-life balance. The understanding and grace shown by my daughters, Audrey and Abigail, have been bolsters during this process. The character and succor demonstrated by my husband, Jeff, has been a constant source of strength. Few people have been so blessed with their family and I am extremely grateful.

"Now to Him who is able to do immeasurably more than all we ask or imagine, according to His power that is at work within us, to Him be glory in the church and in Christ Jesus throughout all generations, for ever and ever! Amen." Ephesians 3:20-21

# TABLE OF CONTENTS

|           |                                                                                                               | Page    |

|-----------|---------------------------------------------------------------------------------------------------------------|---------|

| ACKN(     | OWLEDGMENTS                                                                                                   | iii     |

| LIST O    | F TABLES                                                                                                      | V       |

| LIST O    | F FIGURES                                                                                                     | vi      |

| LIST O    | F ABBREVIATIONS                                                                                               | xii     |

| Chapter   |                                                                                                               |         |

| I.<br>II. | INTRODUCTIONTRANSISTOR PARAMETER VARIATION AND SINGLE                                                         |         |

|           | Process Variation                                                                                             | 4<br>11 |

| III.      | Impact of Process Variation on Single Event Response IMPACT OF PROCESS VARIATIONS ON SRAM SINGLE EVENT UPSETS | 20      |

|           | SRAM Analysis Approach SRAM Analysis SRAM Intradie Analysis                                                   | 34      |

| IV.       | IMPACT OF PROCESS VARIATIONS AND CHARGE-SHARING ON THE SINGLE EVENT UPSET RESPONSE OF FLIP-FLOPS              | 48      |

| V.        | VERIFICATION OF THE PROCESS VARIATION IMPACT ON SINGLE EVENT UPSET                                            | 63      |

|           | Simulation Results Literature Survey                                                                          |         |

|           | Negative Bias Temperature Instability Literature Survey                                                       |         |

| VI.       | IMPACT OF PROCESS VARIATIONS ON UPSET REVERSAL                                                                |         |

|           | IN A 65 NM FLIP-FLOP<br>Upset Reversal Mechanism                                                              |         |

|           | Parametric Variation Impact on Upset Reversal                                                                 | 94      |

| VII.      | Error Source Analysis CONCLUSIONS                                                                             |         |

|           |                                                                                                               |         |

| REF       | FERENCES                                                                                                      | 110     |

# LIST OF TABLES

| Γable |                                                                                                         | Page |

|-------|---------------------------------------------------------------------------------------------------------|------|

| 1.    | The anticipated percentage of threshold voltage variability due to doping variabilities                 | 12   |

| 2.    | The critical charge values for the SRAMs with nominal parameter values for off-state NMOS and PMOS hits | 28   |

| 3.    | SRAM peak-to-peak upset probability variations                                                          | 40   |

| 4.    | Select Parameter Variations from Simulations on the 65 nm Flip-Flop B                                   | 43   |

| 5.    | The Correlation Coefficients of the Highest-Impacting Transistor Parameters                             | 69   |

| 6.    | Current and Future Work Roadmap                                                                         | 72   |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                       | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.     | Flash and DRAM ½ Pitch (nm) values by year 30                                                                                                                                         | 5    |

| 2.     | The figure shows data from multiple lithography processes as reported by different laboratories <sup>4</sup> . Line edge roughness does not scale with linewidth.                     | 8    |

| 3.     | The mean number of dopant atoms in the channel according to the technology node <sup>39</sup>                                                                                         | 9    |

| 4.     | Current (2005) and anticipated future threshold voltage distributions <sup>39</sup>                                                                                                   | 11   |

| 5.     | Development of photocurrent from initial ion strike to current / voltage transient <sup>27</sup>                                                                                      | 13   |

| 6.     | Soft error failure rate as a function of power supply voltage for multiple manufacturers and technologies <sup>85</sup>                                                               | 15   |

| 7.     | The probability density function of $Q_C$ values across a memory ${\rm array}^{113}$                                                                                                  | 18   |

| 8.     | Histogram of individual values of feedback resistors fabricated in the Sandia IIIA technology. The intended value for each feedback resistor was $400~\text{k}\Omega^{120}$           | 18   |

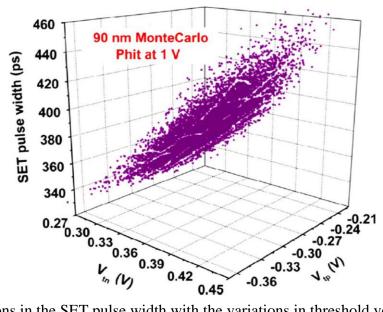

| 9.     | Variations in the SET pulse width with the variations in threshold voltage. Ten thousand Monte Carlo simulations were conducted on inverters in a 90 nm CMOS process <sup>107</sup>   | 20   |

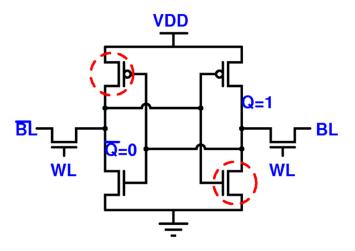

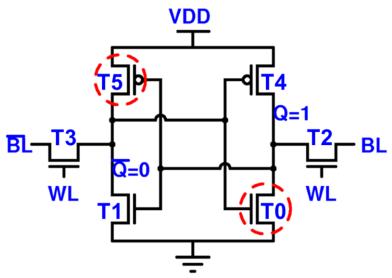

| 10.    | The 6T SRAM cell with the hit NMOS and PMOS transistors highlighted                                                                                                                   | 22   |

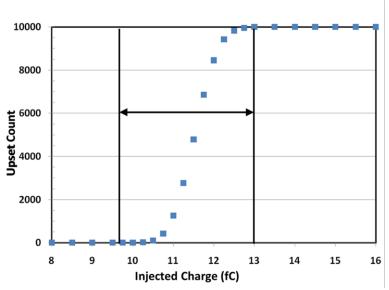

| 11.    | The number of SRAM upsets that occur at each charge value for an off-state PMOS hit on a 65 nm SRAM cell. The two vertical lines show the range of charge values used for simulations | 26   |

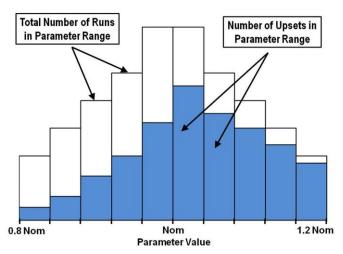

| 12.    | The total number of simulation runs and the number of simulation runs that resulted in an upset as assigned to a set of parameter-value segments                                      | 28   |

| 13.    | The upset rate of PMOS threshold voltage over its value segment range of the entire Monte-Carlo set of simulations                                                                    |      |

|     | at an injected charge value of 7.25 fC for an off-state NMOS hit on a 90 nm SRAM                                                                                                                                                                                                       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14. | The extracted upset probability binned by PMOS threshold voltage and injected charge values for an off-state NMOS hit on a 90 nm SRAM                                                                                                                                                  |

| 15. | The extracted upset probability over the PMOS V <sub>THO</sub> values and injected charge values for an off-state NMOS hit on a 90 nm SRAM. The blue lines represent the upset probability values that would occur if the threshold voltage variation did not impact upset probability |

| 16. | The differential upset probability is the difference between the parameter-value extracted upset probability and the charge-level upset probability                                                                                                                                    |

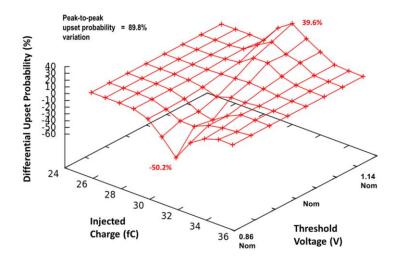

| 17. | The variation in upset probability for PMOS V <sub>THO</sub> (compared to the charge impact) on the SRAM upset rate over the range of charges for a 90 nm SRAM and an off-state NMOS hit. The peak-to-peak upset probability variation is shown                                        |

| 18. | The variation in upset probability over the range of PMOS V <sub>THO</sub> values and the nominal charge-level upset probability for a 90 nm SRAM and an off-state NMOS hit                                                                                                            |

| 19. | The extracted upset probability binned by PMOS V <sub>THO</sub> values and injected charge values for an off-state NMOS hit on a 65 nm SRAM                                                                                                                                            |

| 20. | The variation in upset probability for PMOS VTHO (compared to the charge impact) on the SRAM upset rate over the range of charges for a 65 nm SRAM and an off-state NMOS hit                                                                                                           |

| 21. | The impact of TOXE shifts on the relative rate of SRAM upsets for an off-state PMOS hit at 90 nm                                                                                                                                                                                       |

| 22. | The impact of TOXE shifts on the SRAM differential upset probability for an off-state PMOS hit at 90 nm                                                                                                                                                                                |

| 23. | The impact of TOXE shifts on the relative rate of SRAM upsets for an off-state PMOS hit at 65 nm                                                                                                                                                                                       |

| 24. | The variation in upset probability over the range of PMOS TOXE values and the nominal charge-level upset probability for a 90 nm SRAM and an off-state PMOS hit                                                                                                                        |

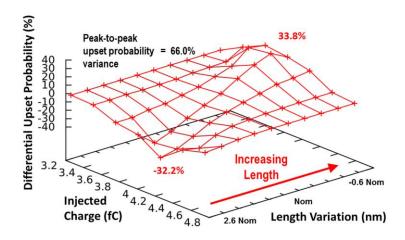

| 25. | The variation in differential upset probability of SRAM upsets for XL shifts for an off-state NMOS hit at 65 nm41                                                                                                                                                                      |

| 26. | 6T SRAM cell with labeled transistors                                                                                                                                                                                                          | 13 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 27. | Variation in upset probability for a single event hit on transistor T5 over the range of extracted threshold voltage values for transistor T1                                                                                                  | 14 |

| 28. | The variation in upset probability over the range of T1 $V_{THO}$ values and the nominal charge-level upset probability for a 65 nm SRAM and SE hit on T5                                                                                      | 14 |

| 29. | Variation in upset probability for a single event hit on transistor T5 over the range of extracted width variation values for transistor T1                                                                                                    | 45 |

| 30. | Variation in upset probability for a single event hit on transistor T0 over the range of extracted threshold voltage values for transistor T4                                                                                                  | 46 |

| 31. | Variation in upset probability for a single event hit on transistor T0 over the range of extracted width variation values for transistor T4                                                                                                    | 47 |

| 32. | The charge-level upset probabilities and the ranges of possible upset probability due to interdie threshold voltage variation. The single event strike was simulated on T0 and the upset response was correlated to the PMOS threshold voltage | 47 |

| 33. | The charge-level upset probabilities and the ranges of possible upset probability due to intradie threshold voltage variation.  The single event strike was simulated on T0 and the upset response was correlated to the T4 threshold voltage  | 48 |

| 34. | The percentage of simulations resulting in an upset for a strike to a transistor that causes upset through charge sharing in flip-flop B                                                                                                       | 52 |

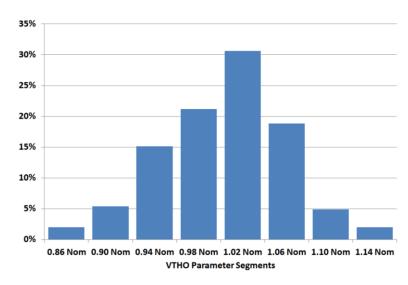

| 35. | The percentage of simulations with a threshold voltage value in each segment. The average value of each segment is shown as a fraction of the nominal VTHO value                                                                               | 54 |

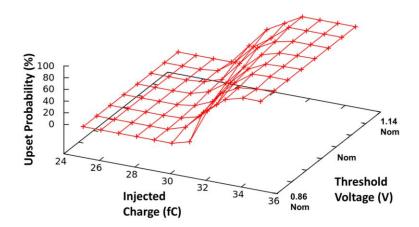

| 36. | The impact of threshold voltage variations on the parameter-value upset probability for a strike in flip-flop B                                                                                                                                | 54 |

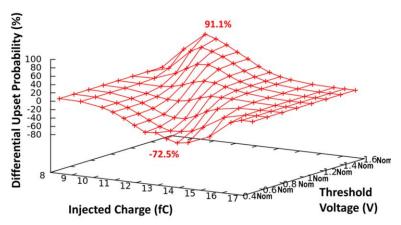

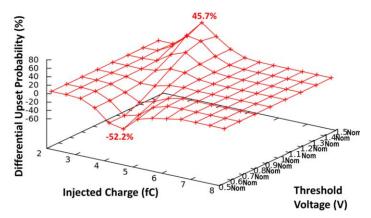

| 37. | The impact of threshold voltage variations on the differential upset probability for flip-flop B                                                                                                                                               | 55 |

| 38. | The impact of TOXE variations on the differential upset probability for flip-flop A                                                                                                                                                            | 56 |

| 39. | The impact of TOXE variations on the differential upset probability for flip-flop B                                                                                                                   | 7              |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 40. | The variation in upset probability over the range of PMOS TOXE values and the nominal charge-level upset probability for a flip-flop B                                                                | 7              |

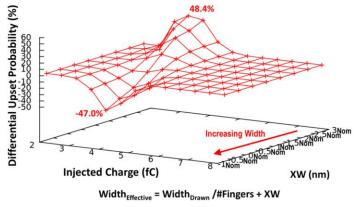

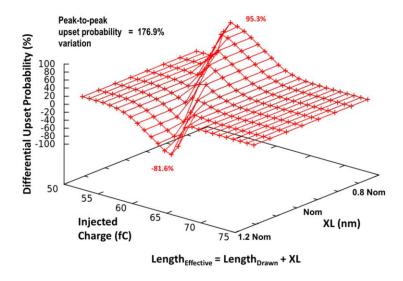

| 41. | The variation in upset probability for variations in NMOS XL for flip-flop A, a 45 nm flip-flop. The nominal value of XL is negative                                                                  | <b>5</b> 9     |

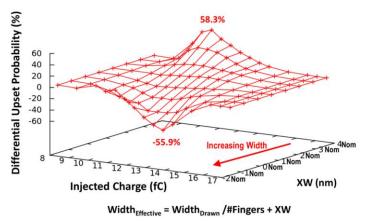

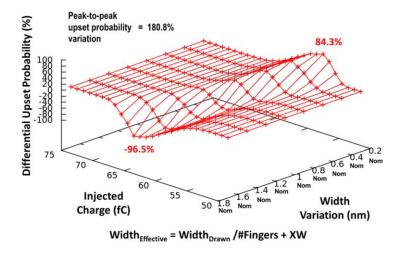

| 42. | The differential upset probability for variations in NMOS XW for flip-flop A, a 45 nm flip-flop5                                                                                                      | 9              |

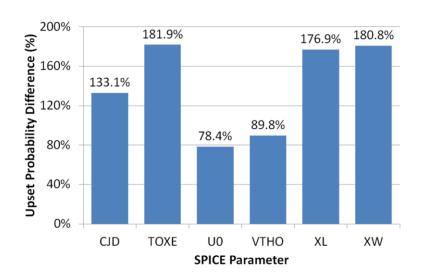

| 43. | Peak-to-peak upset-probability variation values for flip-flop A, a 45 nm flip-flop                                                                                                                    | <del>5</del> 0 |

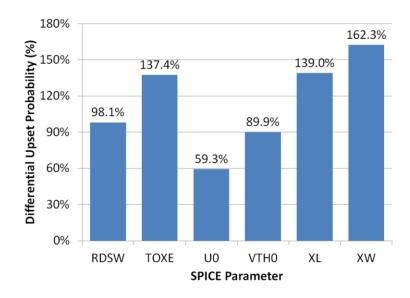

| 44. | Peak-to-peak upset-probability variation values for flip-flop B, a 65 nm flip-flop6                                                                                                                   | 51             |

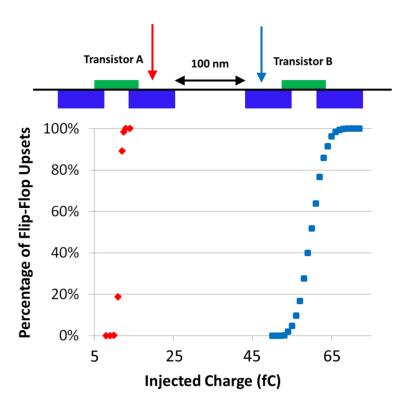

| 45. | The ranges of injected charge values for neighboring transistors in FF A. The charge range for a strike on Transistor A is 9fC to 13fC. The charge range for a strike on Transistor B is 52fC to 69fC | 53             |

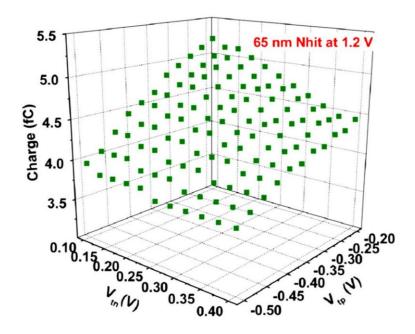

| 46. | The spread of critical charge values required for a bit flip in a 65 nm CMOS SRAM cell for an off-state NMOS transistor SE strike 107                                                                 | 55             |

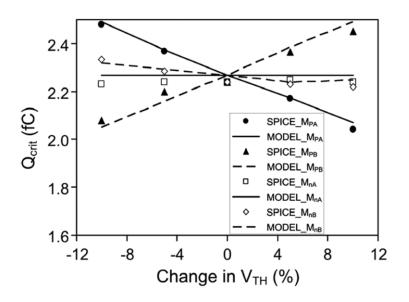

| 47. | Critical charge as a function of threshold voltages of the transistors in the cross-coupled inverters for the SRAM pictured in Fig. 43 <sup>125</sup>                                                 | 6              |

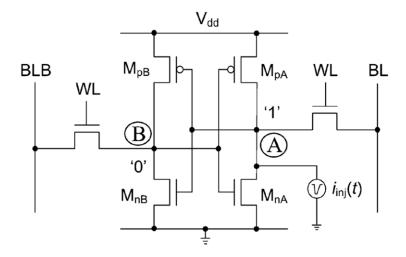

| 48. | SRAM with injected charge onto the drain of $M_{nA}$ .<br>The voltage value at Node A begins at '1' and the value at Node B begins at '0' $^{125}$                                                    | 57             |

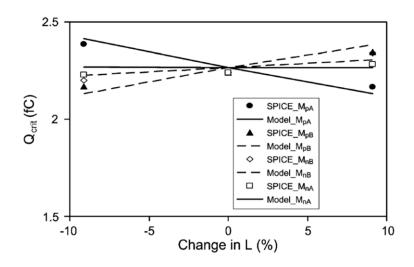

| 49. | SRAM critical charge as a function of the change in channel length 1256                                                                                                                               | 8              |

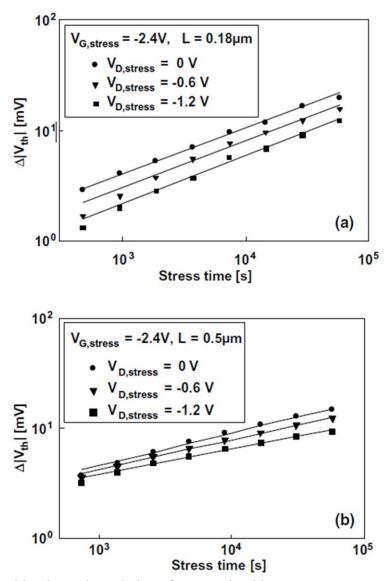

| 50. | Threshold voltage degradation after negative bias temperature stress. The W/L of the device geometries in a) is $10 \ \mu m/0.18 \mu m$ and $10 \mu m/0.5 \mu m$ in b) <sup>58</sup>                  | ′0             |

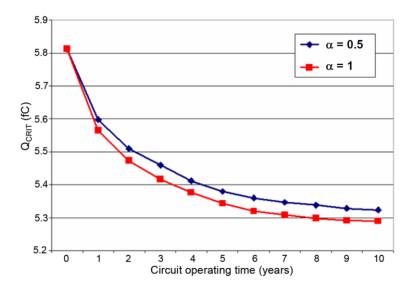

| 51. | Simulation results showing the SRAM critical charge as a function of the circuit operating time in years 129                                                                                          | '2             |

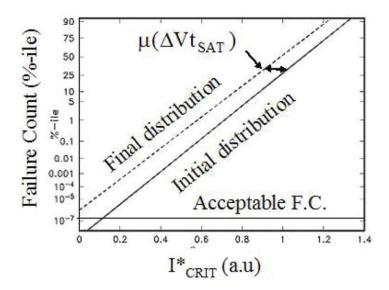

| 52. | Negative bias temperature instability induced increase in SRAM failure count as a function of I*CRIT 131                                                                                              | '3             |

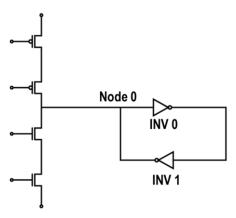

| 53. | A simplified schematic of the slave portion of the D-latch7                                                                                                                                           | '4             |

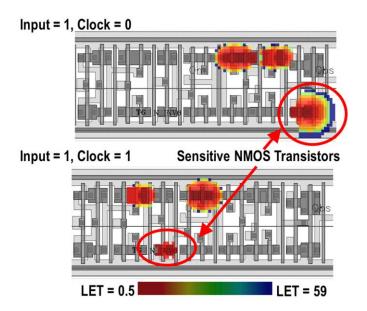

| 54. | Layout-aware simulation image highlighting the sensitive NMOS transistors 137                                                                                                                                              | 76 |

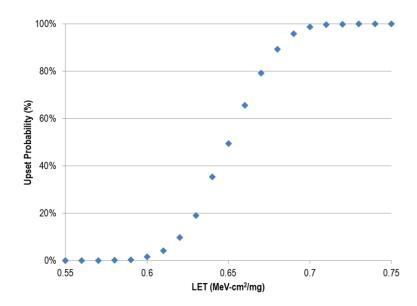

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

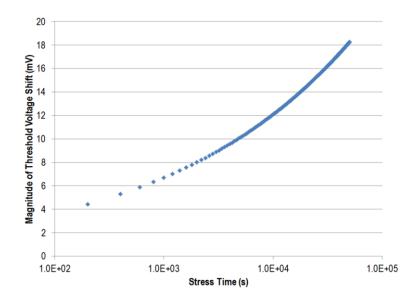

| 55. | Increase in flip-flop upset probability corresponding to the increase in the LET of a SE strike on the most sensitive NMOS transistor. The threshold voltage is nominal and the clock state is HIGH                        | 77 |

| 56. | NBTI-induced increase in the threshold voltage magnitude of PMOS transistors based on the stress-time <sup>148</sup>                                                                                                       | 78 |

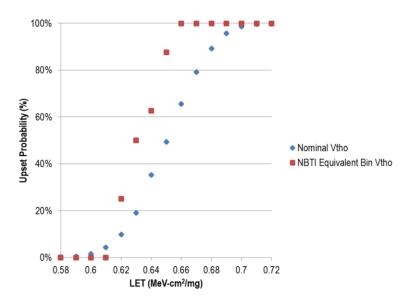

| 57. | Change in upset probability due to increase in threshold voltage magnitude due to NBTI                                                                                                                                     | 79 |

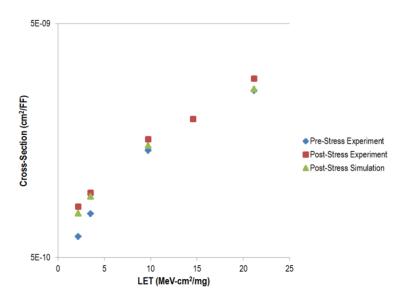

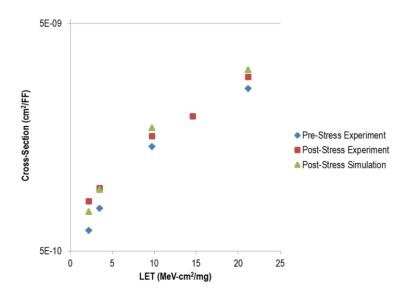

| 58. | Comparison of the pre-stress cross-section, the post-stress cross-section, and the process-variation simulation-based post-stress cross-section approximation                                                              | 31 |

| 59. | Comparison of the pre-stress cross-section, the post-stress cross-section, and the overall upset probability based estimation of the post-stress cross-section                                                             | 33 |

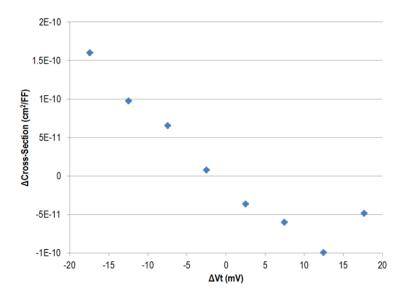

| 60. | Relationship between the change in threshold voltage and the resulting change in flip-flop cross-section for an incident ion LET of 3.49 MeV-cm <sup>2</sup> /mg                                                           | 34 |

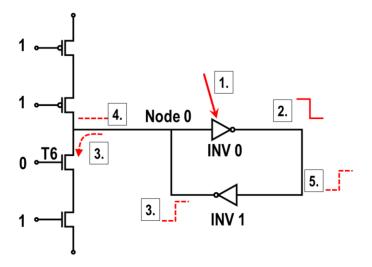

| 61. | A partial schematic of the master-slave flip-flop. It shows the progression of the upset-reversal mechanism                                                                                                                | 39 |

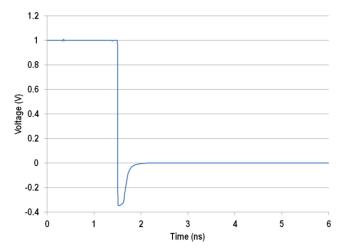

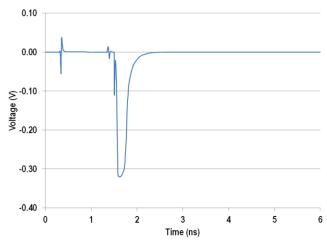

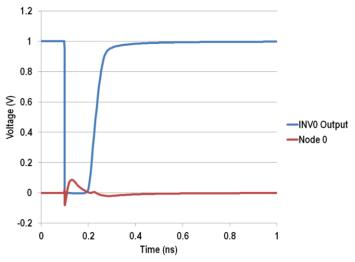

| 62. | The voltage signal at the output of inverter 0 (INV0) after a single event strike to the drain of the NMOS transistor in the inverter                                                                                      | 39 |

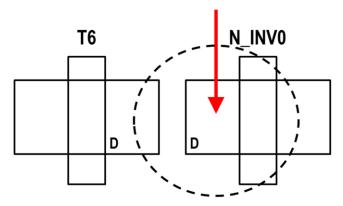

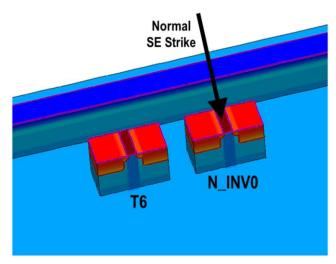

| 63. | An illustration of the sharing of charge between N_INV0 and T6 after a single-event hit                                                                                                                                    | 90 |

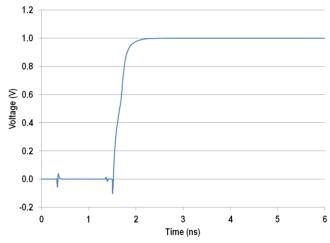

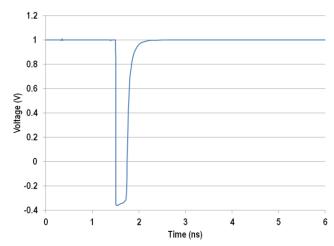

| 64. | The voltage signal at NODE 0 given that insufficient charge is collected by T6 in order to draw current through the transistor. The voltage signal changes from the correct value of LOW to the SE – induced value of HIGH | 90 |

| 65. | The voltage signal at NODE 0 given that sufficient charge is collected by T6. If so, charge collected by T6 prevents the SE–induced transient from changing the voltage at NODE 0                                          | 91 |

| 66. | The voltage signal at the output of INV0 if the reversal charge was reached. The signal changes                                                                                                                            |    |

|     | back to the correct value of HIGH. The change takes approximately 0.5ns9                                                                                                | 1  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 67. | The voltage signal at the output of INV0 if the reversal charge was reached. The signal changes back to the correct value of HIGH. The change takes approximately 0.5ns | 2  |

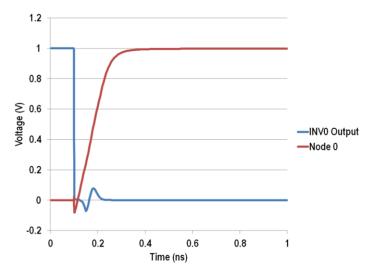

| 68. | The voltage signals at NODE 0 and the output of INV0 given that insufficient charge is collected by T6 in order to cause upset reversal                                 | 3  |

| 69. | The voltage signals at NODE 0 and the output of INV0 given that sufficient charge is collected by T6 in order to cause upset reversal                                   | 3  |

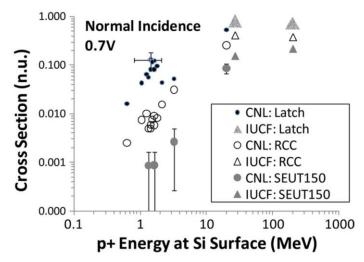

| 70. | The normalized cross-sections for multiple 32 nm devices 144                                                                                                            | 5  |

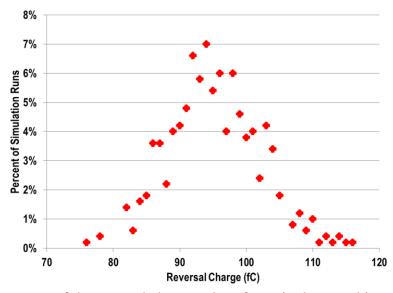

| 71. | The spectrum of the reversal charge values for a single event hit on the N_INV09                                                                                        | 7  |

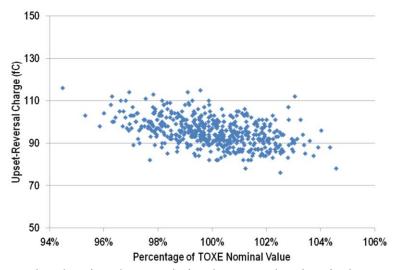

| 72. | A scatter plot showing the correlation between the electrical gate oxide thickness and the upset-reversal charge9                                                       | 8  |

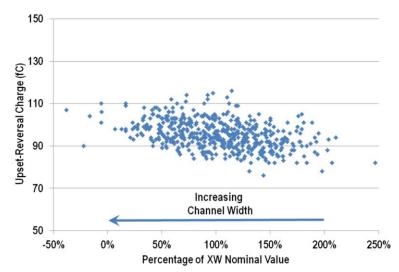

| 73. | A scatter plot showing the correlation between the channel width variation and the upset-reversal charge9                                                               | 9  |

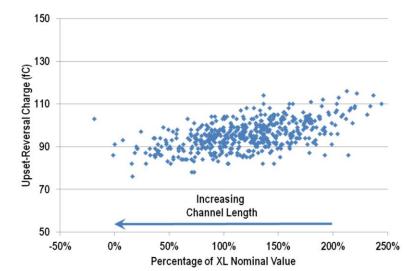

| 74. | A scatter plot showing the correlation between the channel length variation and the upset-reversal charge                                                               | 00 |

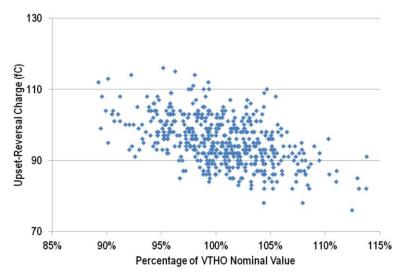

| 75. | A scatter plot showing the correlation between the threshold voltage and the upset-reversal charge                                                                      | 01 |

## LIST OF ABBREVIATIONS

β Charge Enhancement Factor

BTI Bias Temperature Instability

CGDL Drain-gate Overlap Capacitance

CGDO Drain-gate Overlap Capacitance per Unit Channel Width

CJ Junction Capacitance Density

CJSWG Gate-side Junction Capacitance

DICE Dual Interlocked Storage Cells

E<sub>CM</sub> Circuit Modeling Error

E<sub>S</sub> Monte-Carlo Sampling Error

E<sub>TM</sub> Manufacturer Modeling Error

E<sub>TOTAL</sub> Total RMS Error

HCI Hot-Carrier Injection

HVT High- $V_T$

IC Integrated Circuits

ITRS International Technology Roadmap for Semiconductors

LER Line Edge Roughness

LET Linear Energy Transfer

LSB Least Significant Bit

NBTI Negative Bias Temperature Instability

PDK Process Design Kit

PVTI Process, Voltage, Temperature, and Input

Q<sub>C</sub>, Q<sub>CRIT</sub> Critical Charge

RCC Reinforcing Charge Collection

RDF Random Dopant Fluctuations

RDSW Resistance per Unit Width

RMS Root-Mean-Square

SE Single Event

SEE Single Event Effects

SER Soft Error Rate

SET Single Event Transient

SEU Single Event Upset

SRAM Standard Random Access Memory

$SVT \hspace{1cm} Standard\text{-}V_T$

TDDB Time-Dependent Dielectric Breakdown

TOXE Electrical Gate Oxide Thickness

U0 Mobility

VLSI Very Large Scale Integration

VTHO, V<sub>THO</sub> Threshold Voltage

XL Length Variation due to Masking and Etching

XW Width Variation due to Masking and Etching

#### CHAPTER I

#### INTRODUCTION

Over the past few decades, the study of radiation effects has greatly impacted the field of electronics. The design, testing, and implementation of circuits, from the transistor level to the very large scale integration (VLSI) chip level, have been affected by some sub-facet of radiation effects. For example, the advent of circuit simulators, including PREDICT, ECAP, NET-1, CIRCUS, SPICE, and SCEPTRE, was directed, at least in part, by the need to model radiation effects in circuits [1], [2]. Studies show that with shrinking device sizes comes an increased impact of radiation effects, specifically single event radiation, on the performance of military, space, and commercial electronics [3]. The most important era for radiation effects may be in the days ahead.

The study of radiation effects possesses multiple facets. It primarily includes the analysis of total dose radiation, neutron-displacement damage, dose-rate radiation, and single event (SE) radiation. Each subset has different methods of analysis, metrics of error, and approaches to mitigation. All four areas are vital to provide an overall view of how radiation impacts electronic devices and to provide approaches for the amelioration of harmful radiation effects. This work centers on the impact of single event radiation.

In addition to the challenges presented by radiation, transistor and chip design also faces a challenge from the variations that are inherent to the manufacturing process. During chip fabrication, extreme measures are taken to ensure precision. However, variations in lithography, random dopant fluctuations, gate depletion, surface state charge, and line-edge roughness cause changes in individual transistor behavior and therefore, changes in the behavior-describing transistor parameters. The non-standard behavior then affects circuit performance and therefore impacts single event response. It is anticipated that the effects of process variations will substantially increase with shrinking device sizes. Thus, the potential impact of process variations on SE circuit response is significant. Parameter variations may also occur after the fabrication process. Circuit use, particularly in environments of high electrical, temperature, or mechanical stress, can cause device degradation. Device degradation can impact transistor parameter values and thus affect the functional performance and behavior of a circuit or system. This work analyzes the impact of process variations and device degradation on single-event upset (SEU) response of sub-100 nm CMOS memory storage circuits.

#### CHAPTER II

## TRANSISTOR PARAMETER VARIATION AND SINGLE EVENT OVERVIEW

Predictive ability in circuit design is at the core of the functionality of electronics. The response of a transistor ought to be determined based on the set of inputs. Loss of predictive ability disconnects the efforts of design and purpose from the actual performance of circuits. Both parameter variations and single events can affect the deterministic nature of devices. Parameter variations are caused by fabrication process variations and by device degradation over the lifetime of a circuit. Significant studies have been conducted analyzing the impact of parameter variations, from both sources, on device and chip function [4]-[18]. Also, analyses have been conducted studying the impact of single events on device and chip function. However, the simultaneous impact of both single events and parameter variations due to process variations and device degradations, specifically negative bias temperature instability, has had limited discussion in technological literature. Since the effects of single events and process variations are anticipated to increase with decreasing device sizes [3], [19]-[27], the analysis and discussion of the relationship between single events and parameter variation should be explored.

# **Process Variation**

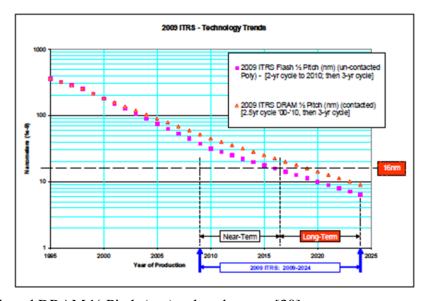

Since approximately 1959, the number of transistors that can be inexpensively placed on an integrated circuit has doubled approximately every two years, as predicted by Moore's Law [28-30]. One of the reasons for the increase in components is the decrease in device size. Figure 1 shows the DRAM ½ pitch size by year [30]. This decrease in device size has enabled significant increases in technology including increased memory capacity, faster switching times, processing speed, etc.

Fig. 1. Flash and DRAM ½ Pitch (nm) values by year [30].

The increasingly small transistor sizes have been enabled through advances in process technology. Improvements in process technology have stemmed from improvements in lithography, materials, patterning, and masks. As devices sizes

decrease, several changes are imposed upon circuits. These include smaller voltage rails, decreased storage node capacitance, and increased operating speeds [3]. Such changes accommodate the continuance of Moore's Law, but contribute to the sensitivity of a circuit to process variations.

The manufacturing processes that produce integrated circuits inherently, like all manufacturing, have process disturbances [26], [31]. Such disturbances result from fluctuations in oven temperature, equipment properties, and chemical properties of materials [26]. They cause process variations, which Duvall defines as "random fluctuations in process conditions and material properties leading to variations in the local or global characteristics of a product" [26]. For instance, chemical polishing results in variations due to non-uniform polishing. The changes in polishing speed result from a non-uniform layout density. The denser portions of the circuit slow the polishing. Thus, the denser portions of the chip are more highly polished than the less-dense portions. This effect can cause differences in the inner-layer dielectric thickness in the thousands of angstroms [25]. Another process disturbance results from lithography issues, which have increased with decreasing device size. The stepper causes a sizeable portion of the variations due to lithography. Stepper lens heating and improper lens focusing cause variabilities during exposure [25]. Additionally, the spin-on resist causes thickness variations, etching causes depth and line-width variations, and doping processes cause random dopant variations [25].

Variations in the manufacturing process may be modeled in multiple ways – using process parameter, physical parameters, model parameters (BSIM4) [32], and electrical/behavioral parameters [26]. When modeled as BSIM4 parameters, the process

variations show the resulting large shifts in the individual transistor parameters. For instance, as the polysilicon gate doping concentration decreases, the gate capacitance decreases [33]-[37]. The degradation is credited to the voltage drop across the gate due to the formation of a depletion layer near the polysilicon/silicon interface [33]. Another manufacturing variation is the variation in the surface-state charge density. Deviations in the charge density cause shifts in the threshold voltage [38]. Variations in channel length, along with variations in threshold voltage, cause increased variation in the standby current [6].

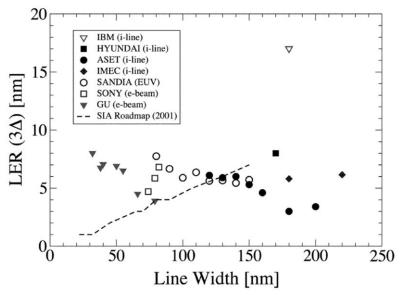

Line edge roughness (LER) results from limitations in the materials and tools used in lithography [4]. LER is becoming an issue of increasing concern since it does not scale with linewidth, as shown in Fig. 2 [4]. LER causes variations in the threshold voltage and may cause enhanced short-channel effects where the channel is shortened by LER [4].

Fig. 2. The figure shows data from multiple lithography processes as reported by different laboratories [4]. Line edge roughness does not scale with linewidth.

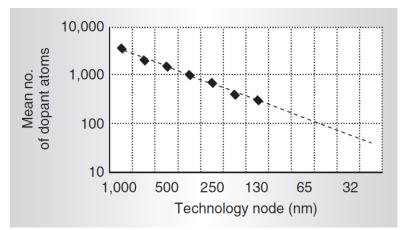

Variations in threshold voltage are also caused by random dopant fluctuations (RDF). Random dopant fluctuations result from the finite number of dopant atoms in the channel of a transistor [5], [39], [20]-[21], [40]-[46]. Channel regions are doped to control the threshold voltage of the transistor. Shrinking device sizes have decreased the number of atoms in the channel region so that in the 16 nm – 32 nm devices, the number of atoms in the channel region is in the tens. Fig. 3 shows the decrease in dopant atoms with decreasing device size [39]. The small numbers and discreteness of the atoms in the channel leads to variations in the electrical characteristics of the transistor. The inconsistent distribution of dopant atoms causes variations in the threshold voltage, which in turn affect drive current and transistor performance. One challenge with threshold voltage variations due to RDF is its impact on matching since the threshold voltage values can vary from transistor to transistor [46]. RDF has been discussed for decades in

the literature [44]-[45], [36]-[37] and is anticipated to increase in its impact on circuit performance. One of the earliest discussions of parameter variation and of RDF in the literature was written by William Shockley in 1961. He discussed the impact of the random distribution of dopant atoms on transistor voltages. Research has been conducted to examine the impact of various doping profiles, including undoped channel regions, on the effect of random dopant fluctuations [47]-[49].

Fig. 3. The mean number of dopant atoms in the channel according to the technology node [39].

Behavioral parameter variations are typically sorted into the categories of die-to-die (interdie) fluctuations and within-die (intradie) fluctuations. Die-to-die fluctuations are the consequence of factors like processing temperature, wafer polishing, and wafer placement [24], [50]. With interdie variations, the general assumption is that the variations do not vary within the die and that the variations equally affect each transistor in the circuit. Within-die variations are the consequence of factors like random dopant fluctuations and channel length variations across a single die [25]. Within-die variations

impact devices across the same die differently. This results in mismatch issues and potentially reduces functional yield [24], [26]. Historically, interdie fluctuations have been considered more significant than intradie variations since the intradie variations have been small in magnitude, compared to interdie variations, and could largely be managed with design techniques. However as device sizes have decreased, intradie variations have increased in magnitude so that they increasingly threaten circuit performance [26]. Both die-to-die and within-die parameter fluctuations are important to circuit performance [50], [51].

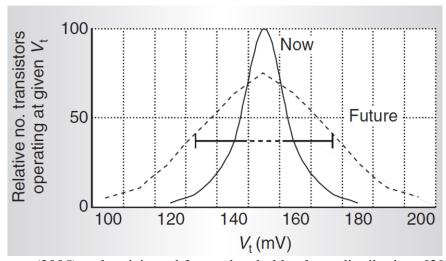

The effects of process variations have increased with decreasing device sizes and are anticipated to become a significant concern for circuit performance [39], [22]-[25]. Performance/power variability, device behavioral parameter variability, "uncontrollable threshold voltage variability" have been identified by the International Roadmap for Semiconductors as key design challenges [30]. Process variability has also been noted as a difficult challenge for reliability and scaling [30]. For example, table I shows the anticipated percentage of threshold voltage variability due to doping variabilities [52]. (The variability is shown as a peak-to-peak difference. For instance, an 81% variation can also be represented as +/- 40.5% from the nominal value.) A significant increase has been shown in the threshold voltage 4-sigma  $(4-\sigma)$  distribution as the gate oxide thickness is decreased from 150 Å to 30 Å. At 150 Å the 4- σ range is less than  $\pm$  2% [20]. A gate oxide thickness of 30 Å corresponds to a 4-  $\sigma$  range of almost +/- 25% [19]. Increased variability will flatten the distribution of threshold voltage as compared to the present distribution, as shown in Fig. 4 [39].

$TABLE\ I.$  The anticipated percentage of threshold voltage variability due to doping variabilities [52].

| Year of    | DRAM ½ Pitch (nm) | % V <sub>TH</sub> Variability (Doping   |

|------------|-------------------|-----------------------------------------|

| Production | Contacted         | Variability Impact on V <sub>TH</sub> ) |

| 2009       | 52                | 40%                                     |

| 2010       | 45                | 40%                                     |

| 2011       | 40                | 40%                                     |

| 2012       | 36                | 58%                                     |

| 2013       | 32                | 58%                                     |

| 2014       | 28                | 81%                                     |

| 2015       | 25                | 81%                                     |

| 2016       | 22.5              | 81%                                     |

| 2017       | 20                | 81%                                     |

| 2018       | 17.9              | 112%                                    |

| 2019       | 15.9              | 112%                                    |

| 2020       | 14.2              | 112%                                    |

| 2021       | 12.6              | 112%                                    |

| 2022       | 11.3              | 112%                                    |

| 2023       | 10.0              | 112%                                    |

| 2024       | 8.9               | 112%                                    |

Fig. 4. Current (2005) and anticipated future threshold voltage distributions [39].

The process- and transistor-parameter variations pose a serious challenge for circuit design at advanced technology nodes [43], [53]-[56]. Parameter variations, which model the deviations from nominal transistor behavior caused by process variations, have significant impact on drive current, current leakage, yield problems, timing issues, and power issues. For instance, Unsal reports that parameter-variation-induced gate-delay variability causes a significant portion of the minimum and maximum delay margins at 130nm [25]. Chip design teams must determine how to manage the process variations for both circuit performance and yield problems [24]. Changing design parameters can affect the impact of process variations [22]. Designers must consider variations due to process, voltage, temperature, and input (PVTI) values. The necessary safety margins are becoming an important facet of design [24], [25].

## Single Event Radiation Overview

Single event effects (SEE) encapsulates the study of the effect of single event radiation on electronic devices. Single event effects are related to the impact of energetic particles (such as protons, neutrons, alpha particles, or heavy ions) on microelectronic circuits. When an energetic particle strikes a device, some of the energy of the particle may generate electron-hole pairs [57]. Linear energy transfer (LET) is used to describe the amount of energy that is lost by the particle per unit of path length. LET can be correlated to the deposited charge through the guideline that a particle with an LET of approximately 100 MeV-cm²/mg deposited approximately 1 pC/μm [57]-[58]. As the

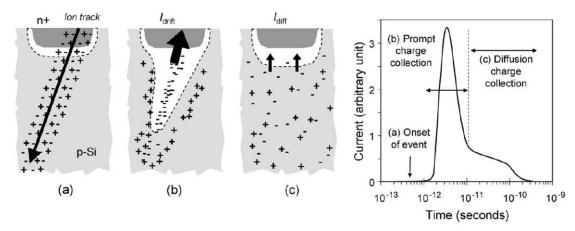

particle moves through the semiconducting material, electron-hole pairs are freed [57]-[58]. The electron-hole pairs serve as "new" mobile charge carriers. If the mobile carriers exist in or near a depletion region, the carriers are collected and they produce a photocurrent [59], [60]. The progression from ionized particle to current and voltage transient is shown in Fig. 5 [27].

Fig. 5. Development of photocurrent from initial ion strike to current / voltage transient [27].

The impact of the photocurrent depends on the LET of the energetic particle, strike location, circuit topology, and circuit state. An induced photocurrent creates a localized current transient and resulting voltage transient. Such transients are called single event transients (SET). SETs are expected to become the dominant contributor to soft error rates [61]. If a single event transient is latched so that it corrupts stored information, it leads to a single event upset.

Single events were initially predicted by Wallmark and Marcus in 1962 [62] and the anomalies in digital circuits on satellites were attributed to single events, based on experimental testing, in 1975 [63]. Significant works during the 1970's brought attention to the challenges caused by single events and helped spur the area's research [64]-[71]. Pickel and Blandford, in 1978, introduced a model for estimating the cosmic-ray-induced bit error rate and used it to sufficiently estimate the actual bit error rate of dynamic RAMs in an operating satellite system [66]. In 1979, an early report of single event upsets was made by Guenzer et al. during the description of irradiated DRAM circuits [68]. In the same year, single event latchup was first reported in the literature [70]. (Further discussion of the single event history can be found in [58], [72].)

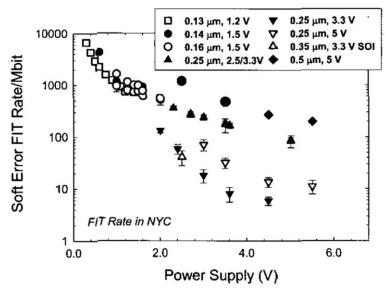

May and Woods reported terrestrial soft errors in 1979. Early terrestrial soft error issues were determined to be the result of alpha-particle emission from radioactive contaminants in chip packaging [65], [73]. Significant effort went into improved packaging material and shielding coatings to prevent terrestrial single event effects [73], [74]. Due to that work, terrestrial single events resulting from alpha particles were a non-issue for a number of years until shrinking device sizes reawakened the issue. However, terrestrial circuits showed sensitivity to upset from particles produced by cosmic rays, particularly neutrons. In 1993, dense SRAM cells were shown to be susceptible to neutron-induced upset at terrestrial levels [75]. Dodd et al. experimentally demonstrated the neutron-induced latchup in high density SRAM cells [76] as shown in Fig. 6. Additionally, neutrons were demonstrated to be the cause of SEUs in implantable cardiac defibrillators [77]. In 2000, it was reported that high-end servers made by Sun Microsystems were susceptible to terrestrial single event radiation [78]. Soft errors from

both alpha-particles and cosmic ray neutrons are a significant concern in terrestrial environments due to decreasing internal circuit capacitances and operating voltages [27], [76], [79]-[81]. In fact, terrestrial soft errors have been noted as a concern for terrestrial electronics below 16 nm in the International Technology Roadmap for Semiconductors (ITRS) [82].

Fig. 6. Soft error failure rate as a function of power supply voltage for multiple manufacturers and technologies [76].

Current deep sub-micron technologies are particularly susceptible to single events. The challenge derives from a conglomeration of effects that affect circuits' radiation response. For instance, decreasing device size has led to decreased storage charge and increased operating speeds [3]. Decreased storage charge contributes to single event sensitivity since the charge deposited by the ionized particle is now more on par

with the storage node charge. The increased operating speeds increase circuit sensitivity since they are now comparable to the speed of a single event transient. It has been postulated that single event transients in digital circuits may set limits on the operating speeds of rad-hard electronics [3]. Without including new mechanisms, scaling rules predict a 43% increase in sensitivity to soft errors per technology generation [83]. Single event upsets are currently the dominant failure mode of all reliability mechanisms (in qualified products) [84]. Not surprisingly, soft errors have been identified as one of the top technology challenges for reliability [30]. Since single events are expected to dominate other reliability concerns in deep sub-micrometer devices due to decreased transistor currents and nodal capacitances, it is vital to understand and quantify the impact of contributing mechanisms.

As technologies continue to scale, single event radiation has resulted in increasingly challenging failure mechanisms in integrated circuits (IC). New phenomena have begun to affect radiation response, including charge sharing [85]-[90], pulse quenching [91], [92], multiple-bit upset [86], [87], [93], [94], and process-parameter variation [95]-[99]. These phenomena add to the complexity of the circuit-level SE response. Charge sharing is a problem for advanced technologies due to decreased storage node charge and increased packing densities [85]-[87]. Charge-sharing occurs because of the diffusion of the carriers in the substrate/well [86] and results in charge collection at multiple nodes to a single incident ion [85]-[88]. It increases the susceptibility to SE radiation of many circuits [85]-[87], including some hardened circuits since more than one storage node can be affected at one time [85], [89]. Techniques used to harden circuits to charge-sharing effects include separating sensitive transistor pairs in

the layout and guard rings [86]. It has, though, been suggested that charge sharing may itself be exploited in specific cases to provide circuit hardening [100]-[102].

# Impact of Process Variation on Single Event Response

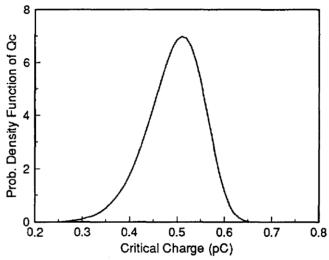

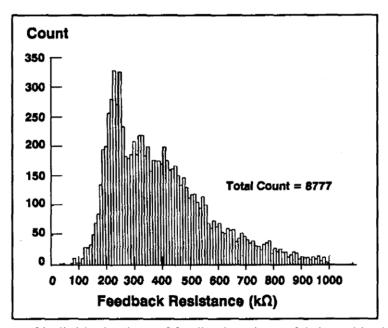

Variations in process parameters have been demonstrated to significantly affect the single-event response of circuits [95], [97]-[99], [103]-[108]. The impact of parameter variations on radiation response has been discussed, albeit not extensively, in the literature for decades. In 1989, Kohler and Koga discussed the impact that the feedback resistor value has on the minimum linear energy transfer required for upset in SRAMs [109]. A few years later, Massengill et al. discussed the spread of critical charge (Q<sub>C</sub>) values as shown by the probability density function in Fig. 7 [103]. It was determined that the spread was due to a variation in the charge enhancement factor (β) due to line width variations, doping variations, and non-uniform dislocation densities of the starting material, along with a distribution of strike locations [103]. Additional work in the 1990's further confirmed the influence of process variations on circuit parameters, as shown in Fig. 8 for feedback resistance [110], and consequently on the single event response of circuits [104], [105], [110], [111].

Fig. 7. The probability density function of Q<sub>C</sub> values across a memory array [103].

Fig. 8. Histogram of individual values of feedback resistors fabricated in the Sandia IIIA technology. The intended value for each feedback resistor was 400 k $\Omega$  [110].

As early as 1998, the impact of process variation on the radiation response of circuits was identified as a challenge in scaled devices [19]. Since that time, the significance of the impact of process variations on circuit performance has increased sizably. Recent work has analyzed the impact of process variation in advanced technologies and has shown that circuits in the sub-100 nm region have a significant SEU sensitivity to process parameter variations [95]-[100]. Balasubramanian examined the impact of the threshold voltage variation on inverter performance. Fig. 9 correlates SET pulse widths with both PMOS and NMOS threshold voltages [98]. A similar study shows the impact of PMOS and NMOS threshold voltages on the critical charge of 130 nm SRAM [99]. A spread in critical charge will significantly affect the overall SRAM cross-section and error rates. In order to accurately predict the single-event response of circuits as device sizes continue to scale, it is necessary to identify and quantify the impact of the specific process variations.

Fig. 9. Variations in the SET pulse width with the variations in threshold voltage. Ten thousand Monte Carlo simulations were conducted on inverters in a 90 nm CMOS process [98].

#### CHAPTER III

## IMPACT OF PROCESS VARIATIONS ON SRAM SINGLE EVENT UPSETS

The impact of process variations are increasing with technology scaling. The resulting transistor parameter variations present challenges for circuit design in the advanced technologies. Single event effects further complicate circuit design difficulties. The interaction between parameter variations and single event response can impact circuit performance. Earlier work acknowledged the impact of process parameter distributions on single event upset cross-section data [103], [104]. This work utilizes Monte-Carlo circuit simulation techniques to assess the impact of process variations.

## **SRAM Analysis Approach**

The impact of process variation on single event response was simulated to determine the impact of each varying parameter. An example study has been carried out on a six transistor (6T) SRAM cell targeted to commercially available 65 nm and 90 nm processes. SE hits were modeled to occur individually on the off-state NMOS and PMOS transistors in the SRAM cell, as shown in Fig. 10. SE currents were modeled using a bias-dependent single-event model that was calibrated to the 90 nm process using 3-D TCAD simulations [112]. The bias-dependent SE model was implemented in Verilog-A

and incorporated into the SPICE BSIM4 transistor model. The single-event models were integrated into the 90 nm process-design kit (PDK) and calibrated using known collection depths and the estimate that a charged particle with an LET of 1 MeV-cm $^2$ /mg deposits approximately 10 fC/ $\mu$ m of track length [57]. The bias-dependent SE model was adapted to work with the 65 nm process design kit (PDK) and the collection length was linearly scaled for the 65 nm technology.

Fig. 10. The 6T SRAM cell with the hit NMOS and PMOS transistors highlighted.

Simulations conducted on the SRAM cells accounted for different SE hit locations by varying the injected-charge value. Simulation studies were performed on each of the processes with the process-nominal supply voltages. In all cases, ten thousand simulations were conducted at several levels of injected charge. The Monte-Carlo simulations provided a representation of the statistical variations during chip manufacturing using the process variabilities included in the process design kits. No single parameter was varied individually since many of the parameters have

interdependencies; all parameters were varied together in accordance with the PDK. For example, channel width and length are related to the threshold voltage value. Also, the mobility is related to the oxide thickness and threshold voltage. A list of the varying parameters is shown in Tables II and III for 90 nm and 65 nm respectively. The parameter variation was accomplished globally (local mismatch was not included). The Monte-Carlo parameter space is the manufacturer's representation of the real-world process variations seen in fabrication. These process variabilities are reflected in shifts in the SPICE transistor parameters. While all model parameter shifts were included in the simulations, the analysis isolated the impact of each parameter. The total number of analyzed parameters was reduced by removing from analysis all parameters that were directly correlated with another parameter. The injected-charge value ranged from a level at which none of the ten thousand simulations resulted in an upset to a level at which all ten thousand simulations resulted in upsets. The charge values were incremented in 0.25 fC steps in between these levels for all other simulations.

TABLE II

VARYING PARAMETERS FOR THE 90 NM CMOS PROCESS

| Name   | Description                                                     | Type       |

|--------|-----------------------------------------------------------------|------------|

| cgdl   | Overlap capacitance between gate and lightly-doped drain region | Electrical |

|        | Non-LDD region drain-gate overlap capacitance per unit channel  |            |

| cgdo   | width                                                           | Electrical |

|        | Overlap capacitance between gate and lightly-doped source       |            |

| cgsl   | region                                                          | Electrical |

|        | Non-LDD region source-gate overlap capacitance per unit         |            |

| cgso   | channel width                                                   | Electrical |

| cj     | Zero-bias junction bottom capacitance density                   | Electrical |

| cjd    | Zero-bias bottom junction capacitance per unit area             | Electrical |

| cjs    | Zero-bias bottom junction capacitance per unit area             | Electrical |

| cjsw   | Zero-bias junction sidewall capacitance density                 | Electrical |

| cjswd  | Zero-bias junction sidewall capacitance density                 | Electrical |

| cjswg  | Zero-bias gate side junction capacitance density                | Electrical |

| cjswgd | Zero-bias gate side junction capacitance density                | Electrical |

| cjswgs | Zero-bias gate side junction capacitance density                | Electrical |

| cjsws  | Zero-bias junction sidewall capacitance density                 | Electrical |

| dlc    | Delta L for capacitance model                                   | Electrical |

| lint   | Lateral diffusion for one side                                  | Physical   |

| lu0    | U0 width sensitivity                                            | Electrical |

| noia   | Flicker noise parameter a                                       | Electrical |

| noib   | Flicker noise parameter b                                       | Electrical |

| noic   | Flicker noise parameter c                                       | Electrical |

| rdsw   | Zero-bias LDD resistance per unit width for RDSMOD=0            | Physical   |

| toxe   | Electrical gate oxide thickness                                 | Physical   |

| toxp   | Electrical gate oxide thickness                                 | Physical   |

| u0     | Low field surface mobility at 'tnom'                            | Electrical |

| vbox   | Oxide breakdown voltage                                         | Physical   |

| vtho   | Threshold voltage at zero body bias for long-channel devices    | Electrical |

| wu0    | U0 width sensitivity                                            | Electrical |

| xl     | Length variation due to masking and etching                     | Physical   |

| XW     | Width variation due to masking and etching                      | Physical   |

$\label{thm:cmos} Table\ III \\ Varying\ Parameters\ for\ the\ 65\ nm\ CMOS\ Process$

| Name   | Description                                                     | Type       |

|--------|-----------------------------------------------------------------|------------|

| cgdl   | Overlap capacitance between gate and lightly-doped drain region | Electrical |

|        | Non-LDD region drain-gate overlap capacitance per unit channel  |            |

| cgdo   | width                                                           | Electrical |

|        | Overlap capacitance between gate and lightly-doped source       |            |

| cgsl   | region                                                          | Electrical |

|        | Non-LDD region source-gate overlap capacitance per unit         |            |

| cgso   | channel width                                                   | Electrical |

| cj     | Zero-bias junction bottom capacitance density                   | Electrical |

| cjd    | Zero-bias bottom junction capacitance per unit area             | Electrical |

| cjs    | Zero-bias bottom junction capacitance per unit area             | Electrical |

| cjsw   | Zero-bias junction sidewall capacitance density                 | Electrical |

| cjswd  | Zero-bias junction sidewall capacitance density                 | Electrical |

| cjswg  | Zero-bias gate side junction capacitance density                | Electrical |

| cjswgd | Zero-bias gate side junction capacitance density                | Electrical |

| cjswgs | Zero-bias gate side junction capacitance density                | Electrical |

| cjsws  | Zero-bias junction sidewall capacitance density                 | Electrical |

| dlc    | Delta L for capacitance model                                   | Electrical |

| lint   | Lateral diffusion for one side                                  | Physical   |

| lu0    | U0 width sensitivity                                            | Electrical |

| noia   | Flicker noise parameter a                                       | Electrical |

| noib   | Flicker noise parameter b                                       | Electrical |

| noic   | Flicker noise parameter c                                       | Electrical |

| toxe   | Electrical gate oxide thickness                                 | Physical   |

| toxp   | Electrical gate oxide thickness                                 | Physical   |

| u0     | Low field surface mobility at 'tnom'                            | Electrical |

| vbox   | Oxide breakdown voltage                                         | Physical   |

| vtho   | Threshold voltage at zero body bias for long-channel devices    | Electrical |

| wu0    | U0 width sensitivity                                            | Electrical |

| xl     | Length variation due to masking and etching                     | Physical   |

| xw     | Width variation due to masking and etching                      | Physical   |

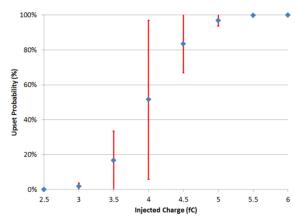

The process variations resulted in a spread of the number of SRAM upsets at each injected-charge value. Fig. 11 shows the number of Monte-Carlo simulations that resulted in an SRAM upset at each charge value for an off-state NMOS hit on a 90 nm SRAM. The slope of the curve within the two vertical lines, shown in Fig. 11, is representative of the effect of the process parameters. The vertical lines correspond to the smallest charge

that causes an upset and the largest charge that causes less than 10,000 upsets. For comparison purposes, the critical charge values for the 65 nm and 90 nm SRAMs with nominal parameter values for off-state NMOS and PMOS hits are shown in Table IV.

Fig. 11. The number of SRAM upsets that occur at each injected charge value for an off-state PMOS hit on a 65 nm SRAM cell. The two vertical lines show the range of charge values used for simulations.

TABLE IV

THE CRITICAL CHARGE VALUES FOR THE SRAMS WITH NOMINAL PARAMETER VALUES FOR OFF-STATE NMOS AND PMOS HITS.

|          | 65 nm     | 90 nm     |

|----------|-----------|-----------|

| PMOS hit | 11.548 fC | 20.103 fC |

| NMOS hit | 4.027 fC  | 7.091 fC  |

|          |           |           |

In order to determine the impact of the parameter values, the upset simulations were carried out over the expected range of injected-charge values for the SRAM cells. For each injected-charge value, 10,000 simulation runs were carried out by varying transistor parameters using foundry supplied Monte-Carlo models. For the simulation set, each parameter value range was divided into an equal number of segments. From parameter to parameter, the numerical values associated with each segment changed. However, the percentage of the variation stayed the same. For instance, the range of one bin of the threshold voltage covered approximately 4% of the nominal value and the range of the oxide thickness bin covered approximately 2%, but both bins covered 10% of the overall range of variation for both parameters. The number of segments should be loosely associated with the number of Monte Carlo simulations. If the number of simulations is low, the number of segments should be decreased to ensure an adequate number of simulations in each segment. A larger number of simulations would enable a larger number of bins. A larger bin count increases the accuracy of the analysis by enabling a more detailed expression of the SE response.

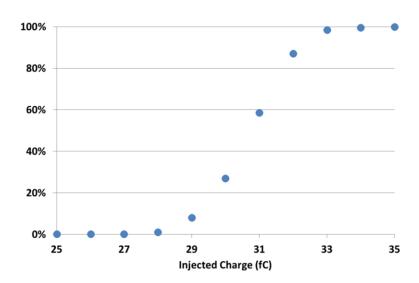

For this simulation set, the range of parameter values used was divided into ten segments. For each simulation, the parameter value was checked and assigned to one of these segments. Fig. 12 shows a cartoon illustration of the simulation parameter segments assignments. Each white column represents the total number of simulations runs for which the parameter value falls into the parameter segment. Each associated blue column, which is contained in the white columns, represents the number of those simulation runs that resulted in an SRAM upset. Thus, each simulation run had a specific injected-charge value and a specific segment of parameter-value assigned to it.

Fig. 12. The total number of simulation runs and the number of simulation runs that resulted in an upset as assigned to a set of parameter-value segments.

The simulation results were used to determine the SRAM upset probability over the range of possible parameter values for a given injected charge. For each parameter-value segment, the total number of simulations and the total number of simulations resulting in an upset were binned. This segregation enabled the comparison of the probability-of-upsets over the parameter-value range to the probability-of-upsets at the corresponding injected-charge level. The upset probability used in this paper is defined as the percentage of the total number of simulations that resulted in an upset out of all of the simulation runs (i.e., 5,000 upsets for 10,000 simulation runs will result in a 50% upset probability). (For this work, probability is based upon empirical data.) The charge-level upset probability is the percentage of the total simulations that result in an upset for a particular value of the injected charge. The parameter-value upset probability is the percentage of the simulations for each parameter-value segment that result in SRAM upsets.

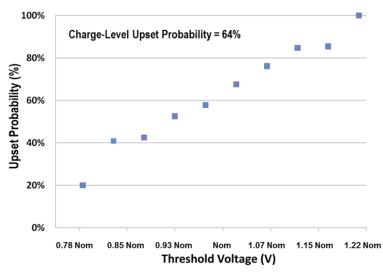

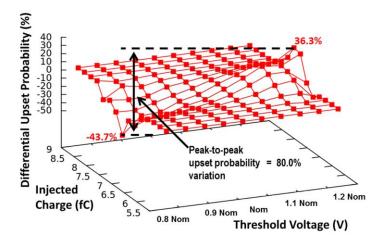

Fig. 13 depicts the upset probability of the PMOS threshold voltage SPICE parameter ( $V_{THO}$ ) over its value segments (bins) and lists the upset probability of the entire Monte-Carlo simulation set at the injected charge value of 7.25 fC for an off-state NMOS hit on a 90 nm SRAM. The parameter values for Fig. 13 and the following figures are normalized to the nominal parameter value, which is shown as Nom. The upset probabilities provide a quantitative description of the impact of each individual process parameter on the upset probability of an SRAM. For the example in Fig. 13, the value of the PMOS  $V_{THO}$  significantly affects the likelihood of an SRAM upset. For the largest magnitude of  $V_{THO}$ , the upset probability is approximately 36% greater than that for the overall charge upset probability, and for the smallest magnitude of  $V_{THO}$  it is almost 44% less with respect to the overall charge upset probability. An increase in threshold voltage magnitude will result in a decrease in transistor current. The decrease in transistor current will result in a lowering of critical charge as restoring current is decreased. This will result in an overall increase in upset probability as observed in these simulations.

Fig. 13. The upset rate of PMOS threshold voltage over its value segment range of the entire Monte-Carlo set of simulations at an injected charge value of 7.25 fC for an off-state NMOS hit on a 90 nm SRAM.

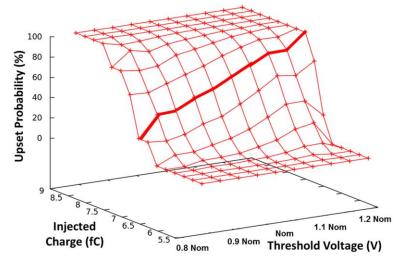

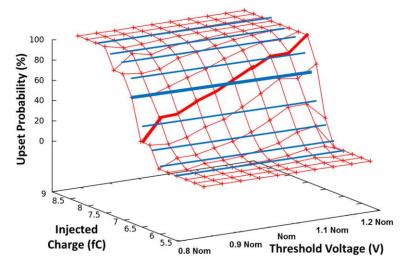

The upset probabilities over the PMOS threshold-voltage values and injected-charge values are shown in Fig. 14. A comparison of these upset probabilities to the charge-level upset probability, shown in Fig. 11, can elucidate the impact of the threshold voltage on the SRAM upset probability. The comparison of the parameter-value upset probability and the charge-level upset probability highlights the impact of the parameter on the upset probability. PMOS V<sub>THO</sub> has the most significant impact near the center of the range of injected-charge values. At the low end of injected-charge values, the charge level is too low to upset many of the SRAM cells regardless of the process parameter values. At the high end of injected-charge values, the charge level is high enough to upset most of the SRAM cells regardless of the process parameter values. In the middle of the charge range, the impact of the parameters is the most evident.

Fig. 14. The extracted upset probability binned by PMOS threshold voltage and injected charge values for an off-state NMOS hit on a 90 nm SRAM.

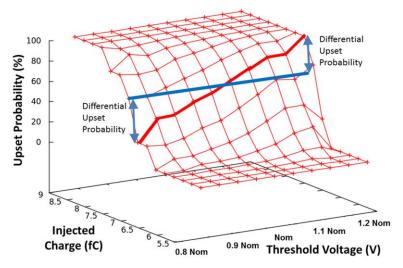

The impact of the process variations is shown in the increase in the upset probability for a given injected charge over the range of the threshold voltage, as highlighted in Fig. 14. Fig. 15 overlays, onto the plot from Fig. 14, the upset probability values that would occur if the threshold voltage variation did not impact upset probability. Those values correspond to the charge-level upset values. The difference between the parameter-value extracted upset probability and the charge-level upset probability, the differential upset probability as shown in Fig. 16, isolates the impact of the individual parameter. The differential upset probability is calculated by subtracting the charge-value upset probability from the parameter-value upset probability. The differential upset probability is important because it allows the measurement of the peak-to-peak upset probability variation. The peak-to-peak upset-probability variation is the delta between the two differential upset probability extremes, which can serve as types of radiation corners for process variation. The peak-to-peak upset-probability variation

shows the maximum variation in single event response due to the variation in process parameters. Radiation "corners" that bound the impact of process variations provide quantitative information for evaluation of the effects of parameter variation. They also afford an approach for the comparison of the impacts of multiple parameters.

Fig. 15. The extracted upset probability over the PMOS  $V_{THO}$  values and injected charge values for an off-state NMOS hit on a 90 nm SRAM. The blue lines represent the upset probability values that would occur if the threshold voltage variation did not impact upset probability.

Fig. 16. The differential upset probability is the difference between the parameter-value extracted upset probability and the charge-level upset probability.

Fig. 17 shows the difference between the PMOS V<sub>THO</sub> upset probability and the charge-level upset probability for an NMOS hit on a 90 nm CMOS SRAM. It also highlights the peak-to-peak upset probability variation. The middle portion of the charge range shows that a smaller threshold voltage magnitude results in a lower likelihood of an SRAM upset and that a larger threshold voltage magnitude results in a greater likelihood of an SRAM upset. The main reason for this effect is the decreased critical-charge requirements for SRAMs. For any given SRAM cell (or any storage cell), an upset occurs when the SET pulse-width generated by an ion hit exceeds the feedback delay of the SRAM cell. When the magnitude of the PMOS transistor threshold voltage is higher, the current provided by the transistor is lower. As the PMOS transistor for N-hits act as the restoring transistor, lower current results in longer SET pulse-widths and higher likelihood of an upset. Similarly, for lower threshold-voltage-magnitude transistors higher restoring current results in shorter SET pulse-width and subsequently lower

probability for an upset.

Fig. 17. The variation in upset probability for PMOS  $V_{THO}$  (compared to the charge impact) on the SRAM upset rate over the range of charges for a 90 nm SRAM and an off-state NMOS hit. The peak-to-peak upset probability variation is shown.

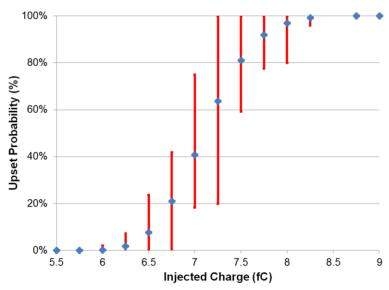

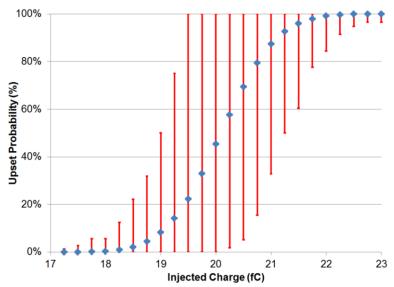

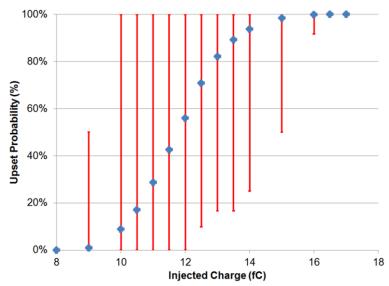

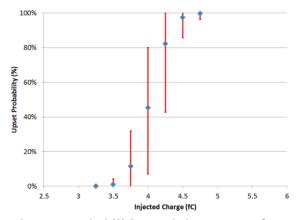

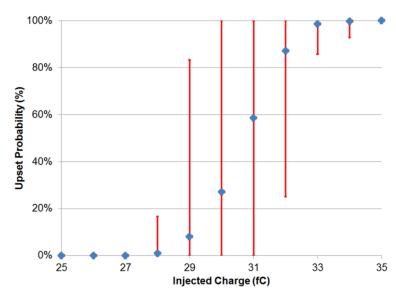

The differential upset probability can be used to show the potential range in upset probabilities due to process variation. Fig. 18 displays the charge-level upset probability values, in blue diamonds, and the range of upset probabilities over the range of threshold voltage variation at each injected charge value, in red lines. The red lines show the extent of the potential upset probabilities due to process variation.

Fig. 18. The variation in upset probability over the range of PMOS  $V_{THO}$  values and the nominal charge-level upset probability for a 90 nm SRAM and an off-state NMOS hit.

## **SRAM Analysis**

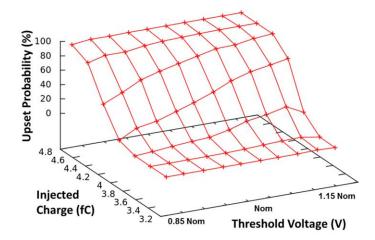

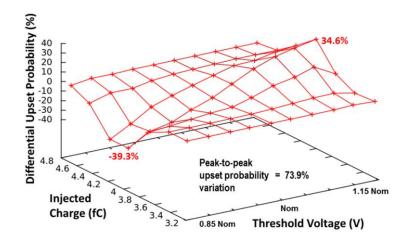

The examination of the parameter related SRAM upsets illustrates the significance that process variations can have on single event circuit response. The parameter analysis was conducted on all varying parameters. Some of the most significant results are presented here. The upset probability over the range of possible PMOS threshold voltages and over the series of charge values is shown in Fig. 19 for an off-state NMOS hit for a 65 nm SRAM. The variation in upset probability for shifts in PMOS V<sub>THO</sub> is shown in Fig. 20. The trend at 65 nm is the same as for 90 nm; the greater magnitude threshold voltages result in an increased likelihood of SRAM upset and the lesser magnitude threshold voltages result in a decreased likelihood of SRAM upset.

Fig. 19. The extracted upset probability binned by PMOS  $V_{THO}$  values and injected charge values for an off-state NMOS hit on a 65 nm SRAM.

Fig. 20. The variation in upset probability for PMOS VTHO (compared to the charge impact) on the SRAM upset rate over the range of charges for a 65 nm SRAM and an off-state NMOS hit.

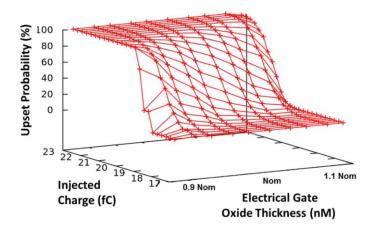

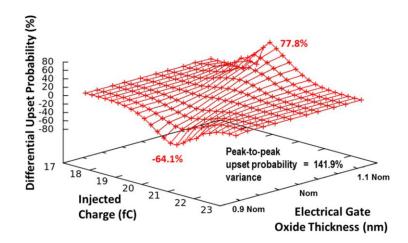

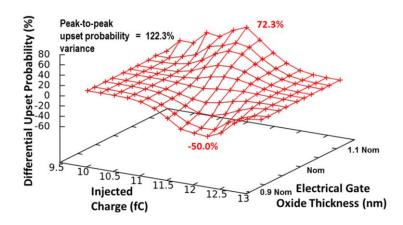

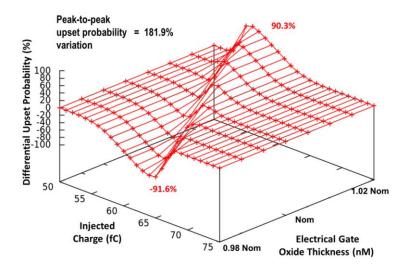

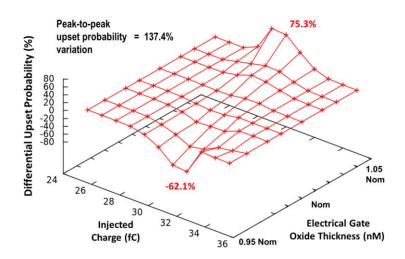

Several process parameter variations impact the SRAM upset probability. For instance, variations in oxide thickness can be discerned by examining TOXE, the electrical gate oxide thickness used in device modeling. Changes in TOXE will affect the threshold voltage, mobility, substrate current, gate-tunneling current, and the capacitance of the circuit node. As TOXE increases, the drain current decreases resulting in subsequent increases in the upset probability. Correspondingly, a decrease in TOXE would increase the drain current and decrease the probability of upsets. Additionally, increases in TOXE would also decrease the storage-node capacitance values and would increase the probability of SRAM upset. Fig. 21 shows the extracted upset probability binned by TOXE. The variation in upset probability for TOXE shifts on the difference probability of SRAM upsets is shown in Fig. 22 for an off-state PMOS hit at 90 nm. (The charge axes on Figs. 21 and 22 are reversed in order to improve the clarity of the graphs.) The corresponding variation in upset probability for a 65 nm SRAM is shown in Fig. 23. At 90 nm, the largest values for TOXE result in large increases, of up to 77.8%, in the likelihood of an SRAM upset. The smallest values of TOXE sizably reduce the relative likelihood of an SRAM upset. At 65 nm, the largest values for the gate oxide thickness result in a 72% increase in the likelihood of an SRAM upset for an injected charge of 11.25 fC. Additionally, the smallest values for TOXE show a decreased likelihood for SRAM upset. For an off-state PMOS SE hit for the 90 nm SRAM cell, fig. 24 shows the range of possible upset probabilities due to variations in TOXE and the nominal chargelevel upset probabilities. The graph indicates that changes in the process affecting TOXE will have a large impact on the SEU error probability.

Fig. 21. The impact of TOXE shifts on the rate of SRAM upsets for an off-state PMOS hit at 90 nm.

Fig. 22. The impact of TOXE shifts on the SRAM differential upset probability for an off-state PMOS hit at 90 nm.

Fig. 23. The impact of TOXE shifts on the relative rate of SRAM upsets for an off-state PMOS hit at 65 nm.

Fig. 24. The variation in upset probability over the range of PMOS TOXE values and the nominal charge-level upset probability for a 90 nm SRAM and an off-state PMOS hit.

Another common process concern is the issue of over-and under-etching. The SPICE parameter XL, length variation due to masking and etching, is affected by variants in etching. Length variation shifts can impact the effective channel length, the intrinsic

capacitances, and the transit time. Increases in XL increase the effective channel length and therefore decrease the drain current. The impact of the length variations on the variation in SRAM upset probability is shown in Fig. 25 for an off-state NMOS hit in 65 nm. (The nominal value of XL is negative.) As shown for TOXE, the shifts in XL have a notable impact on the SRAM upset probability. At 65 nm, the large XL values result in an increase in the relative likelihood of an SRAM upset. Also, the smaller XL values decrease the differential upset probability. The figures illuminate the impact that process variations have on the radiation response of the SRAM. A summary of the peak-to-peak upset probability variations for the SRAM is shown in Table V. Quantifying the impact of the SPICE parameter shifts provides the circuit designer with numerical information that can be applied to help increase the radiation hardness of a potential circuit. It can be used to anticipate the impact of process variations on a circuit's radiation response and can lead to the development of mitigation techniques. For instance, analysis could reveal a sensitivity of dual interlocked storage cells (DICE) to the variation of a specific set of parameters. DICE latches employ dual node feedback control and demonstrate single event upset immunity unless multiple nodes are upset due to a single particle impact [85], [89], [113]. Mitigation techniques could then be applied to harden the DICE cells.

Fig. 25. The variation in differential upset probability of SRAM upsets for XL shifts for an off-state NMOS hit at 65 nm.

$\label{eq:Table V} \textbf{SRAM} \ \textbf{PEAK-TO-PEAK} \ \textbf{UPSET} \ \textbf{PROBABILITY} \ \textbf{VARIATIONS}.$

|                | Peak-to-peak upset |                       |  |

|----------------|--------------------|-----------------------|--|

| Parameter Name | Process            | probability variation |  |

| VTHO           | 90 nm              | 80.0%                 |  |

| VTHO           | 65 nm              | 73.9%                 |  |

| TOXE           | 90 nm              | 141.9%                |  |

|                |                    |                       |  |

| TOXE           | 65 nm              | 122.3%                |  |

| XL             | 65 nm              | 66.0%                 |  |

## **SRAM Intradie Analysis**