# ANALYSIS AND HARDENING OF ALL-DIGITAL PHASE-LOCKED LOOPS (ADPLLS) TO SINGLE-EVENT RADIATION EFFECTS

By

Yanran (Paula) Chen

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

# DOCTOR OF PHILOSOPHY

in

Electrical Engineering

September 30, 2017

Nashville, Tennessee

Approved:

Lloyd W. Massengill, Ph.D.

Bharat L. Bhuva, Ph.D.

W. Timothy Holman, Ph.D.

Michael L. Alles, Ph.D.

T. Daniel Loveless, Ph.D.

Mark N. Ellingham, Ph.D.

## ACKNOWLEDGEMENTS

I would like to express my thanks and appreciation to all of my committee members for their guidance, encouragement and support throughout my entire PhD program. Dr. Massengill has been a great advisor and a role model to look up to. He has been providing me with extraordinary guidance and advice during my graduate years on research topics, career paths and life in general. He taught me in his own ways on how to become a good researcher and engineer. Dr. Bhuva has been always around for me to ask questions and discuss technical details with. Dr. Holman has been a great source of new ideas and new perspectives for looking at research problems. Dr. Alles' abundant knowledge on device physics and different technology nodes definitely brings fresh opinions into this work. Dr. Ellingham's strong background on Mathematics is a great source of inspiration for my work. His in-depth understanding of phase-locked loop (PLL) circuitries have been really useful when it comes to designing and debugging the circuit during electrical or radiation testing.

All the other professors in the RER group are on my list of people to pay appreciation to as well. They have contributed in various aspects to the completion of this work. To name a few: I would like to thank Dr. Schrimpf for his support and numerous motivating conversations. I thank Dr. Fleetwood for pushing me to become better at writing technical papers and better at doing research in general. I also would like to thank Dr. Zhang for her friendship and also for her help with packaging all my test parts, Dr. Kauppila for countless discussions on my research paths and Dr. Sternberg for his help with numerous times of TPA laser experiment conducted at Vanderbilt.

I thank the Defense Threat Reduction Agency (DTRA), the Institute of Space Defense Electronics (ISDE) and Vanderbilt School of Engineering for providing the funding for this work and allowing me to complete this dissertation. I would also like to pay thanks to my fellow colleagues in the Radiation Effects Research (RER) Group, including a lot of those that have graduated already. It has been a pleasure working with everyone. I have been receiving constant help from my friends in this group since the I visited the campus before I even got admitted. Without you all, I could not have adapted to the life in the States and completed the program so smoothly.

Most importantly, I would like to express my deepest appreciation to my husband and my parents for their never-ending support and encouragement. This PhD program brought my husband and I together. I am really grateful that we met, fell-in-love and got married with the best wishes from our advisors and all of our families and friends during the course of it. Thank you to my families for believing in me when I did not believe in myself. Their love have been my sources of confidence and strength through all the ups and downs of my graduate career.

# TABLE OF CONTENTS

| ACKI  | NOWLEDGEMENTS                                                                                                                                                                                                                                                                                                | iii                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| LIST  | OF TABLES                                                                                                                                                                                                                                                                                                    | viii                                                         |

| LIST  | OF FIGURES                                                                                                                                                                                                                                                                                                   | ix                                                           |

| Chapt | ter                                                                                                                                                                                                                                                                                                          |                                                              |

| I.    | INTRODUCTION                                                                                                                                                                                                                                                                                                 | 1                                                            |

|       | Objective of Research                                                                                                                                                                                                                                                                                        | $2 \\ 3$                                                     |

| II.   | ALL-DIGITAL PHASE-LOCKED LOOPS (ADPLLS)                                                                                                                                                                                                                                                                      | 5                                                            |

|       | Basic ADPLLs                                                                                                                                                                                                                                                                                                 | 8<br>8<br>14<br>22<br>26<br>28<br>29<br>29<br>30<br>32<br>33 |

| III.  | SINGLE-EVENT EFFECTS IN INTEGRATED CIRCUITS         Single-Event Mechanisms         Single-Event Transients (SETs) and Single-Event Upsets (SEUs)         Prior Work Related to SEEs in PLLs         Single-Event Characterization and RHBD Techniques for         CPPLLs         Modeling of SETs in CPPLLs | 36<br>36<br>39<br>40<br>41<br>44                             |

| IV.   | ADPLL MODULAR SINGLE-EVENT (SE) CHARACTERIZATION AND ANALYSIS                                                                                                                                                                                                                                                | 48                                                           |

|       | Error Signatures and Error Metric                                                                                                                                                                                                                                                                            | 49<br>51                                                     |

|       | SET Sensitivity Analysis of DCROs                                                                                                                                                                                                                                                                                                                            | 52<br>61<br>65<br>66<br>67<br>85<br>88               |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| V.    | OVERALL ADPLL SE CHARACTERIZATION AND ANALYSIS                                                                                                                                                                                                                                                                                                               | 90                                                   |

|       | SEU and SET Simulation Setup                                                                                                                                                                                                                                                                                                                                 | 90<br>91<br>96<br>100                                |

| VI.   | TIME-DOMAIN MODEL FOR SEUS IN ADPLLS                                                                                                                                                                                                                                                                                                                         | 101                                                  |

|       | System Modeling for ADPLLs       .         Modeling for SEUs in Different Sub-modules of ADPLLs       .         Model Verification       .         Frequency-based ADPLL       .         TDC ADPLL       .         Bang-bang ADPLL Model Verification       .         Implications for RHBD and Limitations of the Model       .         Conclusions       . | 102<br>107<br>110<br>111<br>113<br>115<br>118<br>119 |

| VII.  | RHBD DESIGN CONSIDERATIONS FOR ADPLLS                                                                                                                                                                                                                                                                                                                        | 121                                                  |

|       | Hardening Approach Against Harmonic Errors in DCROs<br>SEU Tolerant Hardening Approaches                                                                                                                                                                                                                                                                     | 121<br>124<br>127<br>131                             |

| VIII. | CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                  | 132                                                  |

| REFE  | ERENCES                                                                                                                                                                                                                                                                                                                                                      | 134                                                  |

| Appe  | ndix                                                                                                                                                                                                                                                                                                                                                         |                                                      |

| А.    | TECHNICAL ANACHRONISMS                                                                                                                                                                                                                                                                                                                                       | 148                                                  |

| В.    | VHDL/VERILOG SOURCE CODE                                                                                                                                                                                                                                                                                                                                     | 149                                                  |

|       | Phase Detectors                                                                                                                                                                                                                                                                                                                                              | 149<br>149<br>150<br>155<br>159                      |

|    | Digital Loop Filter                  |     |

|----|--------------------------------------|-----|

|    | FSM Controller                       |     |

| С. | TIME-DOMAIN MODEL MATLAB SOURCE CODE | 171 |

# LIST OF TABLES

| Table |                                                                         | Page |

|-------|-------------------------------------------------------------------------|------|

| 1     | Design specification comparisons between state-of-art ADPLLs and CPPLLs | 35   |

| 2     | Comparisons of ADPLL designs and maximum SET pulse widths (PWs)         |      |

|       | across technologies.                                                    | 63   |

| 3     | Design measurements for 1st-order and 2nd-order 7-bit linear and bang-  |      |

|       | bang ADPLLs at 713 Hz                                                   | 69   |

| 4     | DLF designs in four synthesized ADPLL topologies.                       | 75   |

| 5     | Design measurements for 1st and 2nd-order fraction-based linear AD-     |      |

|       | PLLs with different DCOs at 128 Hz                                      | 78   |

| 6     | FSM ADPLL design specifications.                                        | 97   |

| 7     | Operating mode of Boeing's ADPLL design under laser test                | 115  |

# LIST OF FIGURES

# Figure

| 1        | PLL usages in (a) modern SoCs and (b) clock and data recovery systems.       | 6   |

|----------|------------------------------------------------------------------------------|-----|

| 2<br>3   | Block diagrams for (a) ADPLLs and (b) A/MS PLLs                              | 7   |

| 3        | analog-digital converter (ADC) and digital-analog converter (DAC)            |     |

|          | wrappers.                                                                    | 8   |

| 4        | Output frequency of a typical ADPLL during initial acquisition time and      | 0   |

| 1        | steady-state operation.                                                      | 9   |

| 5        | Time detection is needed for ADPLLs to reach phase-lock and frequency        | 0   |

| -        | detection is needed for frequency-lock.                                      | 11  |

| 6        | Comparison of locking behaviors with and without the aid of locking          |     |

|          | process monitor $(LPM)$ [26]                                                 | 13  |

| 7        | Simulation results on loop locking characteristics for (a) a 1st-order bang- |     |

|          | bang ADPLL and (b) a 2nd-order frequency-linear ADPLL on IBM 180             |     |

|          | SOI technology.                                                              | 14  |

| 8        | Different digital implementation of bang-bang PDs [33]                       | 18  |

| 9        | A simplified structure of TDC core [34]                                      | 19  |

| 10       | PFD: (a) block diagram and (b) its transfer function [37]                    | 20  |

| 11       | A block diagram of an ADPLL using frequency-based PD (i.e. frequency         |     |

|          | comparator in the figure) and time-based PD (i.e. phase detector in the      |     |

|          | figure) [39]                                                                 | 21  |

| 12       | Time-to-digital converter serves as a "FSM-based PD" [5]                     | 22  |

| 13       | Block diagram of a typical (a) 1st-order ADPLL and (b) 2nd-order             | 2.4 |

| 14       | ADPLL with 2nd-order DLF.                                                    | 24  |

| 14       | Basic architectures of (a) an FIR filter [46] and (b) an IIR filter [47].    | 25  |

| 15       | Block diagram DLF consists of cascaded single-pole IIR filters and PI        | 00  |

| 10       | filters in an ADPLL [4].                                                     | 26  |

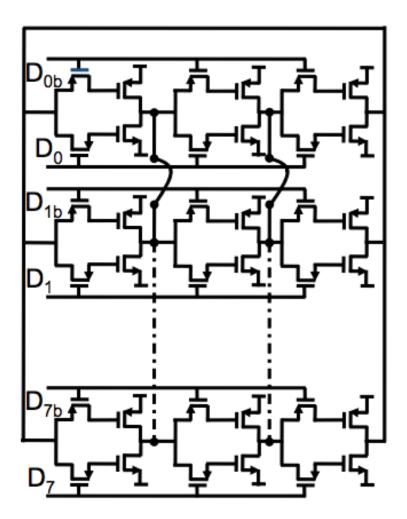

| 16       | Different DCO structures: (a) LC-tank based DCO [4] (b) Ring-based           | 97  |

| 17       | DCO [50]                                                                     | 27  |

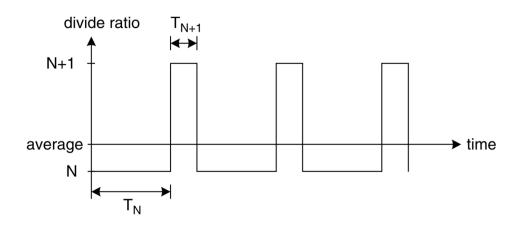

| 17<br>18 | Alternating division ratio of fractional-N PLL                               | 28  |

| 10       | [91]                                                                         | 37  |

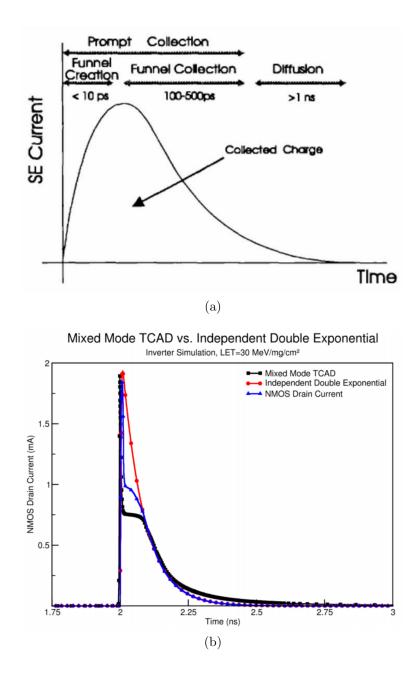

| 19       | (a) Typical shape of the SE current at a junction. The total collected       | 57  |

| 19       | charge corresponds to the area under the curve [90] and (b) Comparison       |     |

|          | of NMOSFET drain current in TCAD mixed-mode and SPICE simula-                |     |

|          | tion of an inverter, where the SPICE simulation used an independent          |     |

|          | current source to model the single-event pulse [92]                          | 38  |

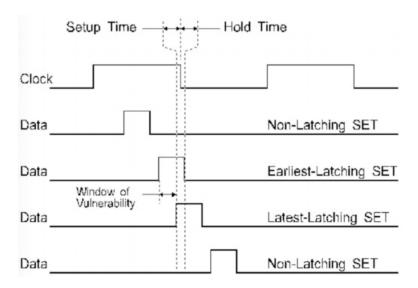

| 20       | An illustration showing how a pulse may or may not be latched by a           | 00  |

|          | storage [91]                                                                 | 40  |

|          |                                                                              | -   |

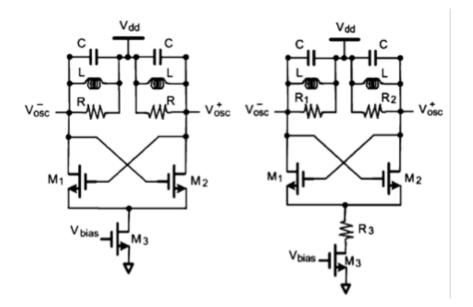

| 21              | Original LC-Tank VCO topology is shown on the left, while the right figure is the schematic of the RHBD VCO with a decoupling resistor R3 |                 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 22              | [109]                                                                                                                                     | 42              |

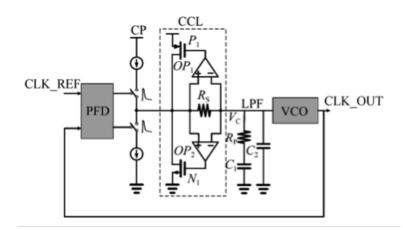

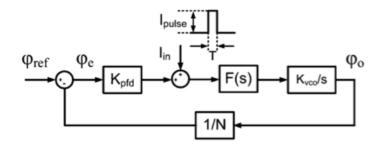

| 23              | (CCL)[110]                                                                                                                                | $\frac{43}{45}$ |

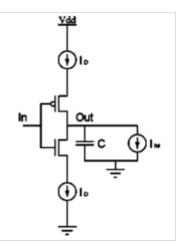

| 23<br>24        | A simple model for a SE hit in a current-starved inverter can be presented                                                                | 40              |

| 24              | by two current sources $(I_D)$ representing the restoring device current in a                                                             |                 |

|                 | current-starved inverter, an output node capacitance (C), and a current                                                                   |                 |

|                 | source representative of the current induced by the SE $(I_{hit})$ [106]                                                                  | 46              |

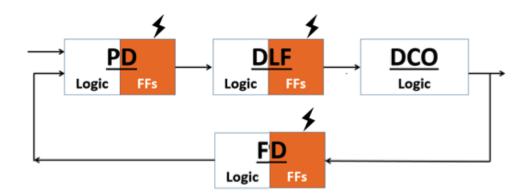

| 25              | SEU-sensitive modules and SET-sensitive modules in an ADPLL.                                                                              | 49              |

| $\frac{26}{26}$ | SEU signature transient waveforms in terms of ADPLL output frequency                                                                      | 10              |

| -0              | plotted over time[117].                                                                                                                   | 50              |

| 27              | Block diagram of the DCRO design implemented in a 40 nm bulk CMOS                                                                         |                 |

|                 | technology $[50]$ .                                                                                                                       | 53              |

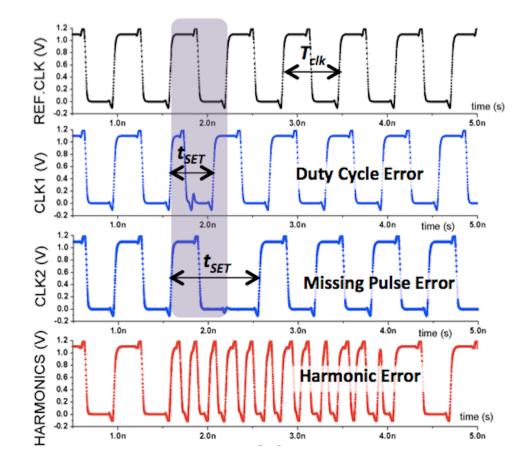

| 28              | SET-induced duty cycle error (second), missing pulse error (third) and                                                                    |                 |

|                 | harmonic errors (bottom) in reference to the unperturbed clock (top) $$ .                                                                 | 54              |

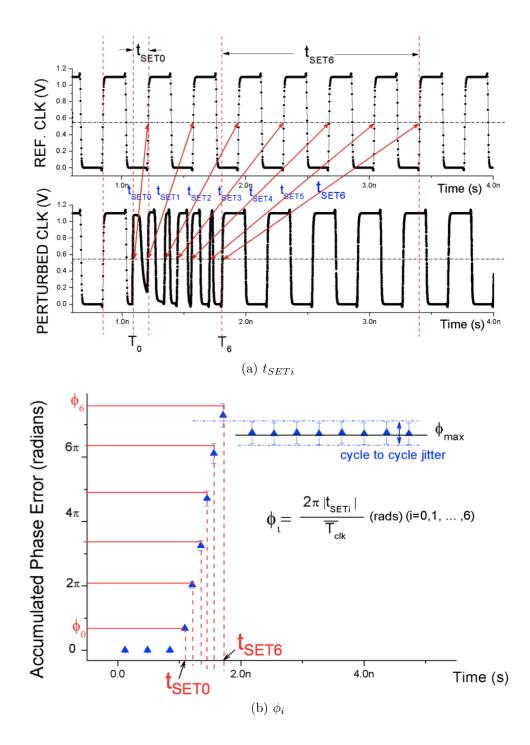

| 29              | The time differences $t_{SETi}$ between the rising edges of the perturbed and                                                             |                 |

|                 |                                                                                                                                           | 56              |

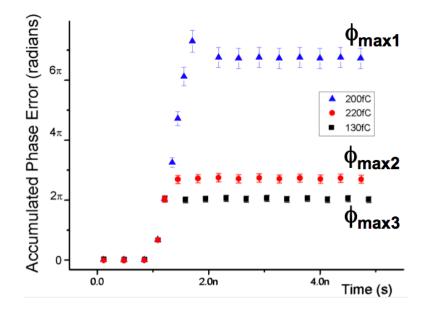

| 30              | The maximum accumulated phase error for different collected charge                                                                        |                 |

| 01              | values.                                                                                                                                   | 57              |

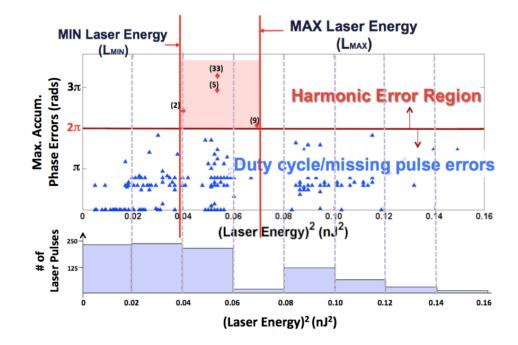

| 31              | Measured maximum accumulated phase error versus laser energy squared                                                                      | 50              |

| 32              | for the DCRO design operated at 0.9 V                                                                                                     | 58              |

| 32              | of DCO over clock period are plotted for both ADPLLs with integer-                                                                        |                 |

|                 | based linear PD and bang-bang PD                                                                                                          | 61              |

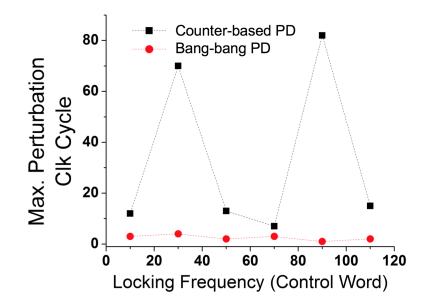

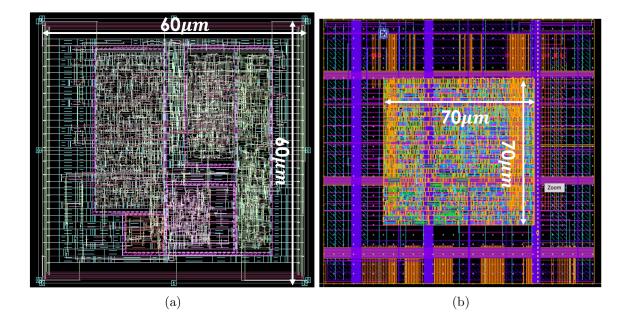

| 33              | Layout screenshots of the ADPLL design on (a) 32nm SOI technology                                                                         | 01              |

|                 |                                                                                                                                           | 62              |

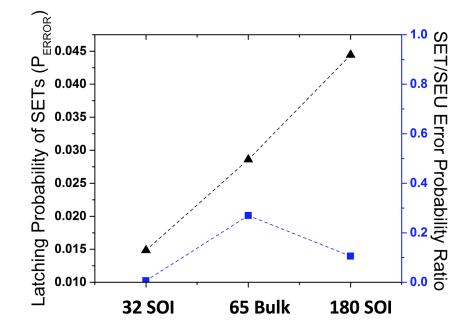

| 34              | The ratio of SET- and SEU-induced error probabilities for the ADPLL                                                                       |                 |

|                 | designs (blue) and the SET latching probability $(P_{ERROR})$ (black) across                                                              |                 |

|                 | technology nodes with logic masking probability $P_{mask}=0$ at reference                                                                 |                 |

|                 | clock frequency of 100 MHz.                                                                                                               | 65              |

| 35              | Block diagram illustration of conducted FPGA-based fault injection                                                                        |                 |

| 24              | experiment.                                                                                                                               | 66              |

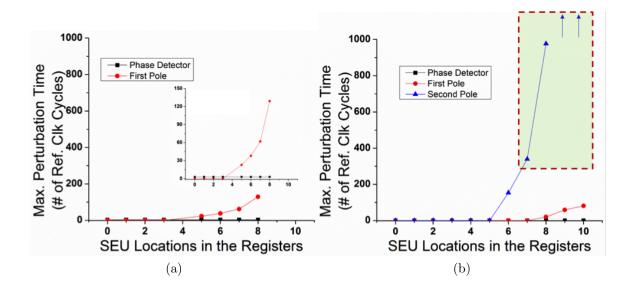

| 36              | FPGA fault injection results on SEU sensitivity of different registers                                                                    |                 |

|                 | in (a) 1st-order bang-bang ADPLL (the inset figure is the zoomed-<br>in version)and (b) 2nd-order bang-bang ADPLL at the same output      |                 |

|                 | frequency of 713 Hz.                                                                                                                      | 70              |

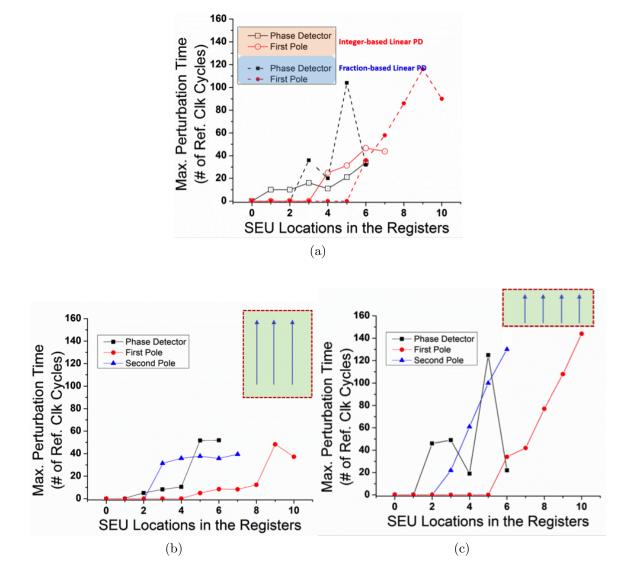

| 37              | FPGA fault injection results on SEU sensitivity of different registers in                                                                 | 10              |

| 0.              | (a) 1st-order ADPLL with fraction-based linear PD and integer-based                                                                       |                 |

|                 | linear PD, (b) 2nd-order ADPLL with integer-based linear PD and (c)                                                                       |                 |

|                 | 2nd-order linear ADPLL with fraction-based linear PD at the same                                                                          |                 |

|                 | output frequency of 713 Hz                                                                                                                | 71              |

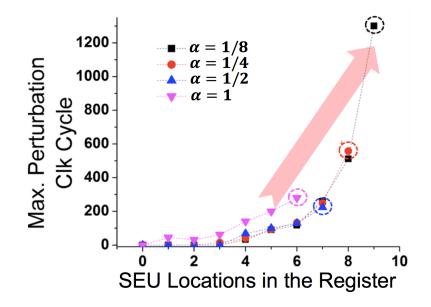

| 38              | FPGA fault injection results on DLF in a 1st-order ADPLL with different                                                                   |                 |

|                 | proportional gain ( $\alpha$ ).                                                                                                           | 73              |

|                 |                                                                                                                                           |                 |

| 39 | FPGA fault injection results on SEU sensitivity of PI filters of the DLFs                                                                                                                                                                                                                                                                                    |    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

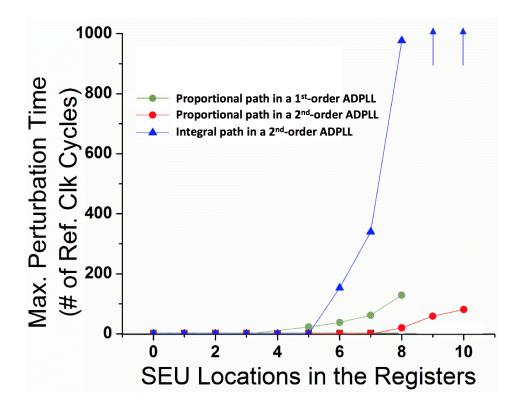

| 05 | in 1st-order and 2nd-order ADPLLs.                                                                                                                                                                                                                                                                                                                           | 74 |

| 40 | Worst-case ADPLL SEU response in terms of output frequency. The output signal(above) and reference clock signal (below) are plotted over the same period of time when SEUs occur in registers in FIR filters for two ADPLLs using a 2-tap and a 3-tap FIR filter respectively. Erroneous ADPLL output clock frequency errors are is observed only over a few |    |

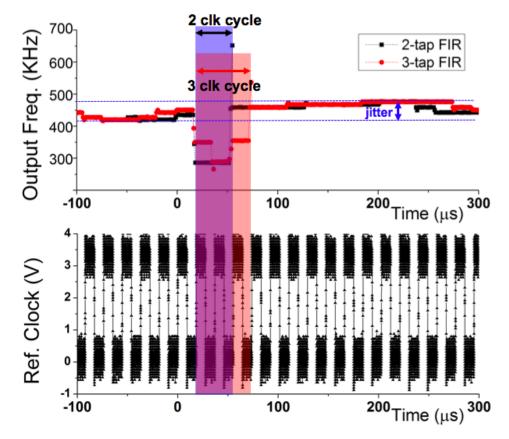

|    | reference clock cycles as shown in the colored boxes                                                                                                                                                                                                                                                                                                         | 76 |

| 41 | Maximum output perturbation time is plotted for SEUs occurring in<br>every bit location in the register corresponding to the three poles in the                                                                                                                                                                                                              |    |

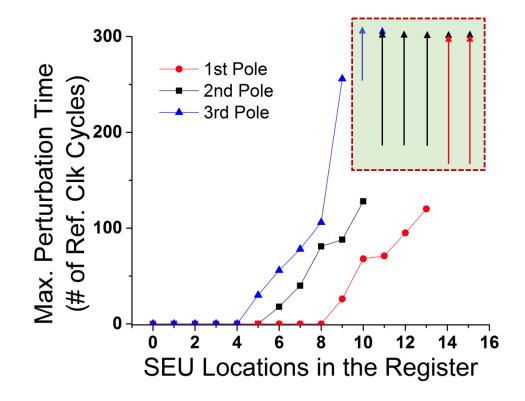

| 10 | ADPLL.                                                                                                                                                                                                                                                                                                                                                       | 77 |

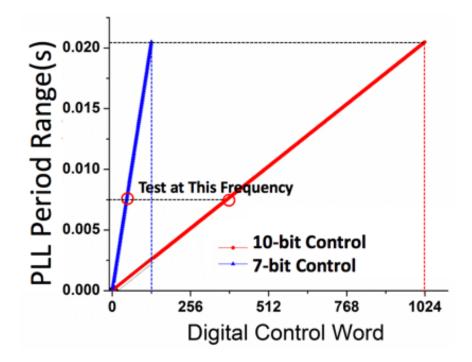

| 42 | ADPLL output period over digital control word for the analyzed design<br>topologies. Locking frequencies of the analyzed ADPLLs are marked                                                                                                                                                                                                                   |    |

| 43 | with circles in the plot                                                                                                                                                                                                                                                                                                                                     | 79 |

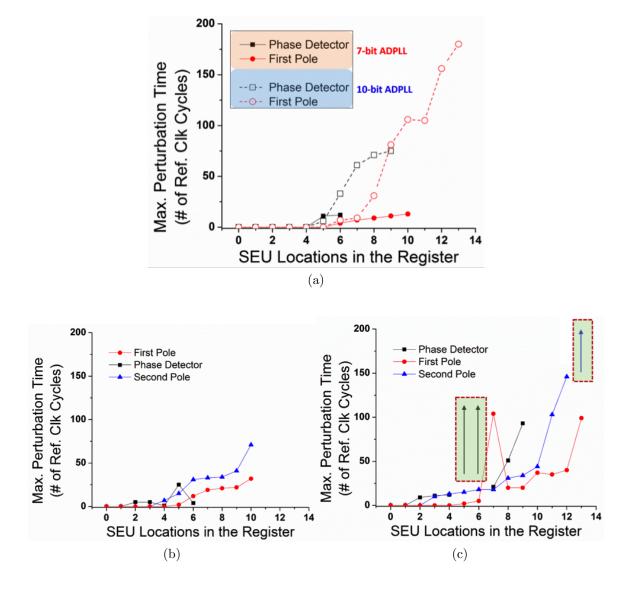

| 40 | (a) 1st-order ADPLL with 7-bit and 10-bit DCO, (b) 2nd-order linear<br>ADPLL with 7-bit DCO and (c) 2nd-order linear ADPLL with 10-bit                                                                                                                                                                                                                       |    |

|    | DCO at the same output frequency of 128 Hz                                                                                                                                                                                                                                                                                                                   | 80 |

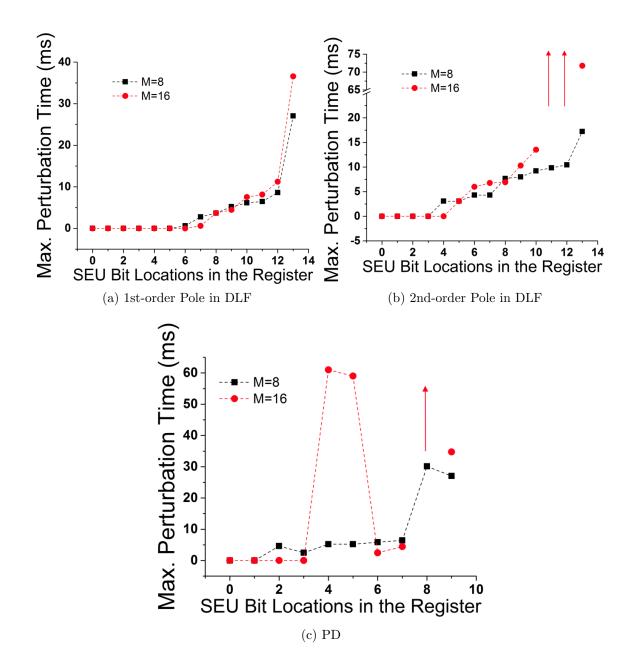

| 44 | FPGA fault injection results in terms of maximum ADPLL output                                                                                                                                                                                                                                                                                                |    |

|    | perturbation time for SEUs in different registers in (a) 1st-order pole in                                                                                                                                                                                                                                                                                   |    |

|    | the proportional path of DLF, (b) 2nd-order pole in the integral path of                                                                                                                                                                                                                                                                                     |    |

|    | DLF and (c) PD when the ADPLL is programmed to achieve frequency<br>multiplication factor (M) of 8 or 16 at the same output frequency of 104                                                                                                                                                                                                                 |    |

|    | kHz                                                                                                                                                                                                                                                                                                                                                          | 84 |

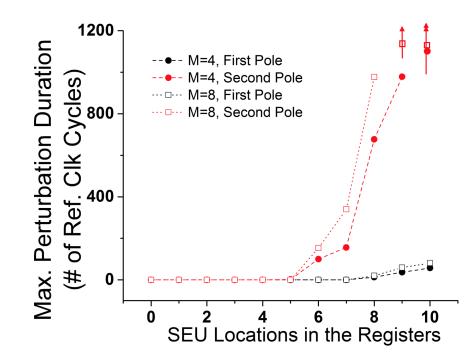

| 45 | Maximum output perturbation time over the SEU bit locations in the                                                                                                                                                                                                                                                                                           |    |

|    | 1st and 2nd-order pole in the DLF at output clock frequency of 128 kHz.                                                                                                                                                                                                                                                                                      | 86 |

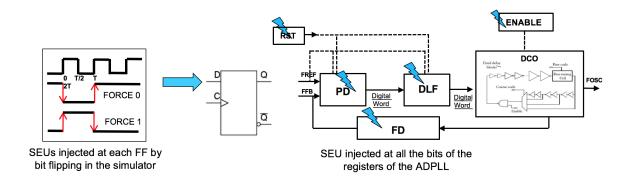

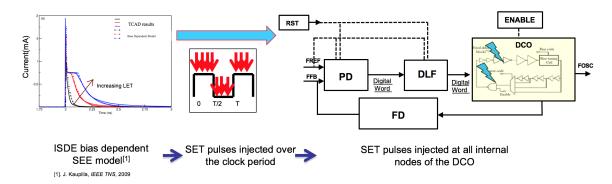

| 46 | Block diagram illustration of conducted SEU simulation on the ADPLL                                                                                                                                                                                                                                                                                          | 01 |

| 47 | implementations                                                                                                                                                                                                                                                                                                                                              | 91 |

| ті | implementations.                                                                                                                                                                                                                                                                                                                                             | 91 |

| 48 | Modular illustration of single-event-induced error signatures for each                                                                                                                                                                                                                                                                                       |    |

|    | main subcircuit of the ADPLL designs.                                                                                                                                                                                                                                                                                                                        | 93 |

| 49 | SE-induced maximum perturbation time at the output of ADPLL in                                                                                                                                                                                                                                                                                               |    |

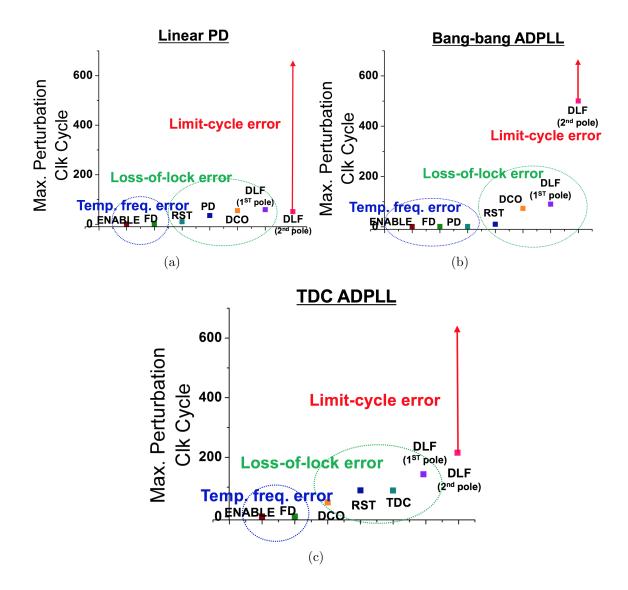

|    | terms of reference clock cycles for each module (a) linear 2nd-order ADPLL, (b) bang-bang 2nd-order ADPLL and (c) TDC 2nd-order ADPLL.                                                                                                                                                                                                                       | 94 |

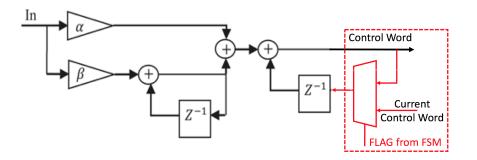

| 50 | Block diagram illustration of an ADPLL incorporating an FSM switching                                                                                                                                                                                                                                                                                        | 51 |

|    | between frequency detection mode and phase detection mode                                                                                                                                                                                                                                                                                                    | 96 |

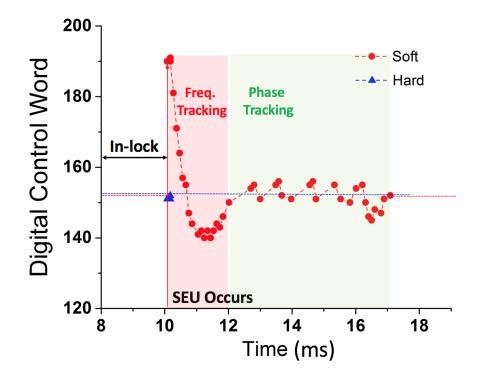

| 51 | ADPLL responses to a SEU perturbation for the flag signal in the FSM controller. The red curve indicates the ADPLL go through frequency                                                                                                                                                                                                                      |    |

|    | tracking (light pink block) and phase tracking (light green block) after                                                                                                                                                                                                                                                                                     |    |

|    | SEU perturbation in the flag signal. The blue data points are for the                                                                                                                                                                                                                                                                                        |    |

|    | modified ADPLL indicating the ADPLL stayed in lock the entire time                                                                                                                                                                                                                                                                                           | 00 |

|    | in spite of the perturbation                                                                                                                                                                                                                                                                                                                                 | 98 |

| 52 | Storing the current digital control word in the DLF in the frequency-<br>tracking path by implementing a multiplexer in the feedback path of the<br>DLF                                                                                                                                           | 99  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

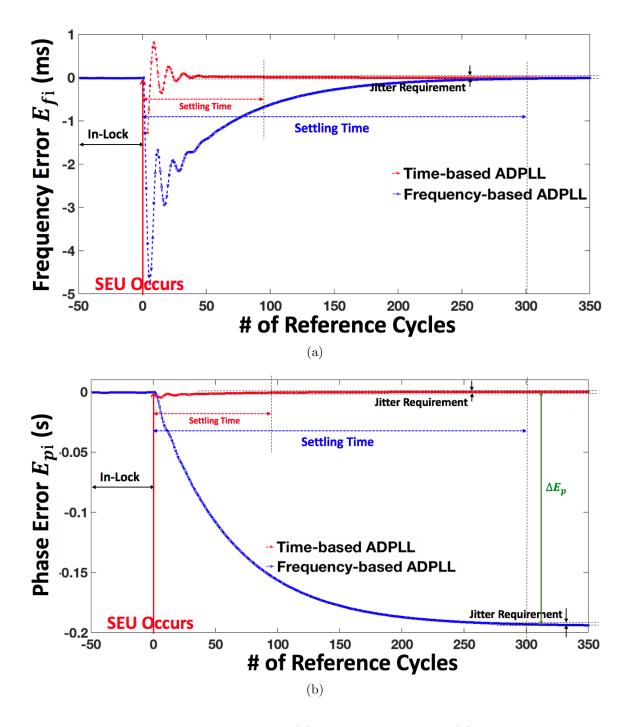

| 53 | System response in terms of (a) frequency error and (b) phase error to<br>step phase/frequency error magnitude $E_0$ over reference cycles for both<br>frequency-based and time-based ADPLLs. Settling time is defined from<br>the time of the SEU to when the system phase error settles back to |     |

|    | within jitter requirement.                                                                                                                                                                                                                                                                        | 105 |

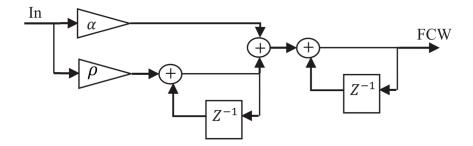

| 54 | Block diagram of a 2nd-order digital loop filter with proportional path                                                                                                                                                                                                                           |     |

|    | gain of $\alpha$ and integral path gain of $\rho$                                                                                                                                                                                                                                                 | 109 |

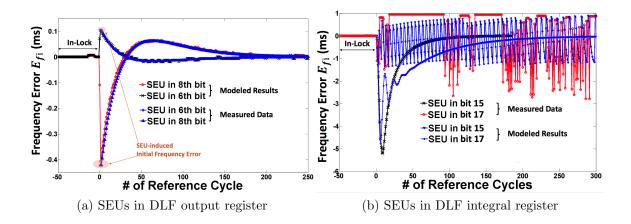

| 55 | Measured time response of frequency-based ADPLL in terms of fre-                                                                                                                                                                                                                                  |     |

|    | quency error over reference cycles towards SEUs in (a) bit 8 and bit                                                                                                                                                                                                                              |     |

|    | 6 in DLF output register and (b) bit 17 and bit 15 in DLF integral                                                                                                                                                                                                                                | 110 |

| EC | register.                                                                                                                                                                                                                                                                                         | 112 |

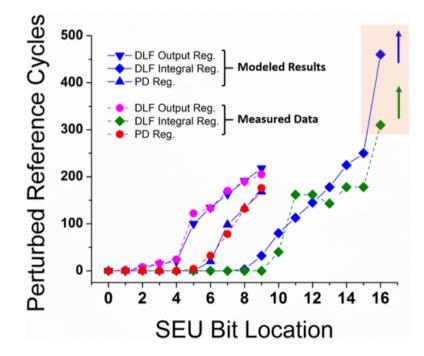

| 56 | Modeled and measured perturbation time in number of reference cycles<br>over the SEU bit location in different registers in DLF and PD for the                                                                                                                                                    |     |

|    | synthesized linear ADPLL design. Limit-cycle errors are indicated in the                                                                                                                                                                                                                          |     |

|    | shaded region, where the everlasting limit-cycle errors are indicated with                                                                                                                                                                                                                        |     |

|    | arrows pointing to infinity.                                                                                                                                                                                                                                                                      | 113 |

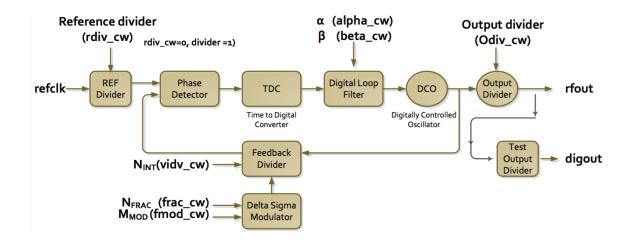

| 57 | Functionality block diagram of the 32nm SOI ADPLL under test                                                                                                                                                                                                                                      | 114 |

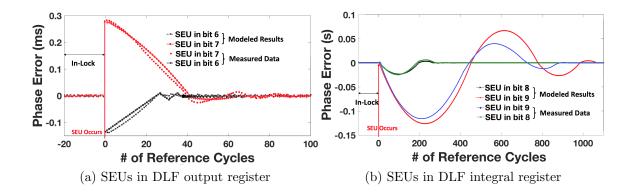

| 58 | Measured time response of bang-bang ADPLL in terms of phase error                                                                                                                                                                                                                                 |     |

|    | over reference cycles towards SEUs in (a) bit 6 and bit 7 in DLF output                                                                                                                                                                                                                           |     |

|    | register and (b) bit 8 and bit 9 in DLF integral register                                                                                                                                                                                                                                         | 116 |

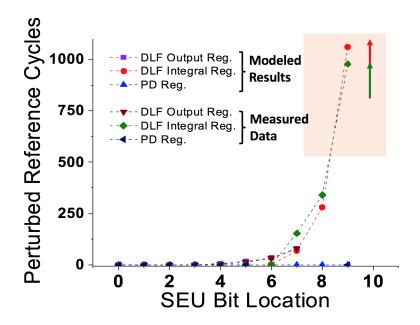

| 59 | Modeled and measured perturbation time in number of reference cycles<br>over the SEU bit location in different registers in DLF and PD for                                                                                                                                                        |     |

|    | the synthesized bang-bang ADPLL design. Limit-cycle errors are                                                                                                                                                                                                                                    |     |

|    | indicated in the shaded region, where the everlasting limit-cycle errors                                                                                                                                                                                                                          |     |

|    | are indicated with arrows pointing to infinity.                                                                                                                                                                                                                                                   | 117 |

| 60 | Schematic of harmonic-oscillation proof 3-stage DCRO [148]                                                                                                                                                                                                                                        | 123 |

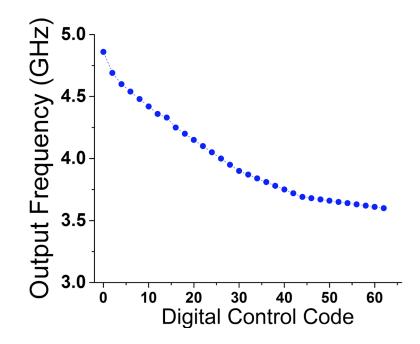

| 61 | Relationship between output frequency and digital control code showing                                                                                                                                                                                                                            |     |

|    | linearity of the designed DCRO                                                                                                                                                                                                                                                                    | 124 |

## CHAPTER I

#### INTRODUCTION

A phase-locked loop (PLL) is a closed-loop feedback system that is capable of tracking the fixed phase relationship between the phase of output and the reference clock[1]. It is widely used for clock generator or clock recovery, as a frequency synthesizer, jitter attenuator and synchronization in the fields of communications, instrumentation, control systems, and multimedia apparatus, to name just a few[2][3]. An accurate clock signal is an important guarantee of the correct functionality of a system on chip (SoC). Design flow and circuit techniques of contemporary PLL circuits are typically quite analog intensive, which usually requires usages of resistors or capacitors. This is difficult to integrate with other digital-intensive parts of the SoC such as a digital baseband (DBB) and application processors (AP) and cumbersome to port between technologies. In addition, other issues like device mismatching and voltage headrooms start to exacerbates with CMOS technology scaling and degrades the performance of conventional analog/mixed signal (A/MS) PLLs [4]. All of those mentioned issues have been pushing researchers to seek digitally-intensive alternatives to conventional analog/RF functions in the most advanced deep-submicron process to reduce cost. In recent years, all-digital phase-locked loops (ADPLLs), as the digital counterparts for conventional A/MS PLLs, are becoming favored in the deepsubmicron CMOS technologies [5] because of a variety of inherent advantages, i.e. high level of integrality and portability from technology to technology. In the past decade, ADPLLs have been applied in mobile phones, Bluetooth, and other

communication applications [6] [5].

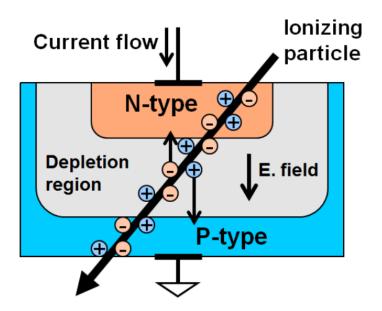

As a type of reliability issues for integrated circuits (ICs) implemented in both terrestrial and space-bound systems, a single-event effect (SEE) occurs when a highenergy ionizing particle, such as a heavy ion, passes through the circuit. If the SE ion deposits charge near a transistor, the deposited charge may potentially change the nodal voltage that is associated with that transistor leading to a single-event upset (SEU) in memory storage elements or a single-event transient (SET) in combinational logic [7]. With the scaling of technology, integrated circuits (ICs) have been reported to exhibit increased susceptibilities to SEEs due to the decreasing feature sizes and increasing operating frequencies [8].

## Objective of Research

As a potential candidate for space applications, radiation-harden-by-design (RHBD) solutions for ADPLLs are of prominent significance to preserve clock signals against SEEs.

While there are numerous studies on single-event effects in charge pump PLLs [9][10][11][12][13], little is published on radiation-effect in ADPLL based clock systems. The early endeavor can trace back to 1990s when D.J. Van Alen et. al discussed how ADPLLs-based clock system could be fault tolerant using the triple modular redundancy (TMR) technique [14]. There was a quiescent period after that for about a decade. Then in 2005, right after the ADPLLs were successfully employed in commercial communication applications, a few researchers have addressed issues related to radiation hardness of ADPLL topologies. A. N. Nemmi proposed in [15] hardening techniques of ADPLLs. But the lack of hardware results degrades the

credibility of the theory.

While there are many similarities between CPPLLs and ADPLLs, major functional modules in CPPLLs and ADPLLs are still greatly different. In this work, circuit-level simulation and experimental testing were conducted to characterize the subcircuits of different types ADPLLs to distinguish and analyze their individual contribution to the overall ADPLL SE vulnerability. Different ADPLLs with complex system architectures were also characterized and analyzed for SE vulnerability. Additionally, a novel time-domain analytical model for SEU-induced errors in ADPLLs was proposed which allows designers to distinguish the most SE sensitive modules in the ADPLL topology and apply selective hardening solutions pre-tapeout. RHBD hardening guidelines for different types of ADPLLs for different operating environment and targeted design specifications were proposed based on SE characterization and modeling of the ADPLL designs. Last but not least, the proposed model and hardening techniques are compared with existing work on A/MS PLLs to provide conventional PLL designers with insights on RHBD ADPLL designs.

### Organization of the Dissertation

The research effort presented in this dissertation is organized as follows:

Chapter II presents general background information and a detailed discussion of ADPLL topologies.

Chapter III is a chapter on the back ground information for single-event effects (SEEs) and previous work on SEEs in A/MS PLLs.

Chapter IV illustrate the SET-induced errors and SEU-induced errors in different modules in ADPLLs respectively. Chapter V details the overall SE characterization results and analysis on common ADPLL topologies.

A generalized time-domain model for SEU-induced errors for ADPLLs is proposed in Chapter VI and Chapter VII goes on by proposing RHBD design techniques for different types of ADPLLs.

Chapter VIII concludes.

## CHAPTER II

#### ALL-DIGITAL PHASE-LOCKED LOOPS (ADPLLS)

The functionality of modern integrated circuits (ICs) is highly reliant on the timing accuracy of the system clock signal. While standalone crystal or quartz oscillators are common clock sources for system clock signals from a few tens of kilohertz to hundreds of megahertz, clock signals in a frequency range higher than hundreds of megahertz are usually generated from active circuits. However, standalone active oscillators are subject to supply voltage changes and ambient temperature variations. Therefore, the active oscillator is usually put in a feedback system to allow users to have control on the oscillation frequency, which is defined as a phase locked loop (PLL).

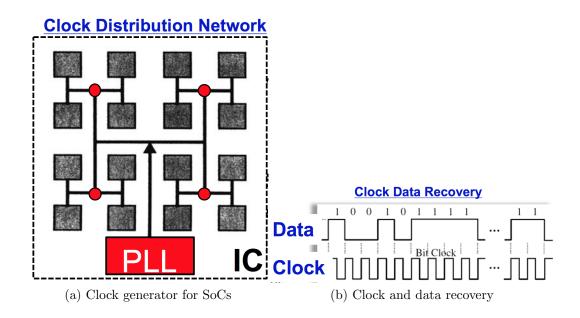

PLLs are ubiquitous in modern SoCs. As indicated in Fig. 1a, PLLs are not only the most common clock sources for modern SoCs. Depending on the complexity of the system, PLLs can also be inserted locally into the clock distribution network for local frequency multiplication or active skew cancellation. In clock and data recovery systems, as shown in Fig. 1b, PLLs are utilized for providing the clock signal at the exact frequency and phase for deciphering the correct data out of the bitstream. And PLL-based frequency synthesizers are commonly deployed as local oscillators (LOs) to perform frequency translation between baseband (BB) and radio frequency (RF) in wireless transceivers.

Depending on the circuit configuration, PLLs can be classified into analog/mixedsignal PLLs (A/MS PLLs) and all-digital PLLs (ADPLLs). Simplified block diagrams for an A/MS PLL and an ADPLL are presented in Fig. 2. What distinguishes an

Figure 1: PLL usages in (a) modern SoCs and (b) clock and data recovery systems.

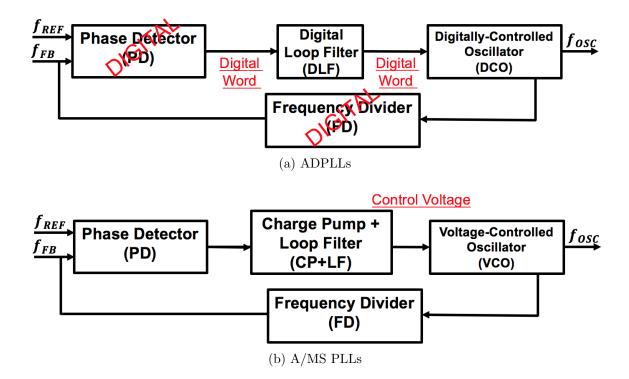

ADPLL from an A/MSPLL is that an ADPLL achieves fully digital frequency tuning instead of conventional analog voltage tuning. Conventionally, the output frequency changes linearly with the analog control voltage for a voltage-controlled oscillator (VCO). Frequency and phase tuning is achieved by adjusting analog control voltages through the A/MS control blocks in the feedback loop. In ADPLLs, the output frequency of the digitally-controlled oscillator (DCO) is usually controlled by a digital word. As shown in Fig. 2a, to accomplish "all-digital" frequency tuning, all the major subcircuits are replaced by their digital counter parts comparing to A/MS PLLs.

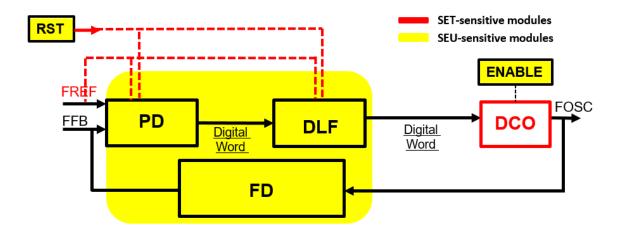

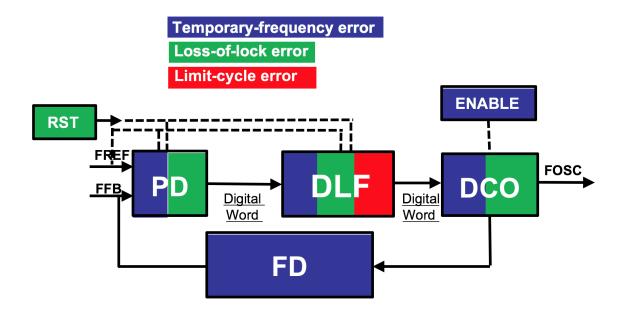

In an ADPLL, as shown in Fig. 2a, the digital phase detector (PD) compares the phase of the feedback signal  $(f_{FB})$  to the phase of a reference signal  $(f_{REF})$ , and outputs a signal representing the frequency or phase error. The digital loop filter (DLF) filters out high-frequency noises in the digital control word and sends it to a DCO to adjust the oscillation frequency  $(f_{OSC})$ . The combined process thus tracks the frequency or phase of the reference signal. Frequency multiplication is completed

Figure 2: Block diagrams for (a) ADPLLs and (b) A/MS PLLs.

through the digital frequency divider (FD) in the feedback path in the PLL.

In A/MS PLLs, as shown in Fig. 2b, despite switching from DCO to VCO, a charge pump and a loop filter is used instead of a DLF. The loop filter is a simple RC low-pass circuit, and the charge pump (CP) generates current or voltage pulses proportional to the pulse width of the PD output and integrates it onto current control voltage. Till now, most PLLs are based on the charge pump architecture [16].

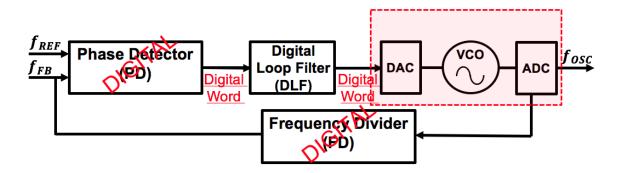

A broader definition for ADPLL includes both "all-digital" PLLs and "digitalintensive" PLLs. In "digital-intensive" PLLs, all the input and output signals for each module in the PLL are digital [4], which means the analog function can be contained inside the modules and only digital signals propagate inter-modularly. Some common topologies for "digital-intensive" PLLs include PLLs using VCOs with analog-digital converter (ADC) and digital-analog converter (DAC) wrappers [17][18][19] and PLLs using digitally-controlled LC-tank oscillators [20] [21].

Figure 3: A simplified structure of a digital-intensive ADPLL using VCOs with analog-digital converter (ADC) and digital-analog converter (DAC) wrappers.

# Basic ADPLLs

The locking characteristics and important specifications for ADPLLs are presented in the first subsection. The descriptions of each of the four modules of a basic ADPLL - namely phase detector (PD), digital loop filter (DLF), digitally-controlled oscillator (DCO) and frequency divider (FD) - are detailed in the following subsections.

# Locking Characteristics and Important Specifications

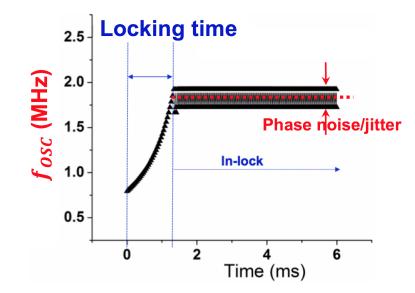

Plotted in Fig. 4 is the output frequency of a typical ADPLL over time. The ADPLL goes through initial acquisition time during which it tries to find or track the expected output frequency and eventually reaches a steady state, which is referred to as the PLL "in-lock".

#### Important Specifications

A. Locking time and loop bandwidth

Figure 4: Output frequency of a typical ADPLL during initial acquisition time and steady-state operation.

As shown in Fig. 4, this time duration (around 1.2 ms) the PLL takes to reach a steady state is referred to as the "locking time" or "acquisition time". A PLL acts as a low-pass filter with respect to the reference modulation. Essentially, high-frequency reference noise is rejected. At the same time, a PLL acts as a high-pass filter with respect to VCO noises. ?Loop bandwidth? is the modulation frequency at which the PLL begins to lose lock with the changing reference (-3dB). PLL loop bandwidth essentially corresponds to the time it takes for the loop to respond to any changes at the input [22]. In general, higher loop bandwidth is recommended if the input clock reference is clean and stable, such as crystal oscillators. A lower PLL loop bandwidth is typically recommended if the input clock is noisy and cleaning is required.

B. Phase noise and phase jitter

After the frequency and phase acquisition, the ADPLL eventually enters a steady state, which is referred to as "in-lock", as shown in Fig. 4. Phase noise and jitter

determines the quality of the PLL output clock signal when the PLL is in-lock. The phase noise is typically expressed in dBc/Hz and represents the amount of signal power at a given sideband or offset frequency from the ideal clock frequency. Phase noise is the frequency domain representation of clock noise. Phase jitter, on the other hand, is the time domain instability of the clock signal and is often expresses in picoseconds (ps) or fractions of the ideal clock period. Two types of phase jitter are commonly used - period jitter and cycle-to-cycle jitter. Period jitter is the worst-case deviation from the ideal clock period. And cycle-cycle jitter is the worst-case clock period difference between adjacent clock cycles. In this work, the term "jitter" refers to period jitter.

ADPLL implementations suffer from tradeoffs between loop bandwidth and phase noise. Essentially, fast locking time of ADPLL is achieved through narrowing the loop bandwidth by tuning the loop parameters of the DLF at the expense of enhanced phase noise and spurs[23]. In Fig. 4, the ADPLL output frequency dithers between two frequencies, which results in jitter and phase noise, as it has reached the bandwidth limitation of the design.

# C. Order and type

The order of a system refers to the highest degree of the polynomial expression in the denominator system transfer function in the phase domain. The type of a system refers to the number of poles of the open-loop transfer function located at the origin. The most commonly used A/MS PLLs are 1st-order type-I, 2nd-order type-I and 2nd-order type-II PLLs. When implementing loop filters in the digital fashion, adding a closed-loop pole is accompanied by the addition of an open-loop pole. Therefore, 1st-order type-I and 2nd-order type-II ADPLLs are commonly used.

# Locking Characteristics

The implementations of the PD and the DLF in an ADPLL dictate the loop tracking characteristics.

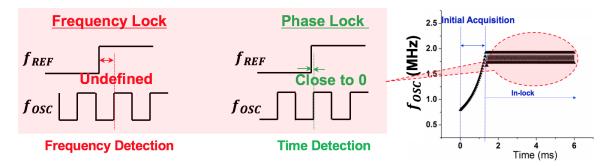

# A. PD

The PD determines whether an ADPLL is in phase-lock or frequency-lock in the steady-state. As indicated in Fig. 5, frequency-lock is referred to a state when an ADPLL is in-lock, the ADPLL outputs only the correct frequency but the timedifference between edges of the reference clock signal  $(f_{REF})$  and PLL output clock  $(f_{OSC})$  is unknown. However, in the phase-lock state, an ADPLL not only produces the desired frequency, but also aligns the clock edges of  $f_{OSC}$  and  $f_{REF}$ .

Figure 5: Time detection is needed for ADPLLs to reach phase-lock and frequency detection is needed for frequency-lock.

Phase-lock is superior to frequency-lock because of the additional edge-alignment feature. Phase-lock ADPLLs are used in clock-data-recovery systems [24] or active skew cancellation applications [25], where accurate frequency and phase are required. However, because that edge-alignment generally requires large design complexity and long settling time, frequency-lock ADPLLs are implemented in applications where the phase accuracy of the PLL output clock signal is not required, such as LOs in transceivers or high-speed clock generators.

Different detection schemes are required for frequency-lock and phase-lock. To achieve only frequency-lock in steady state, a PD deploying frequency-detection scheme, i.e. a "frequency-based" PD, is used, whereas phase-lock requires usages of time-based PDs with the time-detection schemes. Frequency detection schemes are based on frequency-counting algorithms, which are generally more efficient than time detection schemes for frequency locking.

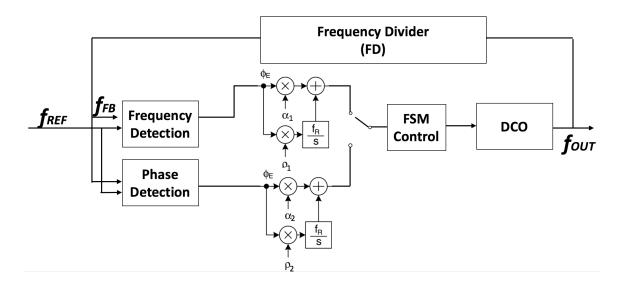

As stated above, using frequency-based PDs can drastically reduce the system settling time, but lack of phase tracking capability. While time-based PDs can perform both frequency and phase, the loop bandwidth is usually made wide meet the system phase noise requirement. To solve the conflicting requirements of the PLLs, "FSM-based PDs" were proposed to allow the loop to switch between different tracking modes with different loop bandwidths controlled by a gear-shifting FSM. Using the frequency-based PD in the frequency-tracking mode of the PLL with large loop bandwidth and the time-based PD in its phase-tracking mode with narrow loop width allows the loop to achieve locking state in an optimum timely fashion.

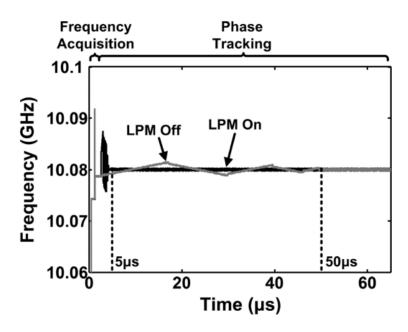

Plotted in Fig. 6 is the ADPLL output frequency over time in an example case when the ADPLL with FSM-based PD undergoes frequency and phase acquisition. The locking process monitor (LPM) is the FSM controller for mode switching in [26]. The light curve represents the case when the LPM is on, while the darkened curve indicates when the LPM is off, i.e. the loop stays in phase-locking mode the entire time. The loop bandwidth decreases from frequency acquisition mode to phase acquisition to allow for less abrupt digital control word changes during phase-tracking mode. As shown in Fig. 6, the overall locking time improves with LPM on. Sometimes, the loop bandwidth could be gear-shifted several time for the most optimal acquisition performance[4].

Figure 6: Comparison of locking behaviors with and without the aid of locking process monitor (LPM) [26].

# B. DLF

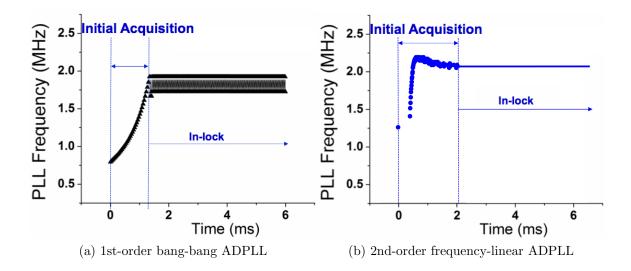

The DLF in an ADPLL determines the order of the system. Plotted in Fig. 7 are examples of two simulated ADPLL designs undergoing initial acquisition at startup and eventually settling in locking state. Essentially, this is a plot demonstrating the system input frequency step response [22]. In Fig. 7a, the 1st-order bang-bang ADPLL exhibit linear 1st-order system behaviour during initial phase and frequency acquisition. In Fig. 7b, the output frequency of the 2nd-order frequency-linear ADPLL overshoots the input frequency during acquisition, which corresponds to a underdamped 2nd-order system behaviour ( $\zeta < 1$ ).

Figure 7: Simulation results on loop locking characteristics for (a) a 1st-order bang-bang ADPLL and (b) a 2nd-order frequency-linear ADPLL on IBM 180 SOI technology.

#### Phase Detector (PD)

A phase detector (PD) is an indispensable element of the ADPLL. The PD generates a digital word representing the difference in phase or frequency between two input signals. PDs can be categorized into three basic categories based on how the errors are detected - frequency-based PD, time-based PD, and FSM-based PD.

## A. Frequency-based PD

Frequency-based PD detects the frequency error between the current and the expected output period. They are sometimes termed frequency detectors. This term is not used in this dissertation to avoid the confusion between frequency detectors and frequency dividers. A PLL uses a frequency-based PD locks on the frequency rather than phase, i.e. small phase offset exists between the output signal and the reference clock signal. This type of PD is used in wireless applications such as a local oscillator (LO)[4] or clock generator for Globally-Asynchronous Locally Synchronous

(GALS) architectures [27], where there is no need to align the clock phase.

If we define the period of the oscillator output as  $T_{OSC}$  and the the reference clock period as  $T_{REF}$ . It is convenient in practice to normalize the transition timestamps in terms of actual  $T_{OSC}$  since it is easy to observe and operate on actual oscillator output clock events. The clock "phase" for the oscillator clock at timestamp t can be defined as:

$$\theta_{OSC} = \frac{t}{T_{OSC}} \tag{1}$$

The "phase" of the oscillator output clock could be estimated as M by accumulating the number of significant (rising or falling) edge transitions over a reference clock cycle. The frequency error at that reference clock cycle can be calculated by comparing the actual (M) and expected number (N) of output clock cycles ( $T_{OSC}$ ) in one reference cycle ( $T_{REF}$ ).

One straightforward implementation outputs the direct difference between the actual (M) and expected number (N) of output clock cycles in one reference cycle, i.e. N-M [28]. This configuration is referred to as "integer-based frequency PD" in the following text. The other, more complicated, configuration of PD is referred to as "fraction-based frequency PD" in the following text. The phase error  $E_f$  is given by

$$E_f = \frac{T_{REF}}{N} - \frac{T_{REF}}{M}.$$

(2)

For a common implementation of DCO, where the digital control word is linearly proportional to the output period, the adjustment needed for the control word is given by

$$\frac{D}{N} - \frac{D}{M},\tag{3}$$

where D is the digital control word corresponding to the desired output frequency [4]. For different applications, D may vary within the pull-in frequency range of the ADPLL.  $D_{center}$ , the control word that corresponds to the center frequency, is chosen in replacement of D for simplicity of design implementation. Therefore, the output of the PD is shown in

$$\frac{D_{center}}{N} - \frac{D_{center}}{M},\tag{4}$$

ADPLLs with integer-based frequency PD suffer from limited frequency pull-in range due to the asymmetry between the positive and negative frequency tuning steps when N is fixed. While fraction-based frequency PD operates more linearly in frequency domain comparing with integer-based frequency PD, they could be referred to as integer-based linear PD and fraction-based linear PD comparing to non-linear PDs, such as bang-bang PDs described in the following section. Other frequencybased PDs are uses advanced algorithms, including binary-search algorithm [29][30] and frequency estimation algorithm[31], which are not discussed in the scope of this work.

#### B. Time-based PD

Time-based PD detects the phase error between the feedback and the reference clock signal based on the relative clock edge locations of the two signals. Comparing to a PLL with a frequency-based PD, a PLL with a time-based PD not only locks onto the correct frequency but also aligns the clock edges of the output clock signal with the reference clock signal, i.e. phase offset between two clock edges is close to zero. Even though phase-lock is superior to frequency-lock, phase alignment generally takes a longer time than locking onto the correct frequency. This type of PD is required in clock and data recovery systems[], because inaccuracies in the phase of the clock signal can introduce extra delay and possibly cause bit offset when interpreting the data stream.

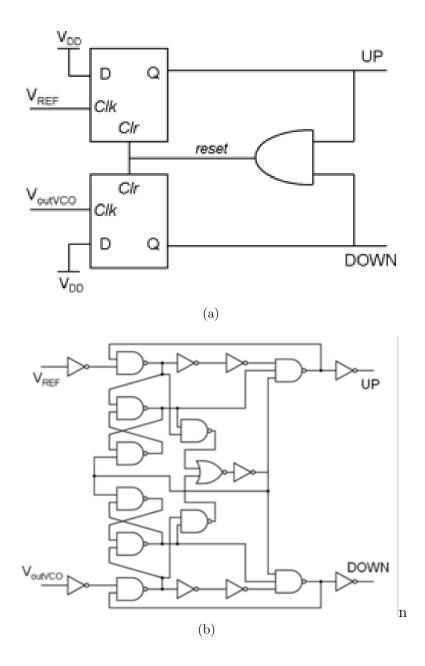

#### B.1 Bang-bang PD

A bang-bang PD is one of the most commonly used time-based PDs due to its simplicity in circuit design[32]. Different types of bang-bang (also called single-bit or lead-lag) PDs are used in bang-bang ADPLLs as well as CPPLLs. As shown in Fig. 8a and Fig. 8b, bang-bang PDs generally contain one or more D-flip-flops. Depending on whether the clock edge of the feedback signal ( $f_{FB}$ ) is leading or lagging that of the reference signal ( $f_{REF}$ )), a '0' or '1' is generated for both up or down signals indicating an increase or a decrease on current digital control word.

The nonlinearity resulted from single-bit resolution can be responsible for huge undesirable spurs and noise at the PLL output. In addition, this nonlinearity contributes to the nonlinear frequency tracking behavior of the loop.

B.2 Time-to-Digital Converter (TDC)

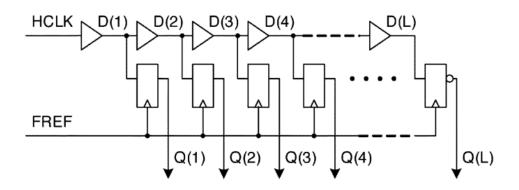

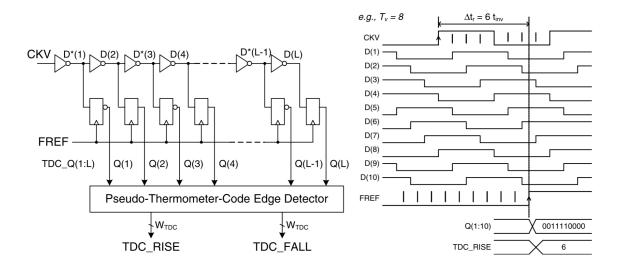

Another type of time-based PD is a time-to-digital converter (TDC). A TDC takes the time difference between the reference clock signal and the feedback clock signal (i.e. the accumulated phase error between the two signals) and directly converts that to a multi-bit digital word. As depicted in Fig. 9, the feedback clock signal HCLK passes through a string of non-inverting delay elements, such as buffers. An array of flip-flops sample the delayed clock vector D(1:L) on the rising edge of the reference clock FREF and output pseudo-thermometer-coded output Q(1:L)

Figure 8: Different digital implementation of bang-bang PDs [33].

containing information on the timing separation between the rising edge of FREF and the rising and falling edges of FFB. The pseudo-thermometer coded output could be converted to binary that measures the HCLK-to-FREF delay in units of a buffer delay or the pulse width of HCLK. Hence, a TDC outputs a digital word DW that satisfies Eqn. 5

$$E_p = DW \cdot \Delta_{TDC},\tag{5}$$

in which  $E_p$  is the phase error between the two signals and  $\Delta_{TDC}$  is the resolution of the TDC, i.e. the inverter delay in Fig. 9.

Figure 9: A simplified structure of TDC core [34].

Several variations of TDC implementations are commonly used, including delayline-based [35] TDCs and gated-ring-oscillator-based [36] TDCs. TDCs can also be cascaded after a bang-bang PD to facilitate in converting a single-bit UP/DOWN pulse to a multi-bit digital word based on the time duration of the UP/DOWN pulses[37][38], as indicated in Fig. 10. However, the structural differences of the TDCs have minimal impacts on the circuit behavior. Eqn. 5 holds true for all TDC design implementations. Since, the TDC output is linearly proportional to the detected phase error, a PLL using a TDC is able to reach locking state faster comparing to ones using bang-bang PDs only.

Figure 10: PFD: (a) block diagram and (b) its transfer function [37].

#### C. FSM-based PD

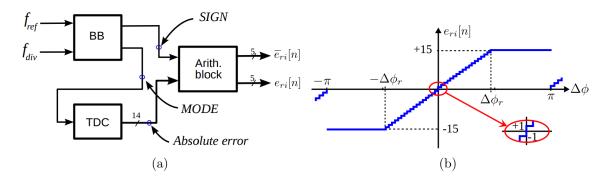

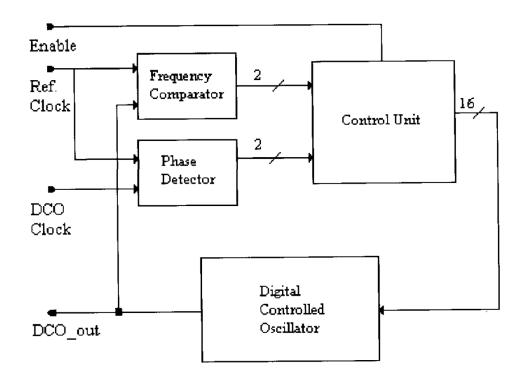

As shown in Fig. 11, at the beginning of operating, this ADPLL is in the frequency acquisition mode utilizing the frequency-based PD only. After frequency acquisition is completed, the ADPLL enters the phase-acquisition mode. The ADPLL increments or decrements the DCO control word based on the output of the time-based PD.

Recently, TDCs are also used as FSM-based PDs, as TDCs can perform both frequency detection and phase detection. As shown in Fig. 12, the DCO clock (CKV) through a chain of inverters such that each inverter output would produce a clock slightly delayed from that of the previous inverter [5]. The staggered clock phases are then sampled by the same reference clock. By detecting the transitions from '1' to '0' and from '0' to '1', the rising edge and falling edge of the DCO clock are detected, based on which half-period of the DCO clock can be calculated in terms of inverter

Figure 11: A block diagram of an ADPLL using frequency-based PD (i.e. frequency comparator in the figure) and time-based PD (i.e. phase detector in the figure) [39].

delays. Therefore, frequency tracking can be conducted based on the difference between current digital word and anticipated digital word for the half-period. As used in the time-detection mode, the TDC detects the time difference between the reference edge and the following rising edge of CKV. With that information, phasetracking can be performed.

The above three categories of PDs are classified based on their phase detecting mechanisms. PDs can also be categorized based on the linearity of the operation of the PD in frequency or phase domain, and the corresponding ADPLL s can be classified into linear and non-linear ADPLLs. Intuitively, frequency-based PDs are frequency-linear PDs due to their operation linearity in frequency domain. TDCs are phase-linear PDs because TDCs output a digital word that linearly proportional to

Figure 12: Time-to-digital converter serves as a "FSM-based PD" [5].

the incoming accumulated phase error. And finally, bang-bang PDs are non-linear PDs.

# Digital Loop Filter (DLF)

The digital loop filter (DLF) is the core digital control unit for an ADPLL, which is analogous to the combination of the charge pump and the loop filter in analog/mixedsignal PLL [4]. The purpose of the DLF is two-fold - integrating the PD output on to the current digital control word and keeping the locking control word as steady as possible, i.e. filtering out fluctuations when PLL is in-lock.

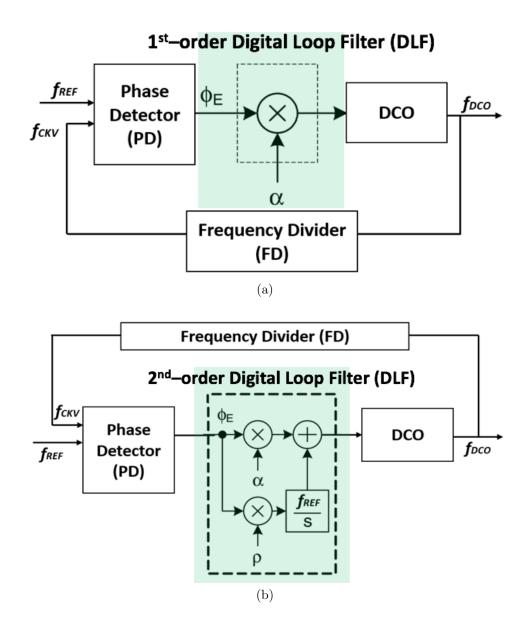

Integrating of digital words in performed through an integrator, which corresponds to a pole in the DLF. An ADPLL with a 1st-order DLF (containing only one digital word integrator with proportional gain of  $\alpha$ ) is referred to as a 1st-order ADPLL. 1st-order ADPLLs generally feature fast dynamics and are used where fast frequency/phase acquisition is required, such as direct transmit modulation[40].

1st-order loops react fast to incoming digital word changes and their filtering

capability is low. An extra integrator, i.e. an extra pole, with integral gain of  $\rho$ , can be added to the DLF for filtering purposes, as shown in Fig. 13b. Together with the proportional path, this forms a 2nd-order proportional and integral (PI) filter. Similarly, an ADPLL with a 2nd-order DLF is referred to as a 2nd-order ADPLL. A chief advantage of 2nd-order loop is that the steady-state phase error goes to zero for a step frequency change, while the phase error in a 1st-order PLL loop is proportional to the frequency offset. Therefore, 2nd-order ADPLLs are commonly used as frequency synthesizers [4] to allow rapid frequency hoping without any residual phase errors. In addition, 2nd-order loop has better filtering capabilities of oscillator noise, leading to improvements in the overall phase-noise performance, comparing with 1st-order loops. As such, this topology is often used in applications with stringent phase noise requirements [41][42][43][44] [45].

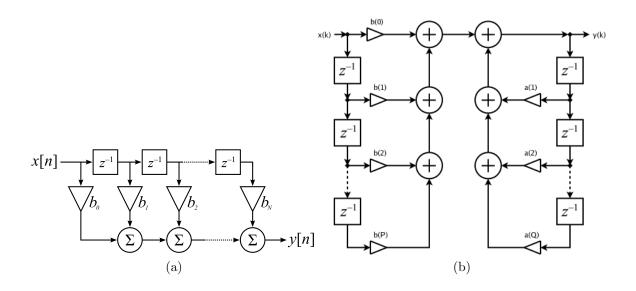

To give rise to 2nd-order DLF configuration and provide even more filtering for incoming word changes, DLF could be constructed as a combination of finite impulse response (FIR) and infinite impulse response (IIR) filters cascaded with the PI filter. Fig. 14 demonstrates the basic architectures of an FIR filter and an IIR filter. The operation of an FIR filter of order N (as shown in Fig. 14a) is illustrated in Eqn. 6

$$y[n] = b_0 x[n] + b_1 x[n-1] + \dots + b_N x[n-N],$$

(6)

where x[n] is the input signal, y[n] is the output signal and  $b_i$  is the value of the impulse response at the corresponding  $i^{th}$  instant (i=0,1,2...,N). FIR filters only have feedforward paths. IIR filters corresponding to Fig. 14b are often described as Eqn. 7

Figure 13: Block diagram of a typical (a) 1st-order ADPLL and (b) 2nd-order ADPLL with 2nd-order DLF.

$$y[n] = \frac{1}{a_0} (b_0 x[n] + b_1 x[n-1] + \dots + b_P x[n-P]) - a_1 y[n-1] - a_2 y[n-2] + \dots + a_Q y[n-Q],$$

(7)

where P, Q are the filter order of feed forward and feedback, respectively.  $b_i$  are feed forward filter coefficients and  $a_i$  are feedback filter coefficients.

Figure 14: Basic architectures of (a) an FIR filter [46] and (b) an IIR filter [47].

Therefore, the transfer functions for the FIR filter above are given in Eqn. 8,

$$H(z)_{FIR} = \sum_{i=0}^{N} b_i z^{-i},$$

(8)

in which all the poles are located at origins so that FIR filters are unconditionally stable. Similarly, the transfer function for the IIR filter is shown in Eqn. 9

$$H(z)_{IIR} = \frac{\sum_{i=0}^{P} b_i z^{-i}}{\sum_{j=0}^{Q} a_j z^{-j}}.$$

(9)

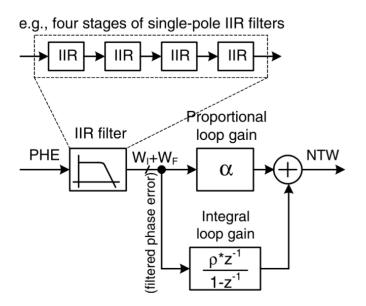

IIR filters could easily become unstable due to the complex pole-zero relationship in the transfer function. However, IIR filters are usually more compact and provide stronger filtering capabilities. This problem is usually solved by using a cascade of single-pole IIR filters, which are unconditionally stable, as shown in Fig. 15. The cascaded IIR filter attenuates the noises from reference signal and the digital PD at (20·n)-dB/dec slope, in which n is the number of poles introduced by the IIR filter [4][48].

Figure 15: Block diagram DLF consists of cascaded single-pole IIR filters and PI filters in an ADPLL [4].

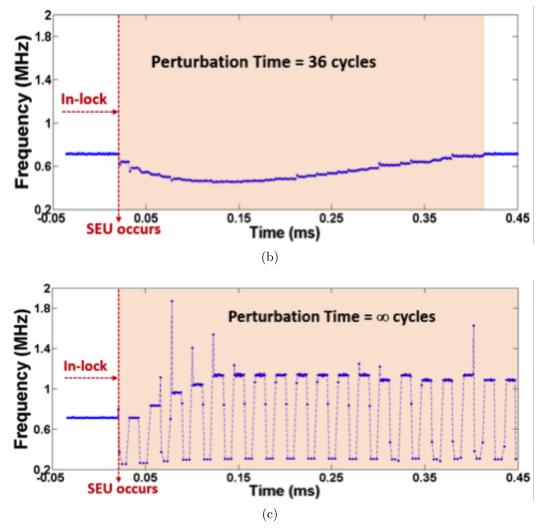

## Digitally-Controlled Oscillator (DCO)

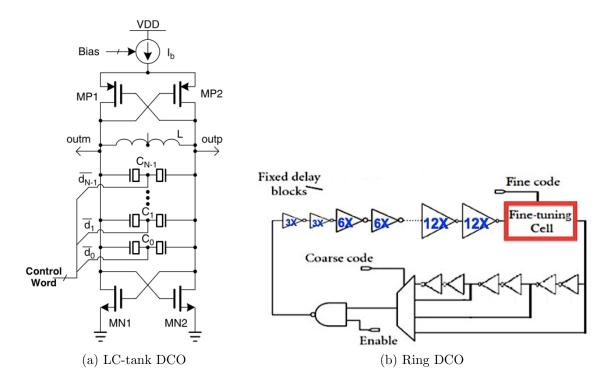

The design of digital controlled oscillators (DCOs) can be derived from the design of voltage-controlled oscillator (VCO). Two common topologies of DCOs are LC-tankbased and ring-based DCOs. The LC-tank oscillator is based on resonance between L and C components in the circuit. As shown in Fig. 16a, the oscillating frequency is controlled by using control words to control how much capacitance from the varactor bank is resonating with the inductor during operation. On the other hand, in Fig. 16b, the ring-based is based on the resonance of odd number of inverting gates tied in a loop fashion. The frequency of oscillation is manipulated by either adjusting the number of inverting gates in the ring or the delay of each inverting gates through the control word. Limited by the phase-noise and jitter performance of pure digital oscillator, i.e. ring oscillator, LC-tank resonance based ADPLL are more commonly used in communication applications[49]. As stated previously, in this case, an ADPLL is really a digital-intensive PLL. For the purpose of this work, we use ring-oscillatorbased ADPLL as an example to characterize the single-event sensitivity of ADPLLs. However, the conclusion of the work could be extended to LC-tank-based digitalintensive PLLs.

Figure 16: Different DCO structures: (a) LC-tank based DCO [4] (b) Ring-based DCO [50].

#### Frequency Divider (FD)

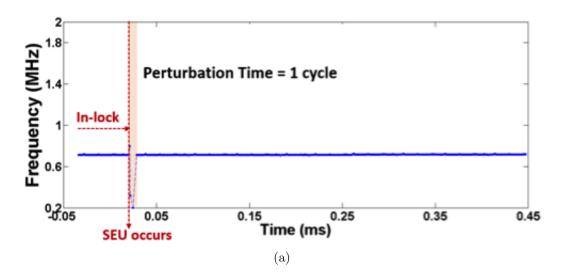

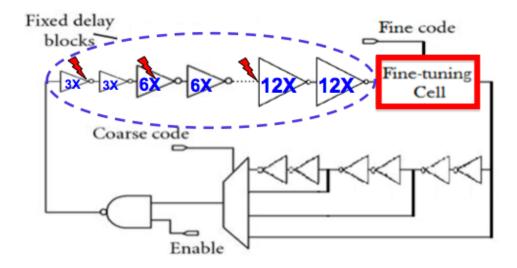

A frequency divider (FD) is commonly used in the feedback path to accomplish frequency multiplication at the output of the ADPLL. In an ADPLL with an integer-N FD, the PLL generates an output clock signal at an integer multiple of the reference frequency ( $f_{PLL} = N f_{REF}$ ), while in an ADPLL with an fraction-N FD, the output frequency can increment by fractions of the reference frequency.